Fターム[4M119CC02]の内容

MRAM・スピンメモリ技術 (17,699) | 磁化制御技術 (1,406) | 磁界による磁化制御 (394) | 磁界発生電流線による磁化制御 (371)

Fターム[4M119CC02]の下位に属するFターム

回路、タイミングによるもの (44)

Fターム[4M119CC02]に分類される特許

21 - 40 / 327

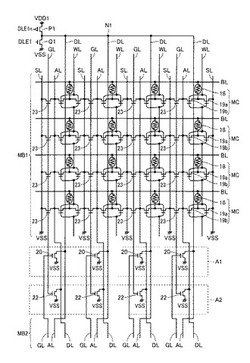

半導体記憶装置

【課題】半導体基板の表面の空き領域が少ない半導体記憶装置を提供する。

【解決手段】このMRAMの各メモリセルMCは、磁気抵抗素子18と2つのアクセストランジスタ19a,19bを含み、トランジスタ19a,19bのドレインを磁気抵抗素子18を介して対応のビット線BLに接続し、それらのゲートを対応のワード線WLに接続し、それらのソースをそれぞれソース線SLおよび補助配線ALに接続する。したがって、アクセストランジスタ19bのソースとDLドライバ14に含まれるドライバトランジスタ23のソースとを共通化することができ、シリコン基板31の表面の空き領域を減らすことができる。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ、磁気記録再生装置、メモリセルアレイ、及び磁気抵抗効果素子の製造方法

【課題】 本発明の実施形態によれば、劣化しにくく、MR変化率の大きい磁気抵抗効果素子、それを用いた磁気ヘッドアセンブリ、磁気記録再生装置、メモリセルアレイ、及び磁気抵抗効果素子の製造方法を提供することができる。

【解決手段】 磁気抵抗効果素子は、第1の電極と、第1の磁性層と、第2の磁性層と、スペーサ層と、Zn、In、Sn、及びCdから選択される少なくとも一つの元素とFe、Co、及びNiから選択される少なくとも一つの元素とを含む酸化物層と、酸化物層に接して設けられ、Zn、In、Sn、及びCdから選択される少なくとも一つの元素を0.5at%以上80at%以下の濃度で含み、かつFe、Co、及びNiから選択される少なくとも一つの元素を含む金属層とを備える。

(もっと読む)

動力発生装置、音響再生装置、インジェクション装置、位置制御装置、光スイッチング装置

【課題】電磁力利用の動力発生装置に関し低消費電力化・部品点数の削減を図る。

【解決手段】例えばMTJ素子(磁気トンネル接合素子)などの磁気メモリ素子を利用した動力発生装置とする。磁気メモリ素子は磁化状態が平行状態のときに漏洩磁界が生じるため、当該漏洩磁界を永久磁石に作用させて動力を発生する。動力の発生は磁気メモリ素子に値を書き込むことで可能となるため、駆動信号としては符号”0””1”の組み合わせで成るデジタル信号を用いることができる。これによりD/Aコンバータを不要とでき部品点数の削減が図られる。また磁気メモリ素子は一度電流を流して値を書き込めば平行状態/反平行状態を維持するものであり、従って動力を継続して得るにあたり電力を与え続ける必要性はなく、この面で低消費電力化が図られる。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録装置

【課題】MR変化率を高くすることができる磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録装置を提供する。

【解決手段】実施形態に係る磁気抵抗効果素子は、積層体と、前記積層体の積層方向に電流を流すための一対の電極と、を備える。前記積層体は、第1の磁性層と、第2の磁性層と、前記第1の磁性層と前記第2の磁性層との間に配置されたスペーサ層と、を有する。そして、前記第1の磁性層、前記第2の磁性層及び前記スペーサ層の少なくとも1つの層が金属酸化物からなる酸化物層を含み、前記金属酸化物の結晶構造は、NaCl構造である。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置

【課題】 十分なMR変化率を有する磁気抵抗効果素子及びその製造方法を提供する。

【解決手段】 本発明の磁気抵抗効果素子は、第1の磁性層14と、第2の磁性層18と、第1の磁性層14と第2の磁性層18との間に設けられたスペーサ層16とを備えた積層体と、積層体の膜面に垂直に電流を流すための一対の電極11、20とを有し、スペーサ層16が、Zn、In、Sn、Cdから選択される少なくとも1つの元素及びFe、Co、Niから選択される少なくとも1つの元素を含む酸化物層21を含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】孤立パターンに銅の化合物が析出するのを抑制する半導体装置の製造方法と、半導体装置とを提供する。

【解決手段】半導体装置では、素子・基板層ESLの低誘電率膜LOW1、ファイン層FLの極低誘電率膜ELK1等およびセミグローバル層SGLの低誘電率膜LOW2等のそれぞれの開口部に形成されるアライメントマークAMおよび重ね合わせ検査マークKMが、半導体基板SUBに形成された所定の導電型の不純物領域IRに電気的に接続されて、アライメントマークAMおよび重ね合わせ検査マークKMが接地電位に固定されている。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

低電力磁気ランダムアクセスメモリセル

【課題】 低電力磁気ランダムアクセスメモリセルを提供する。

【解決手段】 本発明は、熱アシスト書き込み操作又はスピントルクトランスファー(STT)に基づいた書き込み操作を実施するのに適した磁気ランダムアクセスメモリ(MRAM)セルに関する。このMRAMは、磁気トンネル接合を備える。磁気トンネル接合が、上部電極と、第1磁化方向を有する第1強磁性層と第1磁化方向に対して調節可能な第2磁化方向を有する第2強磁性層との間に形成されたトンネル障壁層と、前端層と、第2強磁性層が上に堆積された磁性層又は金属層とから構成される。第2強磁性層が、前端層とトンネル障壁層との間に形成されていて、約0.5nm〜約2nmの厚さを有する。その結果、当該磁気トンネル接合は、約100%より大きい磁気抵抗を有する。本明細書で開示するMRAMセルは、従来のMRAMセルに比べて電力消費が低い。

(もっと読む)

磁気抵抗素子および磁気抵抗素子の製造方法

【課題】従来のTMR素子に比べて磁気抵抗を大きくし、出力電圧を大きくすることを目的とする。

【解決手段】磁気抵抗素子は、基板と、前記基板上に形成されたCo,Fe,Bを含む磁性合金からなる強磁性体層と、前記強磁性体層上にトンネル障壁層として(001)結晶面が優先配向した多結晶酸化マグネシウム層と、を有し、前記強磁性体層が結晶化していることに特徴がある。

(もっと読む)

スピン伝導素子

【課題】 Hanle効果を利用可能なスピン伝導素子を提供する。

【解決手段】 電子流源Eにより、第1強磁性層1と第1電極4との間に電子流が供給されると、半導体層3内を電子が流れると共に、スピンが拡散する。このスピン流は、第2強磁性層2方向にも流れ、スピンの磁化方向に依存して、第2強磁性層2内に吸収される。スピン伝導素子における第1配線8aに電流を供給すると、その周囲に磁場Bが発生するが、半導体層3Cをスピンが走行する領域内において、磁場Bが印加されると、磁場Bの影響を受けて、スピンの方向が変わる。したがって、この磁場Bを制御することで、第2強磁性層2内に吸収されるスピン量を制御することができる。

(もっと読む)

磁気トンネル接合素子、その製造方法、及びMRAM

【課題】 積層構造の側方に生成された付着物の影響を受けにくい磁気トンネル接合素子が求められている。

【解決手段】 基板上に形成された下部電極の一部の領域の上に、下部電極とはエッチング特性が異なる導電材料で形成されたバッファ層が配置されている。バッファ層の上に、アモルファスの強磁性材料で形成された第1磁化自由層が配置されている。第1磁化自由層の上に、結晶化した強磁性材料で形成された第2磁化自由層が配置されている。第2磁化自由層の上にトンネルバリア層が配置されている。トンネルバリア層の上に、磁化方向が固定された磁化固定層が配置されている。磁化固定層の上に上部電極層が配置されている。

(もっと読む)

集積磁気薄膜増強回路素子を有する磁気抵抗ランダムアクセスメモリ(MRAM)

読み出しマージンが改良されたマルチビット磁気ランダムアクセスメモリセル

【課題】読み出しマージンが改良されたマルチビット磁気ランダムアクセスメモリセルを提供する。

【解決手段】第1の磁化方向を有する第1の磁性層21と第2の磁化方向を有する第2の磁性層23との間にトンネル障壁層22を備える磁気ランダムアクセスメモリ(MRAM)セルであって、第2の磁化方向が、第1の磁化方向に対して第1の方向から第2の方向に調節可能であり、前記磁気トンネル接合がさらに電気的に接続されるスイッチング抵抗素子62を備え、スイッチング抵抗素子を通してスイッチング電流が流されるときに第1のスイッチング抵抗レベルから第2のスイッチング抵抗レベルに切り換えることができるスイッチング抵抗を有し、それにより、MRAMセルのMRAMセル抵抗が、接合抵抗及びスイッチング抵抗の抵抗レベルに応じて少なくとも4つの異なるセル抵抗レベルを有することができる磁気ランダムアクセスメモリ(MRAM)セル。

(もっと読む)

メモリセルおよび方法

【課題】マルチビット磁気ランダムアクセスメモリセルの不揮発性メモリセルのための装置およびプログラム方法を提供する。

【解決手段】第1の磁気トンネル接合(MTJ)192は、磁気フィルタ208を有する第2のMTJ192に隣接する。第2のMTJ192がプログラムされることを防ぐために第1の磁束212を磁気フィルタ208が吸収しつつ、第1の磁束212を用いて第1のMTJ192が第1の論理状態にプログラムされる。

(もっと読む)

半導体装置

【課題】磁気抵抗素子を有する半導体装置であって、フリー層に所望の磁化方向と反対方向の磁界の成分が印加されることによる誤動作を抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板の主表面上に位置する、磁化自由層を有する磁気抵抗素子TMRと、磁気抵抗素子TMRの下方に位置し、第1方向に向けて延び、発生する磁界により磁化自由層の磁化状態を変化させることが可能な第1配線DLと、磁気抵抗素子TMRの上方に位置し、第2方向に向けて延び、発生する磁界により磁化自由層の磁化状態を変化させることが可能な第2配線BLとを備えている。磁化自由層は、第2方向に対して対称であり、平面視における第2方向に垂直な方向に対して非対称である。上記第1配線DLは、磁化自由層と平面視において重なる領域において、磁化自由層が磁化されやすい方向に延びる磁化容易軸の延在する方向Heに沿うように延在している。

(もっと読む)

メモリ装置およびその動作方法

【課題】磁気メモリセルへのデータの書込みを改善する。

【解決手段】スピントルクトランスファランダムアクセスメモリ(STRAM)メモリセルのような磁気メモリセルへデータを書込むための方法および装置。さまざまな実施形態に従えば、書込電流が選択された磁気メモリセルに印加されて、選択されたセルの所望の磁化状態への磁気歳差運動を開始する。フィールドアシスト電流が隣接メモリセルに同時に流されて、所望の磁化状態への選択されたセルの歳差を助ける磁場を生成する。

(もっと読む)

磁気抵抗素子、半導体メモリおよび磁気抵抗素子の製造方法

【課題】 エッチング時間を長くすることなく、トンネル絶縁膜の汚染を防止し、磁気抵抗素子の電気的特性の悪化を防止する。

【解決手段】 磁気抵抗素子は、半導体基板上に配置される固定層と、固定層上に配置されるトンネル絶縁膜と、トンネル絶縁膜上に配置され、Feを含む第1自由層と、第1自由層上に配置され、FeおよびTaを含む第2自由層と、第2自由層上に配置され、Ruを含むストッパー層とストッパー層上に配置されるハードマスクとを有している。第1自由層とストッパー層との間隔を第2自由層により大きくできるため、ストッパー層のRuがトンネル絶縁膜に付着することを防止でき、ストッパー層のRuが第1自由層の界面に現れることを防止できる。この結果、エッチング時間を長くすることなく、トンネル絶縁膜の汚染を防止でき、磁気抵抗素子の電気的特性の悪化を防止できる。

(もっと読む)

面外磁気トンネル接合セルの強磁性自由層の磁化方向を切換える方法、磁気メモリシステムおよびデータを電子的に記憶する方法

【課題】関連の強磁性層の磁気異方性(すなわち、磁化方向)をウェハ面に垂直にまたは「面外に」位置合わせさせた、しばしば磁気トンネル接合セルと称される磁気スピントルクメモリセル、およびそれらを利用する方法を提供する。

【解決手段】面外磁気トンネル接合セルの強磁性自由層の磁化方向を切換える方法であって、ACスイッチング電流を上記面外磁気トンネル接合セルに通すステップを含む。ACスイッチング電流は、上記強磁性自由層の磁化方向を切換える。

(もっと読む)

メモリセル、およびメモリセルを動作させる方法

【課題】独立してプログラム可能な自由層ドメインを有するように構成されたマルチビット不揮発性メモリセルを提供する。

【解決手段】マルチビット磁気ランダムアクセスメモリセルなどの不揮発性メモリセルについての装置および関連の方法が提供される。さまざまな実施例に従えば、磁気トンネル接合(MTJ)は、予め定められた磁化に各々が独立してプログラム可能な複数の磁気ドメインを有する強磁性自由層を含む。そして、これらの磁化は、MTJの異なる論理状態として読出され得る。

(もっと読む)

マルチレベル磁気素子

【課題】 マルチレベル磁気素子を提供する。

【解決手段】 本発明は、自由に整列させることができる磁化を有する軟強磁性層と、第1の高温しきい値では固定され、第1の低温しきい値では自由に整列可能な磁化を有する第1の硬強磁性層との間に第1のトンネル障壁層を備えるマルチレベル磁気素子に関する。磁気素子は、第2のトンネル障壁層と、第2の高温しきい値では固定され、第1の低温しきい値では自由に整列可能な磁化を有する第2の硬強磁性層とをさらに備え、軟強磁性層が第1のトンネル障壁層と第2のトンネル障壁層の間に備えられる。本明細書で開示される磁気素子は、ただ1本の電流線のみを使用して4つの異なるレベルを書き込むことができるようにする。

(もっと読む)

21 - 40 / 327

[ Back to top ]