Fターム[4M119DD42]の内容

MRAM・スピンメモリ技術 (17,699) | セル構成 (5,615) | アーキテクチャ (1,063) | クロスポイント方式 (193)

Fターム[4M119DD42]の下位に属するFターム

1セルに複数の記憶素子を含むもの (13)

Fターム[4M119DD42]に分類される特許

1 - 20 / 180

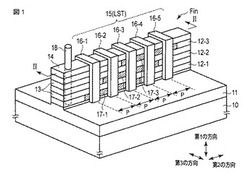

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

半導体装置

【課題】抵抗変化素子を備える半導体装置(半導体チップ)のチップ面積を削減すること。

【解決手段】半導体装置(1)は、半導体基板(50)上に形成されたトランジスタ(71)を含む下層回路(70)と、半導体基板(50)の上方の配線層(60)に形成されたメモリセルアレイ(20)と、を備える。メモリセルアレイ(20)の各メモリセル(MC)は、配線層(60)に形成された抵抗変化素子(40)を記憶素子として備る。メモリセルアレイ(20)は、メモリセル(MC)の直下に当該メモリセル(MC)との電気的接続用のビアが形成されていない第1領域(RF)を有している。下層回路(70)は、第1領域(RF)の少なくとも一部とオーバーラップするように配置されている。

(もっと読む)

磁気抵抗効果素子、ダイオードおよびトランジスタを用いた磁気ランダムアクセスメモリ

【課題】高速動作を可能にする磁気メモリを提供する。

【解決手段】本実施形態の磁気メモリは、スピン注入書込みによって磁化の方向が不変の第1磁性層と、磁化の方向が可変の第2磁性層と、前記第1磁性層と前記第2磁性層との間に設けられたトンネル障壁層とを有する磁気抵抗効果素子と、前記磁気抵抗効果素子の前記第1および第2磁性層の一方の磁性層に電気的に接続された第1配線と、ソース/ドレインの一方が前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に接続された選択トランジスタと、前記選択トランジスタのソース/ドレインの他方に電気的に接続された第2配線と、前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に一端子が電気的に接続されたダイオードと、前記ダイオードの他の端子に電気的に接続された第3配線と、前記第3配線に電気的に接続されたセンスアンプと、を備えている。

(もっと読む)

磁気メモリ素子、磁気メモリ装置、スピントランジスタ、及び集積回路

【課題】 本発明の実施形態によれば、単方向電流で書き込みが可能であり、微細化が可能な磁気メモリ素子、磁気メモリ装置、スピントランジスタ、及び集積回路を提供することができる。

【解決手段】 磁気メモリ素子は、磁化が可変の第1の強磁性層と、第1のバンド及び第2のバンドを有する第2の強磁性層と、前記第1の強磁性層と前記第2の強磁性層との間に設けられた非磁性層と、を備える。

(もっと読む)

磁気メモリ素子及び磁気メモリ装置

【課題】電流で書き込み動作を行うことができる大容量の磁気メモリ及び磁気メモリ装置を提供する。

【解決手段】磁化が固定された第1の磁性層10と、磁化が可変の第2の磁性層30と、第1の磁性層10と第2の磁性層30との間に設けられた第1の中間層20と、第1の磁性層10と第2の磁性層30とを結ぶ第1の方向に直交する第2の方向に延在し、第2の磁性層30に隣接し、スピン波を伝搬する第1の磁性細線40と、第1の磁性細線40の一端に設けられた第1のスピン波入力部と、第1の磁性細線40の他端に設けられた第1のスピン波検出部と、を備える。

(もっと読む)

コバルト薄膜およびその形成方法ならびにナノ接合素子およびその製造方法ならびに配線およびその形成方法

【課題】厚さが35nm以下でも十分に高い保磁力および角型比を有する磁性のコバルト薄膜を得ることができるコバルト薄膜の形成方法およびこの方法により形成したコバルト薄膜を用いたナノ接合素子を提供する。

【解決手段】ポリエチレンナフタレート基板11上に真空蒸着法などによりコバルト薄膜12を35nm以下の厚さに成膜する。こうしてポリエチレンナフタレート基板11上にコバルト薄膜12を成膜した積層体を二つ用い、これらの二つの積層体をそれらのコバルト薄膜12のエッジ同士が、必要に応じて有機分子を挟んで、互いに対向するように交差させて接合することによりナノ接合素子を構成する。このナノ接合素子により不揮発性メモリや磁気抵抗効果素子を構成する。ポリエチレンナフタレート基板11の代わりに、少なくとも一主面がSiO2 からなる基板、例えば石英基板を用いてもよい。

(もっと読む)

磁気メモリ構造およびトンネル磁気抵抗効果型再生ヘッドならびにそれらの製造方法

【課題】十分に高い抵抗変化率および絶縁破壊電圧を確保しつつ、安定した製造に適した磁気トンネル接合素子を備えた磁気メモリ構造を提供する。

【解決手段】この磁気メモリ構造は、基体上に、第1シード層と導電層とを順に有する下部電極と、導線としての上部電極と、下部電極と上部電極との間に配置され、かつ、下部電極の側から順に、下部電極と接すると共に窒化タンタルを含む第2シード層と、反強磁性ピンニング層と、ピンド層と、トンネルバリア層と、磁化自由層と、上部電極と接するキャップ層とを有する磁気トンネル接合素子とを備える。窒化タンタルは、窒素プラズマをタンタルのターゲットに衝突させる反応性スパッタリング処理によって形成されたものである。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

磁気抵抗効果素子、およびその製造方法

【課題】CCP−CPP素子のMR変化率を向上させる。

【解決手段】磁化が実質的に一方向に固着された磁化固着層と、前記磁化固着層と対向するようにして形成され、磁化が外部磁界に対して変化する磁化自由層と、前記磁化固着層と前記磁化自由層との間に位置し、絶縁層、及びこの絶縁層を層方向に電流を通過させる導電体とを有する電流狭窄層を含むスペーサ層と具える磁気抵抗効果素子において、前記磁化固着層の層中、前記磁化自由層の層中、前記磁化固着層及び前記スペーサ層の界面、並びに前記磁化自由層及び前記スペーサ層の界面の少なくとも一か所に、Si、Mg、B、Alを含む機能層を設ける。

(もっと読む)

磁気記録素子及び磁気メモリ

【課題】磁気記録素子のMR比の向上を図る。

【解決手段】実施形態に係わる磁気記録素子は、磁化が可変で磁化容易軸方向が膜面に垂直となる方向の磁気記録層11と、磁化が膜面に垂直となる方向に固定される磁気固着層12と、磁気記録層11と磁気固着層12との間の非磁性バリア層13と、磁気記録層11と非磁性バリア層13との間の挿入層14とを備える。挿入層14は、軟磁性材料、ホイスラー合金、ハーフメタル酸化物、及び、ハーフメタル窒化物のうちの1つを含む。

(もっと読む)

3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法

【課題】単純な方式で集積度が向上し電気的特性が改善された3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法を提供する。

【解決手段】本発明の半導体メモリ素子は、互いに異なるレベルに配置され、2つの交差点を定義する第1、第2、及び第3導線と、2つの交差点の各々に配置される2つのメモリセルを備え、第1及び第2導線は互いに平行に延長され、第3導線は延長されて第1及び第2導線と交差し、第1及び第2導線は垂直断面で見た時に第3導線の長さに沿って交互に配列され、第3導線は第1及び第2導線から垂直に離隔される。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の構成材料の特性劣化を抑制しつつ、基板とゲート絶縁膜との界面の界面準位密度を効率的に低減することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、基板100上に、ゲート絶縁膜102とゲート電極103とを含むトランジスタを形成する。さらに、基板100上に1層の配線層110を形成する処理と、1層の配線層110を配線パターンに加工する処理を1回以上行うことにより、基板100上に、1層以上の配線層113,115を含む配線構造を形成する。さらに、基板100上に、1層以上の配線層113,115のうちの少なくとも1層の配線層110が配線パターンに加工された後に、基板100上にマイクロ波を照射して基板100のアニールを行う。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ、磁気記録再生装置、メモリセルアレイ、及び磁気抵抗効果素子の製造方法

【課題】 本発明の実施形態によれば、劣化しにくく、MR変化率の大きい磁気抵抗効果素子、それを用いた磁気ヘッドアセンブリ、磁気記録再生装置、メモリセルアレイ、及び磁気抵抗効果素子の製造方法を提供することができる。

【解決手段】 磁気抵抗効果素子は、第1の電極と、第1の磁性層と、第2の磁性層と、スペーサ層と、Zn、In、Sn、及びCdから選択される少なくとも一つの元素とFe、Co、及びNiから選択される少なくとも一つの元素とを含む酸化物層と、酸化物層に接して設けられ、Zn、In、Sn、及びCdから選択される少なくとも一つの元素を0.5at%以上80at%以下の濃度で含み、かつFe、Co、及びNiから選択される少なくとも一つの元素を含む金属層とを備える。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録装置

【課題】MR変化率を高くすることができる磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録装置を提供する。

【解決手段】実施形態に係る磁気抵抗効果素子は、積層体と、前記積層体の積層方向に電流を流すための一対の電極と、を備える。前記積層体は、第1の磁性層と、第2の磁性層と、前記第1の磁性層と前記第2の磁性層との間に配置されたスペーサ層と、を有する。そして、前記第1の磁性層、前記第2の磁性層及び前記スペーサ層の少なくとも1つの層が金属酸化物からなる酸化物層を含み、前記金属酸化物の結晶構造は、NaCl構造である。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドアセンブリ及び磁気記録再生装置

【課題】 十分なMR変化率を有する磁気抵抗効果素子及びその製造方法を提供する。

【解決手段】 本発明の磁気抵抗効果素子は、第1の磁性層14と、第2の磁性層18と、第1の磁性層14と第2の磁性層18との間に設けられたスペーサ層16とを備えた積層体と、積層体の膜面に垂直に電流を流すための一対の電極11、20とを有し、スペーサ層16が、Zn、In、Sn、Cdから選択される少なくとも1つの元素及びFe、Co、Niから選択される少なくとも1つの元素を含む酸化物層21を含む。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】データ消失温度が高く、かつ生産性の高い不揮発性記憶装置およびその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性記憶装置の製造方法は、第1の記憶部と、第1の記憶部が有するデータ消失温度よりも高いデータ消失温度を有する第2の記憶部と、を有する不揮発性記憶装置の製造方法であって、第2の記憶部のメモリセルを形成するための第2の積層体を形成する工程と、第1の記憶部が形成される領域に形成された第2の積層体を除去する工程と、第1の記憶部のメモリセルを形成するための第1の積層体を形成する工程と、第2の記憶部が形成される領域に形成された第1の積層体を除去する工程と、第1の記憶部が形成される領域に形成された第1の積層体と、第2の記憶部が形成される領域に形成された第2の積層体と、を同時に処理して、第1の積層体から第1の記憶部のメモリセルを形成するとともに、第2の積層体から第2の記憶部のメモリセルを形成する工程と、を備えている。

(もっと読む)

磁気抵抗素子

【課題】従来よりも高いMR比を持った磁気抵抗素子とその製造方法を提供する。

【解決手段】本発明は、磁気ディスク駆動装置の磁気再生ヘッド、磁気ランダムアクセスメモリの記憶素子及び磁気センサーに用いられる磁気抵抗素子、好ましくは、トンネル磁気抵抗素子(さらに好ましくは、スピンバルブ型トンネル磁気抵抗素子)に関し、基板、トンネルバリア層、Co(コバルト)Fe(鉄)合金からなる強磁性層及びB(ボロン)を含有した非磁性金属層を有する磁気抵抗素子。

(もっと読む)

面外磁気トンネル接合セルの強磁性自由層の磁化方向を切換える方法、磁気メモリシステムおよびデータを電子的に記憶する方法

【課題】関連の強磁性層の磁気異方性(すなわち、磁化方向)をウェハ面に垂直にまたは「面外に」位置合わせさせた、しばしば磁気トンネル接合セルと称される磁気スピントルクメモリセル、およびそれらを利用する方法を提供する。

【解決手段】面外磁気トンネル接合セルの強磁性自由層の磁化方向を切換える方法であって、ACスイッチング電流を上記面外磁気トンネル接合セルに通すステップを含む。ACスイッチング電流は、上記強磁性自由層の磁化方向を切換える。

(もっと読む)

1 - 20 / 180

[ Back to top ]