Fターム[4M119DD52]の内容

MRAM・スピンメモリ技術 (17,699) | セル構成 (5,615) | 記憶素子間の位置関係 (74) | 複数の記憶素子を垂直方向に積層するもの (67)

Fターム[4M119DD52]に分類される特許

1 - 20 / 67

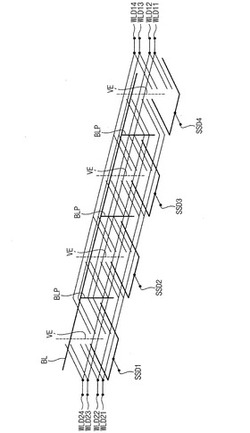

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

メモリ装置

【課題】増加されたメモリ容量を具現できるメモリ装置を提供する。

【解決手段】メモリ装置は、水平な共通導電領域の上に配置され、前記共通導電領域に一端が電気的に連結され、互いに離隔水平な第1選択ラインの上で互いに平行に延長され前記水平な第1選択ラインと交差し前記垂直な半導体柱の側面に対向する側面を包含する水平な第1選択ラインと、前記水平な第1選択ラインと前記垂直な半導体柱との間に、そして前記水平な第2選択ラインと前記垂直な半導体柱との間に介在される少なくとも1つの誘電パターンを包含する選択構造体を含む。前記メモリ装置は、前記選択構造体の上に配置され前記垂直な半導体柱に電気的に連結されたメモリセルを含むメモリセルアレイをさらに含む。

(もっと読む)

磁気メモリ及びその製造方法

【課題】低コストで広帯域の読出方式の、磁壁で区切られた磁区毎に情報が記録された磁

性配線を有する磁気メモリを提供する。

【解決手段】磁区、及び前記磁区を仕切る磁壁を有する第1磁性細線と、前記第1磁性細

線の両端部に配置される電流導入用電極と、前記第1磁性配線に隣接して設けられる書き

込み部と、前記第1磁性配線に交差するように設けられる第2磁性細線と、前記第2磁性

配線の一端部に設けられるスピン波発生部と、前記第2磁性配線の他端部に設けられるス

ピン波検出部とを備える。

(もっと読む)

磁気抵抗効果素子、ダイオードおよびトランジスタを用いた磁気ランダムアクセスメモリ

【課題】高速動作を可能にする磁気メモリを提供する。

【解決手段】本実施形態の磁気メモリは、スピン注入書込みによって磁化の方向が不変の第1磁性層と、磁化の方向が可変の第2磁性層と、前記第1磁性層と前記第2磁性層との間に設けられたトンネル障壁層とを有する磁気抵抗効果素子と、前記磁気抵抗効果素子の前記第1および第2磁性層の一方の磁性層に電気的に接続された第1配線と、ソース/ドレインの一方が前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に接続された選択トランジスタと、前記選択トランジスタのソース/ドレインの他方に電気的に接続された第2配線と、前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に一端子が電気的に接続されたダイオードと、前記ダイオードの他の端子に電気的に接続された第3配線と、前記第3配線に電気的に接続されたセンスアンプと、を備えている。

(もっと読む)

磁気メモリ素子

【課題】実施形態による、磁壁制御が容易な磁気メモリ素子を提供する。

【解決手段】磁気メモリ素子100は、第1方向に延在し、磁壁により隔てられた複数の磁区を有する磁性細線20と、前記磁性細線20に対して前記第1の方向又は前記第1の方向と逆方向に通電可能な一対の第1の電極30と、前記第1の方向に直交する第2の方向において、前記磁性細線20上に設けられた第1の絶縁層40と、前記第2の方向であって前記第1の絶縁層40上に離間して設けられた複数の第2の電極50と、複数の前記第2の電極50と電気的に接続された第3の電極60と、を備える。

(もっと読む)

磁気記憶素子及び不揮発性記憶装置

【課題】高密度化が可能な磁気記憶素子及び不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、積層体を備えた磁気記憶素子が提供される。積層体は第1積層部と第2積層部とを含む。第1積層部は、膜面に対して垂直成分を有する第1の方向に磁化が固定された第1強磁性層と、磁化の方向が膜面垂直な方向に可変である第2強磁性層と、第1強磁性層と第2強磁性層との間の第1非磁性層と、を含む。第2積層部は、積層方向に沿って第1積層部と積層される。第2積層部は、磁化の方向が膜面平行な方向に可変である第3強磁性層と、膜面に対して垂直成分を有する第2の方向に磁化が固定された第4強磁性層と、第3強磁性層と第4強磁性層との間の2非磁性層と、を含む。積層方向を法線とする平面で切断したとき、第3強磁性層の断面積は前記第1積層部よりも小さい。

(もっと読む)

不揮発性記憶装置

【課題】安定した動作が可能な不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、磁気記憶素子と制御部とを備えた不揮発性記憶装置が提供される。磁気記憶素子は積層体を含む。積層体は第1積層部と第2積層部とを含む。第1積層部は、磁化が固定された第1強磁性層と、磁化の方向が可変の第2強磁性層と、第1強磁性層と第2強磁性層との間に設けられた第1非磁性層と、を含む。第2積層部は、積層方向に沿って第1積層部と積層される。第2積層部は、通電される電流によって磁化が回転して発振が生じる第3強磁性層と、磁化が固定された第4強磁性層と、第3強磁性層と第4強磁性層との間に設けられた第2非磁性層と、を含む。制御部は、第2強磁性層の磁化の向きに応じた第3強磁性層の発振の周波数の変化を検出することで、第2強磁性層の磁化の向きを読み出す読み出し部を含む。

(もっと読む)

磁気記憶素子及び不揮発性記憶装置

【課題】安定した動作が可能な磁気記憶素子及び不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、第1、第2積層部を含む磁気記憶素子が提供される。第1積層部は、第1強磁性層/第1非磁性層/第2強磁性層を含む。第1強磁性層の磁化は面直に固定され、第2強磁性層の磁化方向は面直に可変である。第2積層部は、第3強磁性層/第2非磁性層/第4強磁性層を含む。第3強磁性層の磁化方向は面内方向に可変であり、第4強磁性層の磁化は面直に固定されている。第3強磁性層の位置での第1、第2、第4強磁性層からの漏れ磁界Hs、第3強磁性層の磁気異方性Ku、ダンピング定数α、磁化Ms及び反磁界係数Nzは、Ku≦αMs(8πNzMs−Hs)を満たす。電流によりスピン偏極した電子と、第3強磁性層で発生する回転磁界と、を第2強磁性層に作用させ、第2強磁性層の磁化方向を決定できる。

(もっと読む)

記憶装置及びその製造方法

【課題】磁気トンネル接合素子を用いた構造において、製造工程の簡素化を達成することができる記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る記憶装置は、第1信号線と、第2信号線と、トランジスタと、記憶領域と、導通領域と、を備える。トランジスタは、第1信号線と、第2信号線と、のあいだを流れる第1方向の電流及びこれと反対の第2方向の電流の導通を制御する。記憶領域は、第1信号線と、トランジスタの一方端と、のあいだに接続され、第1の平行閾値以上の電流が第1方向に流れると磁化の向きが平行になり、第1の反平行閾値以上の電流が第2方向に流れると磁化の向きが反平行になる第1磁気トンネル接合素子を有する。導通領域は、第2信号線と、トランジスタの他方端と、のあいだに接続される。

(もっと読む)

磁気抵抗素子及び磁気記憶装置

【課題】界面磁化膜を固定磁化層及び自由磁化層として有するMTJを積層し、エッチング工程のダメージのない所期の多値化を確実に実現することのできる信頼性の高い磁気抵抗素子及び磁気記憶装置を提供する。

【解決手段】多値メモリ10Aは、MTJ10aと、MTJ10aの上方に設けられたMTJ10bと、MTJ10a,10b間に設けられた接続層13とを含み、MTJ10a,10bは、夫々、Taからなる挿入層1a,1bと、挿入層1a,1b上で当該挿入層1a,1bに接し、主面に垂直方向の磁気異方性を有する下部磁化層2a,2bと、主面に垂直方向の磁気異方性を有する上部磁化層4a,4bと、下部磁化層2a,2bと上部磁化層4a,4bとの間に設けられたトンネルバリア層3a,3bとを有しており、上部磁化層2a,2b及び下部磁化層4a,4bは、一方が固定磁化層であり、他方が自由磁化層である.

(もっと読む)

磁壁移動型の磁気記録素子及び磁気記録方法

【課題】磁壁の移動が可能となる閾値電流密度を、従来技術であるスピントルクを利用して電流で磁壁移動を行った場合と比較して低減する磁壁移動型の磁気記録素子構造及び閾値電流密度を低減化させる磁気記録方法を提供すること。

【解決手段】本発明の磁壁移動型の磁気記録素子は、金属層/磁性層/非伝導層の3層膜から構成される実効磁場発生構造を持ち、前記磁性層に電流を流したときに発生する実効磁場とスピントルクを用いて前記磁性層中の磁壁の位置を制御することを特徴とする。

(もっと読む)

半導体装置及び磁気ランダムアクセスメモリ

【課題】磁気ランダムアクセスメモリの読み出しマージンを増大させる。

【解決手段】メモリセル200は、磁気記録層2と、磁気記録層2に接合された固定層11、12と、磁気記録層2に対向するように設けられたリファレンス層41、42と、リファレンス層41、42と磁気記録層2との間にそれぞれに挿入されたトンネルバリア膜31、32とを備えている。固定層11、12は、互いに逆の方向に固定された磁化を有している。リファレンス層41、42とトンネルバリア膜31、32とは、固定層11、12の間の位置に設けられている。リファレンス層41、42は、互いに逆の方向に固定された磁化を有している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

磁気記憶素子、磁気記憶装置、磁壁移動方法

【課題】磁性体中の磁壁を安定して移動させる磁気記憶素子、および磁壁移動方法を提供する。

【解決手段】実施形態による磁気記憶素子は、第1電極11と、第2電極12と、前記第1電極11と前記第2電極12との間に設けられ、複数の第1磁性層141および、この第1磁性層141の間に設けられ、第1磁性層141とは構成元素の組成が異なる第2磁性層142を含む積層構造と、前記第1電極11の前記積層構造側の面の反対の面に設けられる圧電体15と、前記圧電体15の前記第1電極11が設けられる位置と異なる位置に設けられ、前記圧電体15に電圧を印加する第3電極13を有する。

(もっと読む)

磁気素子及び不揮発性記憶装置

【課題】読み出し時の誤書き込みを抑制する磁気素子及び不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、第1導電層と、第2導電層と、中間配線と、第1積層部と、第2積層部と、を備えた磁気素子が提供される。中間配線は、第1導電層と第2導電層との間に設けられる。第1積層部は、第1導電層と中間配線との間に設けられる。第1積層部は、第1方向に磁化が固定された第1強磁性層と、第1強磁性層と積層され、磁化の方向が可変である第2強磁性層と、第1強磁性層と第2強磁性層との間に設けられた第1非磁性層と、を含む。第2積層部は、第2導電層と中間配線との間に設けられる。第2積層部は、磁化の方向が可変である第3強磁性層と、第3強磁性層と積層され、第2方向に磁化が固定された第4強磁性層と、第3強磁性層と第4強磁性層との間に設けられた第2非磁性層と、を含む。

(もっと読む)

磁気記録素子及び不揮発性記憶装置

【課題】書き込み時における磁化反転がより高速に起こる磁気記録素子及び不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、積層体を備えた磁気記録素子が提供される。積層体は第1積層部と第2積層部とを含む。第1積層部は、膜面に対して垂直成分を有する第1の方向に磁化が固定された第1の強磁性層と、磁化の方向が膜面垂直な方向に可変である第2の強磁性層と、第1の強磁性層と第2の強磁性層との間の第1の非磁性層と、を含む。第2積層部は、積層軸に沿って第1積層部と積層される。第2積層部は、磁化の方向が膜面平行な方向に可変である第3の強磁性層と、膜面に対して垂直成分を有する第2の方向に磁化が固定された第4の強磁性層と、第3の強磁性層と第4の強磁性層との間の2の非磁性層と、を含む。積層軸を法線とする平面において、第4の強磁性層の外縁は第1積層部の外縁よりも外側の部分を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の構成材料の特性劣化を抑制しつつ、基板とゲート絶縁膜との界面の界面準位密度を効率的に低減することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、基板100上に、ゲート絶縁膜102とゲート電極103とを含むトランジスタを形成する。さらに、基板100上に1層の配線層110を形成する処理と、1層の配線層110を配線パターンに加工する処理を1回以上行うことにより、基板100上に、1層以上の配線層113,115を含む配線構造を形成する。さらに、基板100上に、1層以上の配線層113,115のうちの少なくとも1層の配線層110が配線パターンに加工された後に、基板100上にマイクロ波を照射して基板100のアニールを行う。

(もっと読む)

集積回路とその製造方法

【課題】今後ますます増加するトランジスタの閾値のばらつきに対して、高速に動作させることができる集積回路を提供する。

【解決手段】集積回路1は、電流制御型のMOS電流論理回路10と、電流制御型のMOS電流論理回路10の定電流用MOSFET16に接続される可変抵抗素子20と、電流制御型のMOS電流論理回路10の閾値のばらつきにより生じる出力基準電圧の変動△VBを検出するアンプ22と、可変抵抗素子20の抵抗値を書き込む回路34と、を備えている。電流制御型のMOS電流論理回路10の基準電圧VBと出力信号との差がアンプ22によって検出され、可変抵抗素子20の抵抗が書き込み回路34によって書き込まれる。回路を構成するトランジスタの閾値がばらついても、集積回路1は高速且つ安定に動作する。

(もっと読む)

トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

1 - 20 / 67

[ Back to top ]