Fターム[4M119EE22]の内容

MRAM・スピンメモリ技術 (17,699) | 配線構成 (2,374) | ビット線(BL) (891) | BLが1セル、ユニットに1本だけ有するもの (643)

Fターム[4M119EE22]に分類される特許

61 - 80 / 643

記憶素子、記憶装置

【課題】スピントルク型磁気メモリにおいて、熱安定性及び反転電流のバラツキを抑制する。

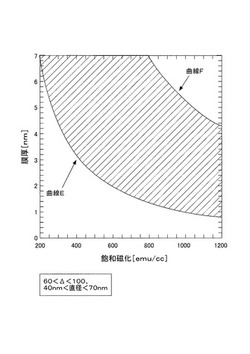

【解決手段】上記記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、上記記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する。そして積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して記憶層の磁化を反転させることにより情報の記憶を行う。この構成において、記憶層の飽和磁化をMs(emu/cc)、上記記憶層の膜厚をt(nm)としたときに、記憶層の膜厚tは、(1489/Ms)−0.593<t<(6820/Ms)−1.55を満たすようにする。

(もっと読む)

磁気メモリデバイスの駆動方法及び磁気メモリデバイス

【課題】基準素子におけるディスターバンスの発生を防止することができる磁気メモリデバイスを提供する。

【解決手段】基準セル28が、基準素子20を含む。基準素子は、固定磁化層21、絶縁層22、自由磁化層23を含み、自由磁化層の磁化方向は固定磁化層の磁化方向と反平行であり、メモリセル18の磁気抵抗素子10が平行状態のときの抵抗値と反平行状態のときの抵抗値との間の抵抗値を有する。基準素子に、基準素子の固定磁化層から自由磁化層に向かう読出電流を流し、磁気抵抗素子の抵抗値と、基準素子の抵抗値との大小関係に依存する物理量を検出することにより、情報の読出しを行う。

(もっと読む)

磁気メモリ

【課題】書き込み時に固定層が安定化された、垂直磁化型トンネル磁気抵抗効果素子を用いたスピントルク磁化反転応用の磁気メモリを提供する。

【解決手段】膜面に垂直な方向の磁化を有する自由層62と、膜面に垂直な一方向に磁化が固定された固定層64と、固定層と自由層の間に形成された非磁性障壁層63を有する磁気抵抗効果素子において、互いに隣接したメモリセルの固定層を一列方向に接続する。

(もっと読む)

記憶素子、記憶装置

【課題】垂直磁化を有するスピントルク型磁気メモリにおいて、垂直磁気異方性を強化し、高い情報保持特性を実現させる。

【解決手段】記憶素子は、膜面に対して垂直な磁化を有し、情報を磁性体の磁化状態により保持する記憶層17と、記憶層17に記憶された情報の基準となる、膜面に対して垂直な磁化を有する磁化固定層15と、記憶層17と磁化固定層15の間に設けられる非磁性体による中間層16とによるMTJ構造を持つものとする。この場合に、中間層16と反対側で記憶層17に隣接する、2層以上の酸化物で形成されたキャップ層18を設けるようにする。

(もっと読む)

記憶素子、記憶装置

【課題】書込電流を増大させることなく、高い保磁力を有し熱安定性を改善することができる記憶素子の提供。

【解決手段】記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、記憶層と磁化固定層の間に設けられる非磁性体による中間層と、磁化固定層に隣接し、中間層の反対側に設けられる磁気結合層と、磁気結合層に隣接して設けられる高保磁力層とを有する。

そして記憶層、中間層、磁化固定層を有する層構造の積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して上記記憶層の磁化を反転させることにより情報の記憶を行うとともに磁気結合層が2層の積層構造となっている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】MRAMの下層強誘電体層と上層強誘電体層がショートしているか否かを検査することができる。

【解決手段】TEG素子100は、テスト用下層強誘電体層112、テスト用トンネル絶縁膜114、及びテスト用上層強誘電体層116を有している。テスト用下層強誘電体層112は、下層強誘電体層42と同一層に位置し、下層強誘電体層42と同一材料により形成されており、第1テスト用パッド120に接続している。テスト用トンネル絶縁膜114は、トンネル絶縁膜44と同一層に位置し、トンネル絶縁膜44と同一材料により形成されている。テスト用上層強誘電体層116は、上層強誘電体層46と同一層に位置し、上層強誘電体層46と同一材料により形成されており、第2テスト用パッド130に接続している。

(もっと読む)

記憶素子、記憶装置

【課題】スピントルク型磁気メモリにおいて、異方性エネルギーを大きくし、微細化しても十分な熱揺らぎ耐性を有するようにする。

【解決手段】記憶素子は、膜面に対して垂直な磁化を有し、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる、膜面に対して垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とにより、MTJ構造を持つ。これに加え、記憶層に隣接する、Cr、Ru、W、Si、Mnの少なくとも一つからなる保磁力強化層と、保磁力強化層に隣接する酸化物によるスピンバリア層を設ける。

(もっと読む)

半導体記憶装置

【課題】MTJ素子の形状およびサイズのばらつきを抑制し、かつ、MTJ素子を製造し易い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。複数の磁気トンネル接合素子は、半導体基板の上方に形成され、抵抗状態の変化によってデータを記憶し、電流によってデータを書き換え可能である。複数のセルトランジスタは、半導体基板に形成され、磁気トンネル接合素子に対応して設けられ、該対応する磁気トンネル接合素子に電流を流すときに導通状態となる。複数のゲート電極は、セルトランジスタに含まれ、セルトランジスタの導通状態を制御する。複数のアクティブエリアは、セルトランジスタが形成され、前記ゲート電極に対して(90−atan(1/3))の角度で交差する方向に延伸している。

(もっと読む)

磁気記憶装置の製造方法および磁気記憶装置

【課題】TMR素子間の特性のばらつきを低減でき、かつ製造歩留まりの高い不揮発性磁気メモリの製造方法およびその構造を提供する。

【解決手段】TMR素子を含む磁気記憶装置の製造方法が、配線層が設けられた層間絶縁膜の上に、絶縁膜を形成する工程と、絶縁膜に、配線層が露出するように開口部を形成する開口工程と、開口部を埋めるように、絶縁膜上に金属層を形成する金属層形成工程と、CMP法を用いて絶縁膜上の金属層を研磨除去し、開口部内に残った金属層を下部電極とするCMP工程と、下部電極上にTMR素子を形成する工程とを含む。

(もっと読む)

記憶素子及び記憶装置

【課題】書込電流を増大させることなく、高い保持力を有し熱安定性を改善することができる記憶素子の提供。

【解決手段】記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、記憶層と磁化固定層の間に設けられる非磁性体による中間層と、記憶層に隣接し中間層と反対側に設けられるキャップ層と、キャップ層に隣接し記憶層と反対側に設けられる金属キャップ層を有する。そして記憶層、中間層、磁化固定層を有する層構造の積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して記憶層の磁化を反転させることにより情報の記憶を行う。そして中間層とキャップ層は酸化物であり、金属キャップ層はPdもしくはPtで構成されているものとする。

(もっと読む)

磁気メモリ装置のためのライトドライバー回路、磁気メモリ装置及びそのレイアウト構造

【課題】本発明の技術的な課題は、共通ソースラインを含む磁気メモリ装置に対してビットラインへ記録電流を供給することができるライトドライバー回路を提供すること、集積度が向上された磁気メモリ装置を提供すること、及び、共通ソースラインを有する磁気メモリ装置のレイアウト構造を提供することにある。

【解決手段】ビットラインとソースラインとの間に接続され、前記ビットライン方向に隣接する一対の磁気メモリセルが前記ソースラインを共有する複数の磁気メモリセルよりなるメモリセルアレイを有する磁気メモリ装置のためのライトドライバー回路であり、正の記録電圧の供給端子と副の記録電圧の供給端子との間に接続されて、ライトイネーブル信号及びデータ信号によって前記正の記録電圧または前記副の記録電圧による電流を前記ビットラインに選択的に供給するスイチング部を備える磁気メモリ装置を提供する。

(もっと読む)

磁気記憶素子、磁気記憶装置、磁壁移動方法

【課題】磁性体中の磁壁を安定して移動させる磁気記憶素子、および磁壁移動方法を提供する。

【解決手段】実施形態による磁気記憶素子は、第1電極11と、第2電極12と、前記第1電極11と前記第2電極12との間に設けられ、複数の第1磁性層141および、この第1磁性層141の間に設けられ、第1磁性層141とは構成元素の組成が異なる第2磁性層142を含む積層構造と、前記第1電極11の前記積層構造側の面の反対の面に設けられる圧電体15と、前記圧電体15の前記第1電極11が設けられる位置と異なる位置に設けられ、前記圧電体15に電圧を印加する第3電極13を有する。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になった磁気記憶素子のデータの誤反転を抑制することにより信頼性の高い書き込み動作を行うことができる磁気記憶素子、およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91と磁化困難軸92とを有する記録層3は、平面視においてすべての領域が第1導電層WTまたは第2導電層BLの少なくとも一方と重なる。磁化容易軸91に沿い、記録層3と平面視において重なる寸法が最大となる第1の線分の第1の端点TP,BPは、第2導電層BLと平面視において重ならない。上記第1の線分の中点を通り、平面視において第1の線分に直交し、記録層3と平面視において重なる第2の線分の1対の端点である第2の端点LP,RPのうち少なくとも一方は、第1導電層WTと平面視において重ならない。

(もっと読む)

磁気記憶素子、磁気記憶装置、および磁気メモリ

【課題】磁壁が静止した状態から移動状態に遷移させるために必要な電流密度を低減化することができるとともに、磁壁の移動を安定に行うことができる磁気記憶素子、磁気記憶装置、および磁気メモリを提供する。

【解決手段】本実施形態の磁気記憶素子は、第1方向に延在し、磁壁により隔てられた複数の磁区を有する磁性細線と、前記磁性細線に前記第1方向の電流および前記第1方向と逆方向の電流を流すことが可能な電極と、電気的な入力を受け、前記磁性細線の全体または一部の領域の磁壁の移動をアシストするアシスト部と、を備えている。

(もっと読む)

磁気記憶装置

【課題】集積度が高い磁気記憶装置を提供する。

【解決手段】実施形態に係る磁気記憶装置は、基板と、前記基板上に設けられた複数個の磁気抵抗効果素子と、を備える。そして、前記複数個の磁気抵抗効果素子のうち、上方から見て互いに最も近い位置にある2個の磁気抵抗効果素子は、前記基板からの距離が相互に異なる。

(もっと読む)

磁気抵抗素子および磁気メモリ

【課題】書込み電流の範囲を広くすることができるとともに書込み電流を低減することができる磁気抵抗素子および磁気メモリを提供する。

【解決手段】本実施形態の磁気抵抗素子は、膜面に垂直方向に磁化容易軸を有し、磁化が可変の第1強磁性層と、膜面に垂直方向に磁化容易軸を有し、磁化が不変の第2強磁性層と、第1強磁性層と第2強磁性層との間に設けられた第1非磁性層と、第2強磁性層に対して第1非磁性層と反対側に設けられ、それぞれが異なる発振周波数の回転磁界を発振する強磁性体の複数の発振体を有し、各発振体が膜面に平行な磁化を有する、第3強磁性層と、を備え、第3強磁性層と、第1強磁性層との間に電流を流すことにより、スピン偏極した電子を第1強磁性層に作用させるとともに、第3強磁性層の複数の発振体に作用させて前記発振体の磁化に歳差運動を誘起し、歳差運動によって生じた複数の回転周波数を有し第1強磁性層の磁化反転をアシストする回転磁界が第1強磁性層に印加される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 メモリセルの微細化を図りつつ、セル電流を確保する。

【解決手段】 実施形態による半導体記憶装置は、ゲート溝15と第1乃至第3の溝19a、19b、18とを有し、第1乃至第3の溝はゲート溝の底面に形成され、第3の溝は第1及び第2の溝の間に形成された半導体基板11と、第1の溝内形成された第1のゲート部21aと第2の溝内形成された第2のゲート部21bと第3の溝内形成された第3のゲート部21cとゲート溝内に形成された第4のゲート部21dとを有するゲート電極21と、を具備する。ゲート電極を有するセルトランジスタTrは、第1及び第3のゲート部間の半導体基板内に形成された第1のチャネル領域Ch1と、第2及び第3のゲート部間の半導体基板内に形成された第2のチャネル領域Ch2と、を有する。

(もっと読む)

磁気抵抗素子および磁気メモリ

【課題】垂直磁気異方性を有するとともにより大きな磁気抵抗効果を発現することが可能な磁気抵抗素子およびこれを用いた磁気メモリを提供する。

【解決手段】下地層と、下地層上に設けられ、膜面に垂直方向に磁化容易軸を有し、MnxGa100−x(45≦x<64atm%)である磁性体膜を含む第1の磁性層と、第1の磁性層上に設けられた第1の非磁性層と、第1の非磁性層上に設けられ、膜面に垂直方向に磁化容易軸を有し、MnyGa100−y(45≦x<64atm%)である磁性体膜を含む第2の磁性層と、を備え、第1および第2の磁性層のMnの組成比が異なり、第1の非磁性層を介して第1の磁性層と第2の磁性層との間に流れる電流によって、第1の磁性層の磁化方向が可変となる。

(もっと読む)

磁気メモリの製造方法

【課題】磁化反転に必要とされる電流密度のマージンを広げる。

【解決手段】実施形態に係わる磁気メモリの製造方法は、磁化方向が可変である第1の磁性層16を形成する工程と、第1の磁性層16上にトンネルバリア層17を形成する工程と、トンネルバリア層17上に、磁化方向が不変である第2の磁性層19を形成する工程と、第2の磁性層19上にハードマスク層20を形成する工程と、ハードマスク層20をマスクにして第2の磁性層19のパターニングを行なう工程と、第2の磁性層19のパターニング後に、ハードマスク層20をマスクにしてGCIB照射を行うことにより、少なくとも第1の磁性層16内に磁気的及び電気的に不活性な領域Nonを形成する工程とを備える。

(もっと読む)

半導体記憶装置

【課題】半導体基板の表面の空き領域が少ない半導体記憶装置を提供する。

【解決手段】このMRAMの各メモリセルMCは、磁気抵抗素子18と2つのアクセストランジスタ19a,19bを含み、トランジスタ19a,19bのドレインを磁気抵抗素子18を介して対応のビット線BLに接続し、それらのゲートを対応のワード線WLに接続し、それらのソースをそれぞれソース線SLおよび補助配線ALに接続する。したがって、アクセストランジスタ19bのソースとDLドライバ14に含まれるドライバトランジスタ23のソースとを共通化することができ、シリコン基板31の表面の空き領域を減らすことができる。

(もっと読む)

61 - 80 / 643

[ Back to top ]