Fターム[4M119FF06]の内容

MRAM・スピンメモリ技術 (17,699) | コンタクト (2,004) | コンタクトの形状又は作成方法 (789) | 中継パッドを有するもの (176)

Fターム[4M119FF06]に分類される特許

1 - 20 / 176

半導体装置の製造方法

半導体集積回路およびその動作方法

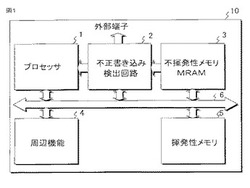

【課題】半導体集積回路の内蔵メモリとしてのMRAMへの不正アクセスに対する保護を改善すること。

【解決手段】半導体集積回路(10)は、プロセッサ(1)と不揮発性メモリ(3)とを具備する。不揮発性メモリ(3)は、複数の磁気ランダムアクセスメモリセルと、複数の磁気リードオンリーメモリセルとを含む。複数の磁気ランダムアクセスメモリセルはプロセッサ(1)による通常書き込みによって書き換えが可能とされ、複数の磁気リードオンリーメモリセルはプロセッサ(1)による通常書き込みによって書き換えが不可能とされる。不揮発性メモリ(3)と接続された感知回路(2)は、不揮発性メモリ(3)の不正アクセスによる複数の磁気リードオンリーメモリセルの状態遷移を感知する。状態遷移に応答して、感知回路(2)は不正アクセスの検出結果をプロセッサ(1)に通知する。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】書き込み電流の低減およびリテンション特性の向上を図る。

【解決手段】磁気抵抗効果素子は、磁化方向が膜面に対して垂直でかつ可変である第1磁性層31と、前記第1磁性層上に形成されたトンネルバリア層32と、前記トンネルバリア層上に形成され、磁化方向が膜面に対して垂直でかつ不変である第2磁性層40と、を具備する。前記第2磁性層は、垂直磁気異方性の起源となる本体層34と、前記トンネルバリア層と前記本体層との間に形成され、前記本体層よりも高い透磁率を有し、前記本体層よりも大きい平面サイズを有する界面層33と、を備える。前記本体層の側面に、前記本体層よりも高い透磁率を有するシールド層90が形成されている。

(もっと読む)

スパッタリングターゲット及びそれを用いた磁気メモリの製造方法

【課題】磁気トンネル接合素子のMR比を向上させることが可能なスパッタリングターゲット、及びそれを用いた磁気メモリの製造方法を提供する。

【解決手段】MgOを主成分とし、厚さが3mm以下であるターゲット本体10を備えることを特徴とするスパッタリングターゲット、及びそれを用いた、MR比を向上させることができる磁気メモリの製造方法である。

(もっと読む)

トンネル磁気抵抗効果素子、非局所スピン注入素子、及びそれを用いた磁気ヘッド

【課題】小さいバンドギャップを持つ障壁膜を岩塩構造の(001)方向に高配向させて、低抵抗かつ高効率なスピン注入素子を提供する。

【解決手段】下地膜300、非磁性シード膜310、強磁性膜305、障壁膜307、強磁性膜308、保護膜309を積層してトンネル磁気抵抗効果素子1を形成する。非磁性シード膜310として、格子定数が強磁性膜305の格子定数の√2倍よりも小さい面心立方格子の物質を用いる。

(もっと読む)

電子装置、半導体装置およびその制御方法、ならびに携帯端末装置

【課題】選択されない磁気抵抗素子の磁化状態が誤って書き換えられる現象の発生が確実に抑制される半導体装置の制御方法を提供する。

【解決手段】当該制御方法は、半導体基板と、半導体基板の主表面上に位置する、固定層MPLと、トンネル絶縁層と、磁化容易軸を有する自由層MFLとを含む磁気抵抗素子と、磁気抵抗素子に隣接する第1の配線とを備える半導体装置における磁化状態を書き換える制御方法である。上記制御方法は以下の工程を備えている。まず上記自由層MFLの磁化状態を変更する前の初期磁化状態が判定される。上記判定する工程において、自由層MFLの磁化状態を変更する必要があると判定された場合に、第1の配線にパルス電流が流される。上記パルス電流により、自由層MFLの磁化容易軸と交差する方向に発生するパルス磁場を磁気抵抗素子に印加することにより自由層MFLの磁化状態が変更される。

(もっと読む)

半導体装置及び磁気ランダムアクセスメモリ

【課題】磁気ランダムアクセスメモリの読み出しマージンを増大させる。

【解決手段】メモリセル200は、磁気記録層2と、磁気記録層2に接合された固定層11、12と、磁気記録層2に対向するように設けられたリファレンス層41、42と、リファレンス層41、42と磁気記録層2との間にそれぞれに挿入されたトンネルバリア膜31、32とを備えている。固定層11、12は、互いに逆の方向に固定された磁化を有している。リファレンス層41、42とトンネルバリア膜31、32とは、固定層11、12の間の位置に設けられている。リファレンス層41、42は、互いに逆の方向に固定された磁化を有している。

(もっと読む)

トンネル磁気抵抗効果素子、それを用いた磁気メモリセル及びランダムアクセスメモリ

【課題】高熱安定性を有する高速超低消費電力不揮発性メモリを提供する。

【解決手段】不揮発性磁気メモリに、高い熱安定性をもつ自由層を適用した高出力なトンネル磁気抵抗効果素子を装備し、スピントランスファートルクによる書込み方式を適用する。トンネル磁気抵抗効果素子1は、CoとFeとBを含有する体心立方構造の第一の強磁性膜306と第二の強磁性膜308と第一の非磁性膜307で構成される自由層を持ち、自由層に(100)配向した岩塩構造のMgO絶縁膜305を介して固定層3021を積層した構造を有する。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】磁気抵抗効果素子のスピン注入磁化反転特性の劣化が抑制され、製造歩留まりが高い不揮発性記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、複数のメモリセルを有する不揮発性記憶装置の製造方法であって、前記メモリセルのそれぞれは、第1電極を含む下地層と、前記下地層の上に設けられた磁気抵抗効果素子と、前記磁気抵抗効果素子の上に設けられた第2電極と、を有する。前記磁気抵抗効果素子は、記憶層である第1磁性層と、前記第1磁性層の上に設けられたトンネルバリア層と、前記トンネルバリア層の上に設けられ、参照層である第2磁性層と、を含む。前記第2磁性層の表面の一部もしくは前記第1磁性層の表面の一部にイオン化されたガスクラスタを照射して、前記第2磁性層の一部および前記第1磁性層の一部をエッチングする。

(もっと読む)

半導体記憶装置

【課題】MTJ素子にデータを書き込むために充分に大きな電流を駆動することができるセルトランジスタを備え、かつ、容易に製造可能なメモリを提供する。

【解決手段】本実施形態によるメモリはアクティブエリアを備え、セルトランジスタはアクティブエリアに形成されている。MTJ素子の一端がセルトランジスタのソース/ドレインの一方に電気的に接続されている。第1のビット線は、セルトランジスタのソース/ドレインの他方に電気的に接続されている。第2のビット線は、MTJ素子の他端に電気的に接続されている。ワード線は、セルトランジスタのゲートに電気的に接続され、あるいは、セルトランジスタのゲートとして機能する。1つの第1のビット線に対して複数の第2のビット線が対応している。MTJ素子が同一のワード線および同一のアクティブエリアを共有している。アクティブエリアは、第1および第2のビット線の延伸方向に連続して形成されている。

(もっと読む)

磁気記憶装置及び磁気記憶装置の製造方法

【課題】 基準素子の抵抗値のばらつきを抑制することが望まれている。

【解決手段】 基板上に磁気抵抗素子及び基準素子が形成されている。磁気抵抗素子は、トンネル絶縁層を自由磁化層と固定磁化層とで挟んだ構造を有し、自由磁化層の磁化方向によって低抵抗状態と高抵抗状態との間で抵抗が変化し、第1の方向に長い平面形状を有する。基準素子は、トンネル絶縁層を自由磁化層と固定磁化層とで挟んだ構造を有し、磁気抵抗素子の低抵抗状態の抵抗と高抵抗状態の抵抗との間の抵抗を有し、第1の方向と直交する第2の方向に長い平面形状を有する。

(もっと読む)

磁気メモリセル及びランダムアクセスメモリ

【課題】信頼性の高い低消費電力不揮発性メモリを提供する。

【解決手段】磁気メモリセルが備えるトンネル磁気抵抗効果素子402の強磁性自由層200の磁化容易軸方向に対して直交する方向、特に膜面垂直方向に45度の角度をなす方向に適当な磁界を印加した状態でスピントランスファートルクにより強磁性自由層の磁化反転を行う。

(もっと読む)

磁気メモリデバイスの駆動方法及び磁気メモリデバイス

【課題】基準素子におけるディスターバンスの発生を防止することができる磁気メモリデバイスを提供する。

【解決手段】基準セル28が、基準素子20を含む。基準素子は、固定磁化層21、絶縁層22、自由磁化層23を含み、自由磁化層の磁化方向は固定磁化層の磁化方向と反平行であり、メモリセル18の磁気抵抗素子10が平行状態のときの抵抗値と反平行状態のときの抵抗値との間の抵抗値を有する。基準素子に、基準素子の固定磁化層から自由磁化層に向かう読出電流を流し、磁気抵抗素子の抵抗値と、基準素子の抵抗値との大小関係に依存する物理量を検出することにより、情報の読出しを行う。

(もっと読む)

磁気記憶装置の製造方法および磁気記憶装置

【課題】TMR素子間の特性のばらつきを低減でき、かつ製造歩留まりの高い不揮発性磁気メモリの製造方法およびその構造を提供する。

【解決手段】TMR素子を含む磁気記憶装置の製造方法が、配線層が設けられた層間絶縁膜の上に、絶縁膜を形成する工程と、絶縁膜に、配線層が露出するように開口部を形成する開口工程と、開口部を埋めるように、絶縁膜上に金属層を形成する金属層形成工程と、CMP法を用いて絶縁膜上の金属層を研磨除去し、開口部内に残った金属層を下部電極とするCMP工程と、下部電極上にTMR素子を形成する工程とを含む。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になった磁気記憶素子のデータの誤反転を抑制することにより信頼性の高い書き込み動作を行うことができる磁気記憶素子、およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91と磁化困難軸92とを有する記録層3は、平面視においてすべての領域が第1導電層WTまたは第2導電層BLの少なくとも一方と重なる。磁化容易軸91に沿い、記録層3と平面視において重なる寸法が最大となる第1の線分の第1の端点TP,BPは、第2導電層BLと平面視において重ならない。上記第1の線分の中点を通り、平面視において第1の線分に直交し、記録層3と平面視において重なる第2の線分の1対の端点である第2の端点LP,RPのうち少なくとも一方は、第1導電層WTと平面視において重ならない。

(もっと読む)

磁気抵抗素子および磁気メモリ

【課題】書込み電流の範囲を広くすることができるとともに書込み電流を低減することができる磁気抵抗素子および磁気メモリを提供する。

【解決手段】本実施形態の磁気抵抗素子は、膜面に垂直方向に磁化容易軸を有し、磁化が可変の第1強磁性層と、膜面に垂直方向に磁化容易軸を有し、磁化が不変の第2強磁性層と、第1強磁性層と第2強磁性層との間に設けられた第1非磁性層と、第2強磁性層に対して第1非磁性層と反対側に設けられ、それぞれが異なる発振周波数の回転磁界を発振する強磁性体の複数の発振体を有し、各発振体が膜面に平行な磁化を有する、第3強磁性層と、を備え、第3強磁性層と、第1強磁性層との間に電流を流すことにより、スピン偏極した電子を第1強磁性層に作用させるとともに、第3強磁性層の複数の発振体に作用させて前記発振体の磁化に歳差運動を誘起し、歳差運動によって生じた複数の回転周波数を有し第1強磁性層の磁化反転をアシストする回転磁界が第1強磁性層に印加される。

(もっと読む)

磁気メモリ及びその製造方法

【課題】磁気抵抗素子間での電気的特性のバラツキを低減する。

【解決手段】磁気メモリの製造方法は、半導体基板20上のセルアレイ部に磁気抵抗素子37を形成する工程と、半導体基板20上の周辺回路部に、磁気抵抗素子37と同じ積層構造を有しかつ磁気抵抗素子37と同じレベルに配置されたダミー素子68を形成する工程と、磁気抵抗素子37及びダミー素子68を一括して平坦化する工程と、ダミー素子68にレーザー光線を照射し、ダミー素子68を非磁性体化する工程と、平坦化された磁気抵抗素子37上に上部電極41を形成する工程とを含む。

(もっと読む)

磁気抵抗素子および磁気メモリ

【課題】垂直磁気異方性を有するとともにより大きな磁気抵抗効果を発現することが可能な磁気抵抗素子およびこれを用いた磁気メモリを提供する。

【解決手段】下地層と、下地層上に設けられ、膜面に垂直方向に磁化容易軸を有し、MnxGa100−x(45≦x<64atm%)である磁性体膜を含む第1の磁性層と、第1の磁性層上に設けられた第1の非磁性層と、第1の非磁性層上に設けられ、膜面に垂直方向に磁化容易軸を有し、MnyGa100−y(45≦x<64atm%)である磁性体膜を含む第2の磁性層と、を備え、第1および第2の磁性層のMnの組成比が異なり、第1の非磁性層を介して第1の磁性層と第2の磁性層との間に流れる電流によって、第1の磁性層の磁化方向が可変となる。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 配線の信頼性が劣化しない磁気ランダムアクセスメモリ及びその製造方法を提供することである。

【解決手段】 実施形態に係る磁気ランダムアクセスメモリは、下部電極、磁気抵抗効果素子、上部電極が下層から順に積層された積層膜が設けられる。前記磁気抵抗効果素子、前記上部電極の側面に接し、上面が前記上部電極の上面と実質的に同一の高さであるストッパ層平坦部が設けられる。前記上部電極上にバリアメタル膜が設けられる。前記バリアメタル膜上にコンタクトプラグが設けられる。

(もっと読む)

半導体記憶装置

【課題】半導体基板の表面の空き領域が少ない半導体記憶装置を提供する。

【解決手段】このMRAMの各メモリセルMCは、磁気抵抗素子18と2つのアクセストランジスタ19a,19bを含み、トランジスタ19a,19bのドレインを磁気抵抗素子18を介して対応のビット線BLに接続し、それらのゲートを対応のワード線WLに接続し、それらのソースをそれぞれソース線SLおよび補助配線ALに接続する。したがって、アクセストランジスタ19bのソースとDLドライバ14に含まれるドライバトランジスタ23のソースとを共通化することができ、シリコン基板31の表面の空き領域を減らすことができる。

(もっと読む)

1 - 20 / 176

[ Back to top ]