Fターム[5B018MA23]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | ROMを組込んだメモリシステム (418)

Fターム[5B018MA23]に分類される特許

41 - 60 / 418

データ記憶装置

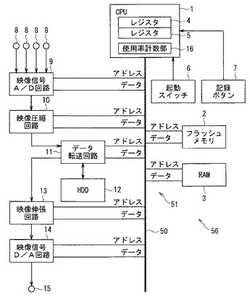

【課題】フラッシュメモリなどのEEPROMにおいて、データ変化を防止する専用の記憶容量を設けなくても、データ変化及びデータ消失の抑制を可能とし、かつ、それに必要な処理能力を抑制することが可能な技術を提供することを目的とする。

【解決手段】監視記録装置56は、CPU1と、フラッシュメモリ2と、RAM3と、CPU1の使用率を計数する使用率計数部16とを備える。CPU1は、フラッシュメモリ2から記憶データを読み出してRAM3に記憶した後、再びRAM3からフラッシュメモリ2の元アドレスに書き戻す上書き処理を行う。CPU1は、この上書き処理を、使用率計数部16で計数された使用率が所定のしきい値よりも低い場合に実行する。上書き処理は他の処理によるフラッシュメモリ2への読み書きが禁止される排他処理とともに実行され、CPU1は、上書き処理を他の処理と時分割で実行する。

(もっと読む)

不揮発性メモリ装置

【課題】信頼性を向上させることができる不揮発性メモリ装置の提供。

【解決手段】メモリセルアレイの選択されたページからデータを読み出すか、或いはメモリセルアレイの選択されたページへ書き込むように構成されたページバッファ回路と、選択されたページに割り当てられたシードに基づいて、ページバッファ回路へ伝送されるか、或いはページバッファ回路から伝送されるデータをランダム化及びデランダム化するように構成されたランダム化及びデランダム化回路と、を有し、選択されたページは複数のセグメントで構成され、ランダム化及びデランダム化回路は、選択されたページに割り当てられたシードに基づいて選択されたページのアクセス要請されたセグメントの各々に対するランダムシークェンスを生成するように構成され、シードにしたがって反復的に生成されたランダムシークェンスに基づいて各アクセス要請されたセグメントのデータをランダム化及びデランダム化するように構成される。

(もっと読む)

半導体装置及びそのデータ異常判定方法

【課題】記憶手段を有する第1チップと、記憶手段に対してメモリデータの読み出しを指示する指示手段、及び、少なくとも多数決により、読み出された制御用データの信頼性を判定する判定手段を有する第2チップと、を備える半導体装置において、データ信頼性を向上しつつ、第2チップの体格増大を抑制する。

【解決手段】制御用データは、記憶先のアドレスの一部に対応するチェック用データが付加されてなるメモリデータとして、1つの制御用データにつき異なる3つのアドレスに記憶される。1つの制御用データに関する各アドレスにおいて、チェック用データに対応する一部を除く部分は、互いに異なるとともに複数の制御用データで同じとされる。また、3つのメモリデータに関し、制御用データ同士、チェック用データ同士、及び該チェック用データに対応するアドレスの一部同士は、それぞれ同じ或いはミラー反転の関係にある。

(もっと読む)

自動車用電子制御装置

【課題】不揮発性メモリの記憶領域に故障が発生しても、情報の蓄積に支障がないようにする。

【解決手段】イグニッションスイッチがOFFになったことを契機として、不揮発性メモリに故障情報を書き込むときに、故障が発生していない記憶領域を選定し(S1)、記憶領域の全領域に消去データを書き込み(S2,S3)、消去データの確認により消去できたか否かを判定する(S4,S5)。記憶領域が消去できなかった場合、故障が発生していない他の記憶領域に素子異常情報を書き込む(S16)。また、イグニッションスイッチがONになったことを契機として、不揮発性メモリから故障情報を読み込むときに、チェックサムを利用して異常を検知し、故障が発生していない他の記憶領域に素子異常情報を書き込む。そして、素子異常情報を計数した計数値が所定の閾値以上である記憶領域は、故障が発生していると判定し、その使用を禁止する。

(もっと読む)

不揮発性メモリへのデータ保存方法および制御装置

【課題】書き換え保証回数内で書き換え頻度を変更し、不揮発性メモリでのデータ記憶の信頼性を向上することができる不揮発性メモリへの保存方法を提供する。

【解決手段】複数のデータを保存し、電気的に上記データの書き換えが可能で、各データの書き込み範囲より大きい所定範囲の単一ブロックを一括でしか消去できない不揮発性メモリ4へのデータの書き換えを行う制御装置100は、複数のデータが、書き換え頻度の高いデータと、書き換え頻度の低いデータとからなり、不揮発性メモリ4の書き換え回数をカウントするカウント部10と、カウント部10にてカウントされた書き換え回数が所定値以上であるか否かを判断する判断部11と、判断部11にて所定値以上と判断されると書き換え頻度の高いデータの書き換え頻度を変更する設定部12とを備える。

(もっと読む)

不良ビットエラーを処理するシステムおよび方法

【課題】半導体不揮発性メモリ装置における不良ビットエラーを補償する。

【解決手段】装置は、メモリ装置120から古いページを受け取り、そのページが不良ビットを有するか否かを決定する不良ビット検出モジュール116を含む。装置は、新しいページを生成する不良ビット修正モジュール118を含む。不良ビット修正モジュール118は、不良ビットの位置を特定し、不良ビットの好適値を決定し、不良ビットのユーザ値を決定する。不良ビット修正モジュール118は、古いページの実質的なデータに対応するビット列に好適値を挿入し、好適値が挿入されたビット列を記録する。不良ビット修正モジュール118は、古いページのアドレスに新しいページを格納する。

(もっと読む)

メモリ制御装置及びメモリ制御方法

【課題】

ウエアレベリングを効率良く、かつ、合理的に行う。

【解決手段】

メモリ利用モジュール900から送られた書き込み要求WRQを受けた場合に、アクセス制御部150が、現在時刻TMD、書き込み対象の候補となったアクセス単位ブロックの現時点における検出エラービット数EBN、並びに、不揮発性メモリ200内の管理領域に記憶されている当該書き込み対象の候補となったアクセス単位ブロックに関する最新書込時刻、及び、最新の書き込み時における検出エラービット数を取得する。引き続き、アクセス制御部150は、これらの取得結果に基づいて、最新の書き込み時から現時点までの検出エラービット数の時間変化率を算出し、算出された時間変化率に基づいて、当該書き込み対象の候補となったアクセス単位ブロックが、不揮発性メモリ200に関する消去回数の平準化のために利用できるか否かを判定する。

(もっと読む)

電子制御装置

【課題】フラッシュメモリのデータ消去中或いはデータ書込み中に、フラッシュメモリのデータ消去動作或いは書込み動作を中断させるような事象が発生した場合でも、適切なバックアップ動作を継続可能な電子制御装置を提供する。

【解決手段】揮発性メモリと、フラッシュメモリと、前記揮発性メモリに保存されているバックアップデータを所定条件の成立をトリガとして前記フラッシュメモリに保存するメモリ制御部とを備える電子制御装置であって、前記メモリ制御部は、電源投入時において、前記フラッシュメモリの消去単位ブロックの内、データが全く保存されていない消去単位ブロックをブランクブロックとして特定し、前記ブランクブロックを基準として消去すべき消去単位ブロックを消去ブロックとして特定すると共に最新データが保存されている消去単位ブロックを最新ブロックとして特定する。

(もっと読む)

メモリシステムおよびメモリシステムの制御方法

【課題】信頼性を向上したメモリシステムを提供する。

【解決手段】実施形態のメモリシステム1は、ブロックを複数有する不揮発性メモリ2と、キャッシュ3と、ホスト7が指定する論理アドレスと不揮発性メモリ上のデータ位置を指定する物理アドレスの対応を示す論物変換テーブルと、論物変換テーブルに対応する論理アドレスを有するブロック毎の消去回数を保持する消去回数テーブルを備える。メモリシステムは、ホストが削除対象となる論理アドレスを通知した場合に、論物変換テーブルにてそれに対応する物理アドレスが指定する削除対象領域を含む削除対象ブロックの消去回数を取得し、当該消去回数の所定の割合以下の消去回数を有する少消去ブロックが消去回数テーブルに存在する場合には、少消去ブロック内の有効データのキャッシュへの読み出しおよび削除対象領域への書き込みを実行し、少消去ブロック内の有効データを無効化するコントローラ6を備える。

(もっと読む)

メモリシステム

【課題】書き換え回数制限下での実効的な書き換え容量を増大したメモリシステムを提供する。

【解決手段】実施形態のメモリシステム1は、2ビット以上の所定ビット数の記憶容量のメモリセルを複数個有する不揮発性メモリ2と、前記メモリセルの書き換え回数を管理する書き換え回数管理テーブル40を備える。実施形態のメモリシステムは、ホスト7からの書き込み要求に応じたビット数で前記メモリセルに書き込みを行い、前記書き換え回数管理テーブル40が管理する前記メモリセルの書き換え回数が所定の回数を超えた後は、前記メモリセルを前記記憶容量に依存したグループに分割し、ホストからの書き込み要求に応じたビット数の前記記憶容量に対応する前記グループの前記メモリセルに書き込みを行うコントローラ3を備える。

(もっと読む)

メモリ書き込み確認装置、メモリ書き込み確認方法およびプログラム

【課題】データの正常性だけでなく、書き込みアドレスの正常性も確認する。

【解決手段】書き込み部11は、メモリ12にデータを書き込み、計算部13は、書き込み部11がメモリ12に書き込んだデータのデータ・チェックサム値とデータを書き込んだアドレスのアドレス・チェックサム値とを計算し、データ・チェックサム値とアドレス・チェックサム値を合計したチェックサム合計値を計算する。表示部14は、データ・チェックサム値とチェックサム合計値を表示する。

(もっと読む)

メモリの制御方法、メモリの制御回路、記憶装置、及び電子機器

【課題】消去回数を低減すること。

【解決手段】制御回路22は、メモリセルの状態を書き込み状態から消去状態に変更する「1変更データ」がライトデータ列WDTに含まれるか否かを判定する。ライトデータ列WDTに「1変更データ」が含まれる場合、制御回路22は、ライトデータ列WDTから、「1変更データ」ではない位置のデータをメインセクタMSmに書き込み、「1変更データ」である位置のデータを論理反転して補助セクタMSsに書き込む。

(もっと読む)

メモリシステム及びメモリコントローラ

【課題】処理内容の判別が可能なメモリシステムを提供する。

【解決手段】実施形態に係るメモリシステムは、外部からの入力データにパリティ情報を付加させた記憶データを記憶する複数のメモリセルを有するメモリデバイスと、前記入力データ及び前記記憶データ間の変換を行うメモリコントローラとを備え、前記記憶データに含まれる前記入力データに対応する情報データは、前記入力データに対して非線形の関係にあることを特徴とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】リードディスターブを効率良く回避するための技術を提供する。

【解決手段】不揮発性半導体記憶装置(1)は、不揮発性記憶部(11)と、上記不揮発性記憶部の消去単位とされるブロック毎のデータを、当該ブロックとは異なるブロックに書き直すためのリフレッシュ処理を制御可能なコントローラ(12)とを含む。上記コントローラは、上記不揮発性記憶部に、第1領域とそれとは異なる第2領域とを設定し、上記第1領域のデータについてのリフレッシュ頻度が、上記第2領域のデータについてのリフレッシュ頻度に比べて高くなるように、リフレッシュトリガが発生される毎に上記第1領域及び上記第2領域についてのリフレッシュ処理を実行する。これにより、リードアクセスが繰り返される場合のリードディスターブを効率良く回避することができる。

(もっと読む)

マルチチャネルを有するメモリ装置及び同装置におけるメモリアクセス方法

【課題】ブロック単位のメモリアクセス処理を、小容量のメモリ領域を用いた管理で高速に実行できるようにする。

【解決手段】実施形態によれば、コマンド生成手段は所定のアクセス処理において、チャネル別のアクセスコマンドの群をメモリインタフェースに逐次投機的に投入する。パージ手段は、複数のチャネルを介してのメモリアクセスのいずれかでエラーが発生した場合、既に投入されている未実行のアクセスコマンドの系列を返却する。コマンド進捗管理手段は、各チャネルにおけるコマンド進捗が、返却された未実行のアクセスコマンドの系列のうちの最も古い未実行のアクセスコマンドの指定する位置を指すようにコマンド進捗情報を更新する。コマンド生成手段は更新された情報に基づき、チャネル別のアクセスコマンドの群をメモリインタフェースに投入する。

(もっと読む)

データリテンション動作を実行する使用者装置、データ格納装置、及びそれのデータリテンション方法

【課題】グローバルタイムを参照してデータリテンション動作を実行する使用者装置、格納装置、及びそれのデータリテンション方法を提供する。

【解決手段】本発明のデータ格納装置の駆動方法は、データ格納装置をオフライン状態でオンライン状態に転換する段階と、オンライン状態の間にホストから現在のグローバルタイム(Global time)を受信する段階と、オンライン状態の間に現在のグローバルタイム(Current global time)を参照してデータ格納装置に格納されたデータを少なくとも1つのノーマルデータリテンション動作を通じてリフレッシュする段階と、を含む。

(もっと読む)

メモリコントローラ

【課題】エラー訂正処理時間の短縮、消費電力の削減、およびエラー訂正用データの削減を図る。

【解決手段】メモリインターフェイスと、ホストからのコマンドに従ってメモリインターフェイスを制御する制御部と、を具備し、メモリインターフェイスは、メモリへの書き込みが2値書き込みの場合、データに対してiビットの第1エラー訂正ビット数を設定し、多値書き込みの場合、データに対してjビット(i<j)の第2エラー訂正ビット数を設定するエラー訂正ビット数設定部161と、エラー訂正ビット数設定部により、第1エラー訂正ビット数が設定された場合、kバイトの第1エラー訂正コードを生成してデータに付加し、第2エラー訂正ビット数が設定された場合、l(k<l)バイトの第2エラー訂正コードを生成してデータに付加するエラー訂正コード生成付加部162と、を備える。

(もっと読む)

メモリシステムおよびその動作方法

【課題】動作速度を低下させることなくシステムの信頼性を向上させることが可能なメモリシステムおよびその動作方法を提供する。

【解決手段】不揮発性メモリシステム2は、ブロック(ページ)単位でデータのアクセスが行われるNAND型フラッシュメモリ21(第1の不揮発性メモリ)と、ワード単位でデータのランダムアクセスが行われるNVRAM22(第2の不揮発性メモリ)と、NAND型フラッシュメモリ21およびNVRAM22の動作の制御を行うNVMコントローラ23(制御部)とを備えている。NVRAM22のデータに適用されるエラー訂正コードECC2が、NAND型フラッシュメモリ21内に保持されている。NVRAM22に対するアクセス速度の低下が回避されつつ、このNVRAM22におけるデータ保持特性が改善される。

(もっと読む)

動的ECC符号化率調節方法、装置、およびシステム

【課題】誤り制御符号化(ECC)の符号化率の動的調節方法、装置、およびシステムを提供する。

【解決手段】ビット誤り率モニタ106は、ECCエンジン104から受信した訂正不能コードワード信号に少なくとも部分的に基づいて、ビット誤り率を動的に決定する。ビット誤り率に基づいて、符号化率変更トリガがECCエンジン104へ送られ、所定の所望の範囲内に出力誤り率を維持するには符号化率を増減させる。ビット誤り率の変更に呼応して、誤り制御符号化の符号化率(ECC符号化率)を、第1の符号化率から第2の符号化率へ変更する段階を備える。

(もっと読む)

電子機器および記憶方法

【課題】 低コストのフラッシュメモリの使用によるコスト低減を可能にし、更には、処理の高速化や、フラッシュメモリの寿命延長を図ることもできる電子機器を提供すること。

【解決手段】n個のデータブロックのマップ番号を書き換え候補番号に設定して、該書き換え候補番号をマップ番号として持つ記憶ブロックがフラッシュメモリ上に複数存在するか否かを判定する候補ブロック判定処理を実施し、候補ブロック判定処理で、書き換え候補番号に一致するマップ番号の記憶ブロックがフラッシュメモリ上に複数存在すると判定された時には、該当する複数個の記憶ブロックの内から、更新日時が最も古い記憶ブロックを書き込みブロックに決定して、該記憶ブロックにRAM上の該当データブロックを書き込む。

(もっと読む)

41 - 60 / 418

[ Back to top ]