Fターム[5B018MA23]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | ROMを組込んだメモリシステム (418)

Fターム[5B018MA23]に分類される特許

81 - 100 / 418

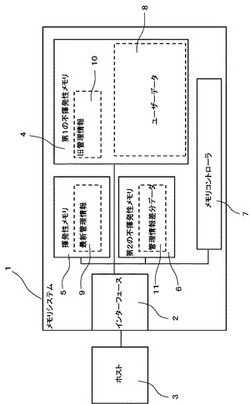

メモリシステム

【課題】 小容量の不揮発性メモリを効率的に利用することで異常電源断からの復元が可能なメモリシステムを提供する。

【解決手段】 実施形態に係るメモリシステムは、揮発性メモリを持つ。前記揮発性半導体メモリには、第1の不揮発性メモリが接続される。前記揮発性半導体メモリには、第2の不揮発性メモリが接続される。前記揮発性メモリに最新管理情報を記憶し、前記第1の不揮発性メモリに旧管理情報を記憶し、および前記第2の不揮発性メモリに前記最新管理情報と前記旧管理情報の差分データを記憶するメモリコントローラが設けられる。

(もっと読む)

記憶装置及び画像形成装置

【課題】記憶領域のシフト方向を管理する。

【解決手段】記憶装置は、有効記憶領域に記憶されている分割データを無効記憶領域に書き直すとともに、書き直し先の無効記憶領域に対応する第2の記憶領域に有効フラグを設定し、書き直し元の有効記憶領域に対応する第2の記憶領域に無効フラグを設定することで複数の第1の記憶領域における無効記憶領域の位置をシフトしながらデータのリード回数が第1の記憶部のリード限界回数に達するまでに全ての分割データの書き直しを完了し、識別フラグに基づいて無効記憶領域のシフト方向を判定する記憶制御手段とを具備する。

(もっと読む)

記憶装置、ホスト装置、回路基板、液体容器及びシステム

【課題】書き込み不要なデータを非書き込みとし、書き込み処理時間を短縮することができる記憶装置、ホスト装置、回路基板、液体容器及びシステム等を提供すること。

【解決手段】記憶装置100は、ホスト装置400との通信処理を行う制御部110と、ホスト装置400からのデータが書き込まれる記憶部120と、記憶部120のアクセス制御を行う記憶制御部130とを含む。制御部110は、ホスト装置400からコマンドパケット及びデータパケットを受信し、データパケットの書き込みイネーブルビットが書き込み許可状態に設定されている場合には、アドレス情報の更新指示を行うと共に、データパケットのデータの書き込み指示を行い、書き込みイネーブルビットが書き込み非許可状態に設定されている場合には、アドレス情報の更新指示を行う一方で、データパケットのデータの書き込み指示を行わない。

(もっと読む)

電子装置、及び、これを用いた電動パワーステアリング装置

【課題】アドレスバスおよびデータバスの故障を検出する電子装置において、故障検出に係る処理負荷を低減し処理速度を向上する。

【解決手段】電子装置は、CPUとROMとを接続しアドレスを伝送する4つ以上のバスラインからなるアドレスバス21を備える。電子装置は、アドレスバス検査用アドレスAdによって指定されるROM領域13aから値を読み出し、読み出した値から計算した判定値Vjと予め計算されたアドレスバス検査用正解値Vtとを比較し、一致しない場合、アドレスバス21が故障していると判定する。アドレスバス検査用アドレスAdは、4つ以上のバスラインに対応する4ビット以上の値であって、2ビット以上の0の値と2ビット以上の1の値とを有する値を含み、複数のバスライン間の短絡故障を同時に検出可能である。これにより、故障検出に必要な検査用アドレスAdの数を低減することができる。

(もっと読む)

電子機器

【課題】多値書込フラッシュメモリの活用されていないエリアを使用し、データ領域内の退避領域を不要とする。

【解決手段】コントローラ10は、多値書込フラッシュメモリ6のデータ領域への新規データ書込時には、先ずこの新規データの書込先アドレスを決定し、次に前記新規データの書込先アドレスに対応するデータ領域のアドレスに書込済データが存在するか否かを検出し、前記書込先アドレスに対応するアドレスに書込済データが存在すると判断した時には、前記書込済データのコピーをFAT予約領域に書込み、その後、前記新規データをFAT予約領域に書込み、次に、FAT予約領域に存在する新規データと前記書込済データをデータ領域に書込む構成とした。

(もっと読む)

半導体装置

【課題】フラッシュメモリ等の不揮発性メモリの誤書き込み、誤消去を防止する半導体装置を提供する。

【解決手段】内部リセット信号を正論理で保持するレジスタと負論理で保持するレジスタとを複数設け、これらの出力信号と、外部リセット信号とを入力し、これらの信号のいずれかがリセット状態である場合に活性化し、これらの信号のいずれもリセット状態でない場合に非活性化するメモリリセット信号を出力するメモリリセット信号を出力するメモリリセット信号生成回路と、メモリリセット信号を入力し、メモリリセット信号が活性化しているときにリードライトアクセス、消去動作が禁止される不揮発性メモリと、を備える。

(もっと読む)

電子機器、制御方法及びプログラム

【課題】BIOSデータがOS起動中に破壊されてしまっても、そのBIOSデータを復元することが可能な電子機器を提供する。

【解決手段】 本実施形態の電子機器(100)は、電源(15)が投入された際に、データを記憶する第1の記憶手段(12)に格納されているBIOSデータを、第1の記憶手段(12)とは異なる第2の記憶手段(13)にコピーし、OSを終了する際に、第1の記憶手段(12)に格納されているBIOSデータと、第2の記憶手段(13)にコピーしたBIOSデータと、を比較し、双方のBIOSデータが異なる場合は、第2の記憶手段(13)にコピーしたBIOSデータを、第1の記憶手段(12)にコピーする。

(もっと読む)

ビデオサーバ、管理情報キャッシュ方法及び管理情報キャッシュプログラム

【課題】 管理情報を半導体記録メディアに記録する場合であっても、長期の運用に耐えることが可能なビデオサーバと、このビデオサーバで用いられる管理情報キャッシュ方法及び管理情報キャッシュプログラムとを提供する。

【解決手段】 素材データを符号化データに変換する符号化部と、前記符号化データを記録する記録部と、前記符号化部及び前記記録部を制御すると共に、前記素材データの管理情報を管理する制御部とを具備するビデオサーバにおいて、前記制御部は、メモリ、CPU、キャッシュメモリ及び接続インタフェースを備える。CPUは、メモリに記録される操作履歴に基づいて、前記管理情報が変更される可能性が高いか否かを判断し、高いと判断した場合、キャッシュメモリに管理情報を一時的に記録し、低いと判断した場合、管理情報を接続インタフェースに接続される半導体記録メディアに書き込む。

(もっと読む)

データ修復装置

【課題】同一のデータが書き込まれた全ての領域に破壊された部分が存在する場合においても、破壊されたデータを修復すること。

【解決手段】CPU1は、全ての領域R0〜RNの同一オフセットアドレスのワードデータを1ワード分だけフラッシュROM6から読み出し、ワードデータが同じならば次の1ワード分のワードデータを読み出し、ワードデータが1個でも異なるならば、全ての領域R0〜RNのワードデータをマージすることでワードデータを再構築する。

(もっと読む)

不揮発性半導体記憶装置、及び、メモリシステム

【課題】データ保持特性を向上することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、複数のメモリセルをそれぞれ含む複数のブロックを有し、前記複数のブロックのうちの通常ブロックに、通常のデータが記憶され、前記複数のブロックのうちのタイムコードブロックに、前記通常ブロック毎に設定され且つ前記通常ブロックの最後の書き込み動作を実行した時間に対応する時間データを含むタイムコードが記憶されたメモリセルアレイを備える。前記不揮発性半導体記憶装置は、前記タイムコードブロックから前記タイムコードを読み出し、現在の時間を取得し、読み出された前記タイムコードの時間データの時間と前記現在の時間との時間差が規定値よりも大きくなる選定された前記通常ブロックに対して、データを読み出し、消去し、且つ、読み出されたデータを書き込み、前記現在の時間の時間データに対応する新たなタイムコードを、選定された前記通常ブロックに対応させて、前記タイムコードブロックに書き込む。

(もっと読む)

記憶装置、回路基板、液体容器及びシステム

【課題】記憶されたデータにエラーが生じた場合でも、正しいデータを書き込むことができる記憶装置、回路基板、液体容器及びシステム等を提供すること。

【解決手段】記憶装置100は、ホスト装置400との通信処理を行う通信部110と、ホスト装置400からの受信データ及びメモリー領域選択情報を記憶する、第1、第2のメモリー領域MA1、MA2とを有する記憶部120と、第1、第2のメモリー領域MA1、MA2のいずれか一方を読み出し用メモリー領域として選択し、他方を書き込み用メモリー領域として選択して、読み出し及び書き込み制御を行うメモリー制御部130と、メモリー制御部130により読み出し用メモリー領域から読み出されたデータの値と受信データの値との大小関係を比較するインクリメント判断部140とを含む。

(もっと読む)

メモリコントローラ及びメモリコントローラを備える不揮発性メモリシステム、並びに不揮発性メモリの制御方法

【課題】物理ページ(PP)を複数個含む物理ブロック(PB)からなる不揮発性メモリにおける論理ページ(LP)とPPの対応関係を、それぞれのPPに簡易な情報を書き込むことにより管理する。

【解決手段】PB内の先頭のPBから末尾のPPに向かう書き込み順序で、データが書き込まれると共に、当該データが書き込まれたPPに、先頭のPPから当該PPまでのそれぞれのPPに対応するLPを示す情報を含むページ管理情報が書き込まれる。それぞれのLPに対応する最新のデータが書き込まれているPPを特定するときに、PBに書き込まれているページ管理情報のうち、書き込み順序が後のPPに書き込まれているページ管理情報が優先的に参照される。ページ管理情報に含まれる情報は所定の配列順序で配列されており、同じLPを示す情報が複数個あるときは、配列順序が後の情報が優先される。

(もっと読む)

記録ユニット及び故障チップ特定方法

【課題】 誤り訂正符号の誤り訂正能力を超えてエラーが発生した場合であっても、故障したメモリチップを特定することが可能な記録ユニット及び故障チップ特定方法を提供する。

【解決手段】 記録ユニットは、記録部、誤り検出符号付加部、書込み用バッファメモリ、誤り訂正符号付加部及びメモリコントローラを具備する。記録部は、所定の書込み容量単位でデータを書き込み可能な複数のメモリチップを備える。誤り検出符号付加部は、受信したデータストリームの所定容量のデータセグメント毎に誤り検出符号を付加する。書込み用バッファメモリは、誤り検出符号付加部からのデータストリームを一時的に保持して出力する。誤り訂正符号付加部は、書込み用バッファメモリからのデータストリームに誤り訂正符号を付加する。メモリコントローラは、データブロック及び誤り訂正符号が複数のメモリチップに並列して書き込まれるように制御する。

(もっと読む)

メモリシステム

【課題】頻繁に書き換えを行うデータ領域と殆ど書き換えを行わないデータ領域とが混在するデータを格納している際にも最適なウェアー・レベリング制御が可能で、システムの書き換え回数の実効的な寿命を大幅に改善することが可能なメモリシステムを提供する。

【解決手段】制御部は、特定物理アドレスブロックに書き換えが集中しないウェアー・レベリング(Wear-leveling)制御を行う際、書き換えを行わない物理アドレスブロックは、そのまま放置しておくパッシブ・ウェアー・レベリング制御と、書き換えを行わない物理アドレスブロックも全ての物理アドレスブロックの書き換え回数が平均化されるように書き換えを行うアクティブ・ウェアー・レベリング制御とが可能であり、不揮発性メモリ部には、パッシブ・ウェアー・レベリング制御およびアクティブ・ウェアー・レベリング制御の方式選択、若しくは、両ウェアー・レベリングの条件設定値が格納されている。

(もっと読む)

電子機器およびそのプログラム起動制御方法

【課題】不揮発性メモリからプログラムを読み出して電子機器を起動する場合の信頼性を向上させるプログラム起動制御方法および電子機器を提供する。

【解決手段】電子機器は、表示部12と、操作部13と、起動するための同一の起動用プログラムを格納した複数のNANDフラッシュメモリ102,103とを有し、メモリ102から読み出した第1起動用プログラムのデータ誤りを検出すると(S203;Y)、メモリ103から第2起動用プログラムを読み出し(S204)、第1起動用プログラムを第2起動用プログラムで書き換えるか否かの選択メッセージを表示部12に表示させ(S205)、操作部13を通して書き換えが選択されると(S206;Y,S207;Y)、書き換えを実行する(S208−S211)。

(もっと読む)

電子装置およびデータ記録制御方法

【課題】書き込み回数に制限のあるメモリカードを記録媒体として使用する場合、書き込み回数が制限回数を超えたとき、当該メモリカードに記録されているデータの破損を確実に防止しつつ、その後に発生するデータの書き込みを継続することが可能な「電子装置およびデータ記録制御方法」を提供する。

【解決手段】第2の不揮発性メモリ180におけるデータの書き込み回数が所定回数以上である場合、第1の不揮発性メモリ160に対してデータの書き込みを許可し、第2の不揮発性メモリ180に対してデータの書き込みを禁止する設定を行い、その後の書き込み要求に対し第1の不揮発性メモリ160に書き込みを行うように制御することにより、データが破損する可能性の高い状態で第2の不揮発性メモリ180に対するデータの書き込みが行われず、新規に保存する必要のあるデータを第1の不揮発性メモリ160に書き込み続けられるようにする。

(もっと読む)

半導体記憶装置、制御装置、及び半導体記憶装置の制御方法

【課題】不揮発性メモリの記憶領域を消費することなく、読み出し不能なデータを管理できる半導体記憶装置、制御装置、及び半導体記憶装置の制御方法を提供する。

【解決手段】半導体記憶装置は、データを記憶する不揮発性メモリと、前記不揮発性メモリへのデータの書き込みと前記不揮発性メモリからのデータの読み出しとを制御する制御部とを備え、前記制御部は、データが有効であるのか無効であるのかを示す第1のフラグをデータに付加して誤り訂正処理を行うことにより生成された誤り訂正符号を前記データに付加して前記不揮発性メモリへ書き込む書き込み制御部と、前記データと前記誤り訂正符号とを前記不揮発性メモリから読み出し、有効及び無効の何れか一方に固定された第2のフラグを前記読み出されたデータに付加し、前記読み出された誤り訂正符号を用いた誤り訂正処理を前記第2のフラグが付加されたデータに対して行う読み出し制御部とを有する。

(もっと読む)

半導体メモリ装置および半導体メモリシステム

【課題】製品寿命の長い半導体メモリ装置を提供する。

【解決手段】半導体メモリ装置2は、書き替え頻度が高い第1の領域と、書き替え頻度が低い第2の領域と、フリーブロック領域と、に分類される半導体メモリ部30と、所定のタイミングで、第2の領域のブロックに記憶されたデータをフリーブロック領域の最上位エントリのブロックにコピーするとともに、データが記憶されていたブロックを前記第2の領域から解放してフリーブロック領域の最下位にエントリするように制御するメモリコントローラ10と、を具備する。

(もっと読む)

メモリコントローラ、メモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】チャンネル毎に設けられた複数個のシンドローム計算回路と共用される1個の誤り訂正回路を用いてフラッシュメモリから読み出されたデータを復号化するときに、複数個のシンドローム計算回路から誤り訂正回路への復号化処理の引継ぎを円滑に行うこと。

【解決手段】各チャンネルを介して読み出されたデータに基づいてシンドロームを算出する算出処理が、チャンネル毎に独立して実行され、算出されたシンドロームはキューに保持される。この際、キュー内のそれぞれのキュー領域には、そのキュー領域に対応するバッファメモリ内の領域に保持されているデータに対応するシンドロームが保持される。そして、バッファメモリ内のそれぞれの領域に保持されているデータに対するビットエラーの訂正は、そのデータが保持されている領域に対応するキュー領域に保持されているシンドロームに基づいて行われる。

(もっと読む)

メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】バーストエラーが発生したために、読み出されたデータに含まれる全てのビットの論理値が、“1”又は“0”になったときに、そのバーストエラーの発生を高い確率で検出すること。

【解決手段】ビットエラーを訂正するためのECCに符号化されたデータと共に、論理値0のビットと論理値1のビットの双方を複数ビットずつ含む整合性符号をフラッシュメモリ内のページに書き込む。そして、そのデータをフラッシュメモリから読み出したときに、そのデータ及びそのデータと共に書き込まれた整合性符号に含まれる全てのビットが論理値0のビットであるとき、又は、その全てのビットが論理値1のビットであるとき、ECCに基づいて訂正不能エラーの発生が検出されなかった場合でも、訂正不能エラーが発生したと判断し、ホストシステムにその旨を通知する。

(もっと読む)

81 - 100 / 418

[ Back to top ]