Fターム[5B018MA23]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | ROMを組込んだメモリシステム (418)

Fターム[5B018MA23]に分類される特許

61 - 80 / 418

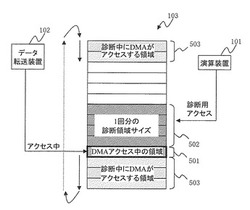

組込制御装置

【課題】DMA装置を停止させることなく、データ整合性を維持しつつ記憶装置のデータ整合性診断を簡易な構成で実施することのできる組込制御装置を提供する。

【解決手段】データ転送装置102が記憶装置103にデータを書き込み、またはデータを読み取っている記憶領域501のアドレスは、データ転送装置102が備えるレジスタに格納されている。演算装置101は、そのレジスタから記憶領域501のアドレスを知ることができるので、これを避けてデータ整合性診断を実施する。

(もっと読む)

NORフラッシュメモリの読み取り方法

【課題】NORフラッシュメモリの読み取り方法を提供する。

【解決手段】

本発明は、NORフラッシュメモリの読み取り方法を提供し、組込み式Linuxオペレーションシステムで使用され、巡回冗長検査値を照合し、カウンタに予め設けられた繰り返し読み取り回数の閾値により、ジャーナリングファイルシステムデータの繰り返し読み取りを継続するか否かを決定する。

(もっと読む)

メモリシステムおよびその制御方法

【課題】読み出しの処理時間を短縮することができるメモリシステムを得ること。

【解決手段】データと、2段階以上の誤り訂正処理により段階毎に定義された所定のサイズの前記データである単位データ毎に生成された各段階の誤り訂正符号と、を記憶する半導体記憶部、を備える。そして、半導体記憶部から読み出されたデータと当該データに対応する前記各段階の誤り訂正符号とに基づいて誤り訂正処理を行う誤り訂正処理部と、誤り訂正処理部による誤り訂正処理により誤り訂正が不可であったか否かを示す段階毎の誤り訂正履歴情報を前記単位データ毎に記憶する誤り訂正履歴情報記憶部と、を備える。さらに、読み出し対象の単位データに対応する前記誤り訂正履歴情報が訂正不可である段階の誤り訂正処理を実施せずに次段階の誤り訂正処理を実施するよう誤り訂正処理部を制御する。

(もっと読む)

電気機器

【課題】電源が供給された際に復元すべきデータを保存する際の負担を軽減することができる、電気機器を提供することを、目的とする。

【解決手段】不揮発性メモリ34に記憶されている復元すべきデータと、揮発性メモリ18に記憶されている復元すべきデータとを直接比較せずに、不揮発性メモリ34に記憶されている復元すべきデータについての現状チェックデータと、揮発性メモリ18に記憶されている復元すべきデータについての確認チェックデータとを比較して、不揮発性メモリ34に記憶されている復元すべきデータと、揮発性メモリ18に記憶されている復元すべきデータとが一致するか否かを判定する。

(もっと読む)

半導体記憶装置

【課題】 各種のデータ転送が可能な半導体記憶装置を提供する。

【解決手段】 メモリセルアレイ10は、複数の不揮発性メモリセルが配置されている。RAM(Random Access Memory)30は、メモリセルアレイ10に書き込まれるデータ、又は読み出されたデータを保持する。制御部4は、RAMを用いた第1の動作モードと、RAMを用いない第2の動作モードを制御する。データ転送部17は、第2の動作モードにおいて、データの書き込み時、データバスDIRを介して入出力部40から供給されたデータをバッファ部12に転送し、バッファ部12に転送されたデータをエラー訂正部20に転送し、エラー訂正部20において、生成されたパリティデータをバッファ部12に転送する。

(もっと読む)

メモリ・バックアップのための電力分離

【課題】電力分離およびバックアップ・システムを開示すること。

【解決手段】電源異常状態が検出される時に、一時ストレージをSDRAMにフラッシュする。フラッシュの後に、インターフェースを停止し、電力を、SDRAMサブシステムを除くチップの大半から除去する。SDRAMサブシステムは、データをSDRAMからフラッシュ・メモリにコピーする。その途中で、データを暗号化し、かつ/またはデータ完全性署名を計算することができる。データを復元するために、SDRAMサブシステムは、データをフラッシュ・メモリからSDRAMにコピーする。その途中で、復元されるデータを暗号化解除し、かつ/またはデータ完全性署名をチェックすることができる。

(もっと読む)

データ転送装置、メモリ制御装置、およびメモリシステム

【課題】誤り訂正が発生したとしてもデータ伝送が待たされる時間を少なくし、データ転送に要する時間を短縮することが可能なデータ転送装置、メモリ制御装置、およびメモリシステムを提供する。

【解決手段】データ転送元の第1メモリ装置200の第1メモリアドレスと、データ転送先の第2メモリ装置の第2メモリアドレスと、転送データに誤りが検出されたか否かを示す誤り信号と、誤り訂正が完了して第2メモリ装置106に格納しているデータが有効であるか否かを示す有効信号を記憶する領域を複数含むデータ情報記憶領域109と、第2メモリ装置に格納しているデータのうち、データが有効であるメモリのアドレスである第2メモリ有効アドレスを出力し、第2メモリ装置の第2メモリ有効アドレスからデータを読出し、読出したデータと共に、第2メモリ有効アドレスに対応する第1メモリ装置のアドレスを転送する制御部108とを有する。

(もっと読む)

メモリシステム

【課題】不正な電源断やデータ破壊を簡便かつ確実に検出することが可能なメモリシステムを提供する。

【解決手段】実施形態のメモリシステムは、揮発性の第1の記憶部と、不揮発性の第2の記憶部と、データ管理部と、復元制御部と、を備える。前記データ管理部は、前記第1の記憶部に記憶されている前記管理テーブルの更新前後の差分情報である差分ログを並列書き込み処理によって多重化して前記第2の記憶部に記憶させた後、書き込み単位分の所定データを最終書き込み単位分データとして多重化して前記第2の記憶部に記憶させる。前記復元制御部は、前記第2の記憶部に記憶された差分ログおよび前記最終書き込み単位分データのデータ記憶状態に基づいて、前記差分ログを前記第2の記憶部に記憶させる際に不正電源断が発生したか、または前記第2の記憶部でデータ破壊が発生したかの状態判断をシステム起動時に行う。

(もっと読む)

メモリシステム

【課題】メモリセルの状態を安定させることで信頼性を向上させることが可能なメモリシステムを提供する。

【解決手段】実施形態のメモリシステム1は、ワード線当たりのメモリセル群がn(n≧2)ページ分の記憶容量を有する不揮発性メモリと、ホストが指定する論理アドレスと前記不揮発性メモリ上のデータの位置を指定する物理アドレスとの対応を示すアドレス変換テーブルを管理するランダムアクセスメモリと、前記アドレス変換テーブルを前記ランダムアクセスメモリから前記不揮発性メモリにコピーするデータ確定処理を実行する前に、同一のワード線に対応する前記nページへの書き込みの書き込み順序におけるページ数単位での最大距離以上のページ分のダミーデータを、有効データを書き込んだ前記不揮発性メモリに引き続き書き込むメモリコントローラとを備える。

(もっと読む)

列車情報管理装置および多数決処理方法

【課題】CPUの負荷を増大させることなく多数決演算を実行可能な列車情報管理装置および多数決処理方法を得る。

【解決手段】少なくとも3つのフラッシュメモリ3a〜3cと、全てのフラッシュメモリ3a〜3cにアクセスする第1のアドレスが割り当てられたCPU1と、CPU1から出力された第1のアドレスを検知したとき、第1のアドレスと各フラッシュメモリ3a〜3cに対応する第2のアドレスとを区別して、第2のアドレスに対応する同一のデータを各フラッシュメモリ3a〜3cから読み出し、読み出されたデータ同士が一致するか否かの多数決結果をCPU1へ通知するPLD2とを備える。

(もっと読む)

情報処理装置及び情報処理装置におけるデータ管理方法

【課題】電源オン/オフの際に、ブロックを分割した複数のデータ領域のうち読出し元及び書込み先のデータ領域を比較的簡単に特定できる情報処理装置及情報処理装置におけるデータ管理方法を提供する。

【解決手段】フラッシュメモリー装置の2つのブロックA,Bは、それぞれ1つの管理領域と複数のデータ領域とに分割され、管理領域にはROM状態とブロック状態と選択領域の各情報が格納される。電源オン時のデータ読出し時には、まず各ブロックA,Bの管理領域を読み出す(S11,S12)。管理領域Aのブロック状態が「使用中」であれば選択領域の指すデータ領域からデータを読み出す。一方、「消去可」であればブロックAのデータ消去を行う(S15)。ブロックBも同様に処理される(S17〜S20)。なお、電源オフ時のデータ書込みの際は、ブロックの全てのデータ領域が使い終わると、ブロック状態が「使用中」から「消去可」に変更される。

(もっと読む)

時系列データを保存する情報処理装置および方法

【課題】書き込み可能回数が限られている記憶媒体に時系列データの書き込み回数を均等に分散させる情報処理装置および方法を提供する。

【解決手段】時系列データ毎の保存先アドレス情報と保存先アドレスに前記時系列データを書き込んだ回数情報と保存先アドレスに格納されている前記時系列データの書き込み順序情報からなる管理情報1310、1320を基に不揮発性記憶媒体1200の特定領域にデータ種別に関係なく時系列データを書き込む回数を平準化させる制御部1100を備える。

(もっと読む)

半導体ディスク装置

【課題】複数の半導体ディスク3a、3bによりデータを記録する半導体ディスク装置1において、高信頼性を維持し、処理量およびオーバーヘッドを少なくする。

【解決手段】複数の半導体ディスク3a、3bによりミラーリング構成を成し、一の半導体ディスク3aの任意のアドレスにてセクタエラーを検出したときに、他の半導体ディスク3bから当該アドレスのデータを読み出して、前記一の半導体ディスク3aの前記アドレスに上書きするとともに、バックグラウンドにて一の半導体ディスク3aまたは3bの全アドレスのセクタエラーを検出しセクタエラーが検出されたときは他の半導体ディスク3bまたは3aから当該アドレスのデータを読み出して前記一の半導体ディスク3aまたは3bの前記アドレスに上書きするベリファイ動作を全ての半導体ディスクについて行うようにした。

(もっと読む)

データ記憶装置、メモリ制御装置及びメモリ制御方法

【課題】マルチチャネルプログラム方式において、リード・モディファイ・ライト動作が実行される場合でも、ライトフラッシュ処理を効率的に実行できるデータ記憶装置を提供する。

【解決手段】データ記憶装置は、ライト処理モジュールと、リード処理モジュールと、コントローラとを具備する。リード処理モジュールは、通常リードコマンドを処理し、かつリード・モディファイ・ライト動作を実行する場合にRMW用リードコマンドを処理する。コントローラは、フラッシュコマンドを処理する場合に、通常リードコマンドよりもRMW用リードコマンドの処理を優先的に実行するようにリード処理モジュールを制御し、RMW用リードコマンド処理の完了後に移行するリード・モディファイ・ライト動作のRMW用ライトコマンドの処理を含むライトフラッシュ処理をライト処理モジュールに実行させる。

(もっと読む)

複数のアクセスコマンドを並行して実行するメモリ装置及び同装置におけるメモリアクセス方法

【課題】ブロック単位のメモリアクセス処理を、小容量のメモリ領域を用いた管理で高速に実行できるようにする。

【解決手段】実施形態によれば、メモリ装置のメモリインタフェースは、複数のアクセスコマンドに従ってメモリに並行してアクセスする。コマンド生成手段は所定のアクセス処理において、メモリインタフェースに複数のアクセスコマンドを投機的に投入する。アクセスコマンド返却手段は、メモリインタフェースに既に投入済みの、エラー発生時点で未実行のアクセスコマンド群を、対応するパージレスポンスにより返却する。コマンド進捗管理手段は、返却された未実行のアクセスコマンド群のうちの最も古いアクセスコマンドを指すようにコマンド進捗管理情報を更新する。コマンド生成手段は、更新された情報に基づき、返却された未実行のアクセスコマンド群をメモリインタフェースに再投入する。

(もっと読む)

NANDフラッシュ・メモリにおける確率論的多層エラー訂正のためのシステム、方法、およびコンピュータ・プログラム

【課題】メモリからデータを検索するためのシステム、方法、およびコンピュータ・プログラムを提供する。

【解決手段】メモリからデータを検索するためのシステムを含むNANDフラッシュ・メモリにおけるエラー訂正。このシステムは、メモリと通信するデコーダを含む。デコーダは、メモリにおけるページ上に記憶されたコードワードを受信することを含む方法を実行するためのものであり、コードワードは、データおよびこのデータに応じて発生された第1の層のチェック・シンボルを含む。この方法は更に、コードワードが第1の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定することを含み、これに応じて、第2の層のチェック・シンボルを受信する。第2の層のチェック・シンボルは、データの受信に応じて、更にコードワードを含むページよりも前に書き込まれたメモリにおける他のページの内容に応じて発生させる。第2の層のチェック・シンボルに応じてコードワードを訂正する。訂正したコードワードを出力する。

(もっと読む)

記憶装置、及び制御方法

【課題】フラッシュメモリの交換、取り外しに適切に対応する。

【解決手段】実施の形態の記憶装置は、識別情報記憶手段と、位置情報記憶手段と、判定手段と、制御手段と、を備える。識別情報記憶手段は、ホストからのアクセスの対象となる不揮発性メモリを識別する識別情報を複数記憶する。位置情報記憶手段は、不揮発性メモリの不良領域を識別する位置情報を記憶する。判定手段は、自装置に接続されている複数の不揮発性メモリに格納されている識別情報のそれぞれが、識別情報記憶手段に記憶されている複数の識別情報のいずれかと一致するか否かを判定する。制御手段は、判定手段により不揮発性メモリの識別情報が識別情報記憶手段に記憶されている複数の識別情報のいずれも一致しないと判定された場合に、一致しない識別情報で識別される不揮発性メモリに対して、位置情報記憶手段に記憶された不良領域の位置情報の利用を抑止するともに、当該不揮発性メモリに対する、ホストからのアクセスを抑止する。

(もっと読む)

データ記憶の方法及びシステム

【課題】マルチレベルセル(MLC)メモリモジュールを含む耐クラッシュメモリ(CPM)システムを提供する。

【解決手段】プロセッサ112がMLCメモリモジュール114と通信可能に結合されており、プロセッサは、第1のメモリ部分116において、第1のデジタル値を、第1のメモリ部分の各データ記憶セルの第1のレベルに書き込むことと、第1のデジタル値と同じである第2のデジタル値を各データ記憶セルの第2のレベルに書き込むことと、を行うようにプログラムされており、プロセッサは、第1のメモリ部分の各データ記憶セルの各レベルからデジタル値を読み出して、各データ記憶セルに単一のデジタルセル値を決定するようにプログラムされている。

(もっと読む)

同時読み出し及び書き込みメモリ動作を実行する方法及び装置

【課題】特定のデータパーティションに書き込む動作が、同じデータパーティションから読み出す動作の完了まで一時停止(サスペンド)される必要はないメモリデバイスを提供する。

【解決手段】メモリデバイス300のデータパーティション310においてリード・ホワイル・ライト方式の動作を同時に実行する技術は、メモリの個々のデータパーティションのコンテンツに少なくとも部分的に基づいてECCを計算することを含み、メモリのメモリアレイの個々のメモリパーティションの特定の1つの第1の部分の特定のコンテンツを、前記個々のメモリパーティションの前記特定の1つの第2の部分に書き込む間に、読み出すことを具備し、前記読み出すことは、前記個々のメモリパーティションのコンテンツに少なくとも部分的に基づいた誤り訂正符号(ECC)に少なくとも部分的に基づいた前記第1の部分の前記特定の部分を決定する。

(もっと読む)

メモリシステム

【課題】 小容量の不揮発性メモリを効率的に利用することで異常電源断からの復元が可能なメモリシステムを提供する。

【解決手段】 実施形態に係るメモリシステムは、揮発性メモリを持つ。前記揮発性半導体メモリには、第1の不揮発性メモリが接続される。前記揮発性半導体メモリには、第2の不揮発性メモリが接続される。前記揮発性メモリに最新管理情報を記憶し、前記第1の不揮発性メモリに旧管理情報を記憶し、および前記第2の不揮発性メモリに前記最新管理情報と前記旧管理情報の差分データを記憶するメモリコントローラが設けられる。

(もっと読む)

61 - 80 / 418

[ Back to top ]