Fターム[5B046BA03]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 回路設計 (1,280)

Fターム[5B046BA03]に分類される特許

41 - 60 / 1,280

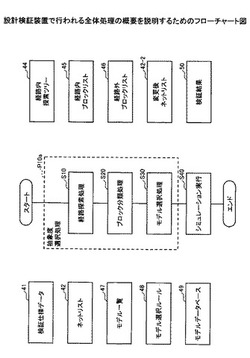

設計検証方法及びプログラム

【課題】 本発明の課題は、検証仕様に従った経路探索の結果を用いて、経路外のブロックの動作の抽象度を変更することにより高速にかつ適切にシミュレーションを行えるようにすること。

【解決手段】 上記課題は、コンピュータによって実行される設計検証方法であって、複数のブロックで構成される回路の検証に係る端子情報に基づいて、記憶部に格納されたネットリストを参照することによって、該ブロック間の接続関係に従って経路を探索し、前記ネットリスト内に記述される、前記探索された経路外のブロックの動作の抽象度を変更することを特徴とする設計検証方法により達成される。

(もっと読む)

半導体集積回路の設計方法

【課題】アナログ回路動作で発生するトランジスタ劣化による特性変動を正確に予測できるようにする。

【解決手段】半導体集積回路に含まれるトランジスタを抽出した後、抽出されたトランジスタのゲート絶縁膜に印加される電界強度の大きさに基づいて、当該トランジスタに適用するストレスバイアス条件を分類する。次に、前記ストレスバイアス条件の分類に応じて、前記トランジスタの劣化後の特性を求めた後、当該劣化後のトランジスタ特性を用いて、前記半導体集積回路の回路シミュレーションを行う。

(もっと読む)

リレー回路結線ネットワークデータ生成装置、リレー回路結線ネットワークデータ生成方法、ならびにそのプログラム

【課題】リレー回路結線ネットワークデータの作成誤りを軽減でき、複雑な結線図についても短時間で自動生成することができるリレー回路結線ネットワークデータ生成装置を提供する。

【解決手段】連動図表データを入力し、鉄道信号の全体のリレー回路を構成する可能性のある複数の異なるリレー種別のリレー回路のうち、何れのリレー回路が必要となるかを連動図表データに基づいて決定する。また、決定したリレー回路についてのリレー回路結線ネットワークデータ生成プログラムと前記連動図表データとを用いて、決定したリレー回路を構成する各リレー回路ブロック内のリレー構成要素を決定するとともに、当該決定したリレー構成要素を用いて前記リレー回路内の結線図を示したリレー回路結線ネットワークデータを生成する。

(もっと読む)

回路連携解析シミュレーション装置および回路連携解析方法

【課題】変位電流を考慮する必要のない低周波の領域において、導体間に任意のインピーダンスや電流源もしくは電圧源を配置した回路モデルについての回路連携解析を行えるようにする。

【解決手段】回路モデルのすべての配線を1つのモデルとしてモデル化し、低周波電磁界解析にビーム電流要素を導入して、ベクトルポテンシャルとスカラーポテンシャルを用いて有限要素法で定式化し、回路解析と連立させる。これにより、配線・受動素子を含めた一体低周波電磁界解析を可能とすることができる。したがって、変位電流を考慮する必要のない低周波の領域において、導体間に任意のインピーダンスや電流源もしくは電圧源を配置した回路モデルについての回路連携解析を行うことが可能となる。

(もっと読む)

論理合成装置、論理合成方法及び論理合成プログラム

【課題】論理合成の際にFFに関する誤接続を確実に防止できる論理合成装置等を提供する。

【解決手段】論理合成装置10は、ICの設計仕様に関するデータ111が格納された設計仕様格納部11と、ICを構成する回路素子に関するデータ121が格納されたライブラリ部12と、設計仕様格納部11に格納された設計仕様に関するデータ111とライブラリ部12に格納された回路素子に関するデータ121とに基づき、ネットリスト131を設計する論理合成部13と、を備えている。そして、ライブラリ部12には、同一のQ出力端子23が論理接続用のQ出力端子231とクロックライン用のQ_C出力端子232とに分岐した構造を有するFF20に関するデータが格納されている。論理合成部13は、ネットリスト131を設計する際に、ライブラリ部12に格納されたFF20に関するデータを用いる。

(もっと読む)

回路改善装置、回路改善装置の回路改善方法および回路改善プログラム

【課題】電子機器の信頼性を向上するための情報を自動的に生成することにより、設計者の負担を軽減できるようにすることを目的とする。

【解決手段】故障率比較分析部210は、予測故障率データ119と目標故障率データ291とを参照して、予測故障率が目標故障率より高い構成部品の種類を「改善種類」として判定する。並列接続部品特定部221は、部品リスト293を参照して改善種類の構成部品を「改善部品候補」として判定する。並列接続部品特定部221は、基板回路図データ292を参照して改善部品候補毎に接続先の構成部品を「接続先部品」として判定する。並列接続部品特定部221は、改善部品候補毎に判定した接続先部品に基づいて、並列に接続する改善部品候補の組み合わせを「改善組み合わせ」として判定する。並列接続部品特定部221は、改善組み合わせを示す改善ポイントデータ209を出力する。

(もっと読む)

パラメトリックシミュレーションシステム

【課題】各種パラメータの組合せの変動領域と目標値を設定してシミュレーションを実行することにより、最適なパラメータ値の組合せを少ないシミュレーション回数で実現するパラメトリックシミュレーションシステムを提供する。

【解決手段】基本シミュレーションプログラムファイル設定部11a、パラメータ設定入力部11b、及び目標値設定入力部11cから成る設定入力部11と、シミュレーションを実行するパラメータ値の組合せとそのシミュレーションプログラムを作成するパラメータ値組合せ作成部12と、連続シミュレーションを実行して、シミュレーション結果をDB16に保存する連続シミュレーション実行部13と、目標値情報とシミュレーション結果とをDB16から取得し、目標値を満たしているかどうかを評価する目標値評価部14と、評価結果を一覧表にして表示する評価結果表示部15とで構成する。

(もっと読む)

集積回路装置、検証装置及び検証方法

【課題】集積回路装置が仕様通りとなっているかの検証の容易化を図る。

【解決手段】集積回路装置10は、マスターモジュール11と、マスターモジュール11に接続されたインターコネクト12と、インターコネクト12によってマスターモジュール11の接続先とされるスレーブモジュール13を含む。集積回路装置10は更に、そのスレーブモジュール13に対してインターコネクト12から送信されてくる読み出し命令信号を受信する固定値応答回路14を含む。インターコネクト12から読み出し命令信号を受信した固定値応答回路14は、インターコネクト12によってマスターモジュール11の接続先とされたスレーブモジュール13固有の固定値を、インターコネクト12に送信する。この固定値に基づき、接続先が仕様通りか否かを検証する。

(もっと読む)

半導体装置における電流による配線破壊箇所の予測方法

【課題】半導体装置の電流による配線破壊箇所の予測方法において、解析時間を短縮する。

【解決手段】下層配線14A,14Bをそれぞれ一つの直列抵抗で、第1の下層ビア15A,第2の下層ビア15Bを1個の抵抗で、第1の上層ビア17A、第2の上層ビア18Bを1個の抵抗で、第1及び第2の上層配線16A,16Bを抵抗ブリッジ回路で、パワートランジスタTRを直列抵抗で、それぞれモデリングしてなる解析モデルをモデリング用計算機により生成する。回路シミュレータ3により、解析モデルにおけるパワートランジスタTRに電流を供給し、解析モデルにおける各抵抗に流れる電流に基づいて、第1及び第2の下層配線14A,14B、第1及び第2の上層配線16A,16Bにおける各抵抗の電流密度を計算し、各抵抗の電流密度と、配線破壊を起こす電流密度閾値とを比較器4により比較することにより、配線破壊箇所を予測する。

(もっと読む)

論理回路の設計方法、論理設計プログラム及び半導体集積回路

【課題】クロック同期型の順序回路と組み合わせ回路との直列パスを含む論理回路に配置された冗長なインバータを削減してゲート段数を低減する。

【解決手段】ハードウェア記述とセルライブラリの部品とを用いた論理合成を行ってクロック同期型の順序回路と組み合わせ回路との直列パスを含む論理回路のネットリストを生成するコンピュータ装置は、正論理入力端子と正論理非反転出力端子を有する第1順序回路、及び正論理入力端子と正論理反転出力端子を有する第2順序回路に加えて、負論理入力端子と負論理非反転出力端子を有する第3順序回路、及び負論理入力端子と負論理反転出力端子を有する第4順序回路用いて、データパスにおける順序回路間のクリティカルパスのゲート段数減らす最適化処理を行う。

(もっと読む)

キャラクタライズ装置およびそのコンピュータ・プログラム

【課題】高速に信頼性の高いハードマクロの特性値を抽出することが可能なキャラクタライズ装置を提供すること。

【解決手段】特性値抽出部32は、ハードマクロに入力する信号波形にスルーを与えて静的な経路探索を行なうことにより、ハードマクロ内の測定点における遅延時間を算出して特性値を抽出する。動的検証部34は、特性値抽出部32によって抽出された特性値を用いてハードマクロの動的検証を行なうことにより、特性値が適切か否かを検証する。したがって、動的検証に要する時間を短くすることができ、高速に信頼性の高いハードマクロの特性値を抽出することが可能となる。

(もっと読む)

半導体集積回路の遅延解析方法、遅延解析プログラム、遅延解析装置

【課題】動的再構成デバイスの精度の高い遅延解析方法を提供する。

【解決手段】遅延解析方法は、動的再構成デバイスの回路面の変更を制御するための再構成パスにおける遅延値を記憶装置から抽出するステップと、再構成パスの遅延値を考慮して回路面におけるデータパスの遅延値を算出するステップとを具備する。

(もっと読む)

FPGA設計支援システムおよびFPGA設計支援方法ならびにFPGA設計支援プログラム

【課題】FPGAの設計段階で、ユーザ回路にTMRを適用したときのSERを見積もることができるFPGA設計支援システムを提供する。

【解決手段】TMRを適用した場合のSER低減率を含む情報を保持するTMR効果情報DB17と、FPGAが有するCRAM全体のSERを計算するCRAM_SER計算部12と、各回路ブロックのFPGAリソースの使用率を計算するFPGAリソース使用率計算部13と、CRAM全体のSERおよび各回路ブロックのFPGAリソースの使用率に基づいて、回路ブロック単位のSERを計算する回路ブロックSER計算部11と、TMRブロックについてSERおよびTMRを適用した場合のSERの低減率に基づいてTMRブロックのSERを計算するTMRブロックSER計算部14と、各回路ブロックのSERおよび各TMRブロックのSERに基づいてユーザ回路全体のSERを計算するSER計算部10とを有する。

(もっと読む)

回路シミュレーション方法および回路シミュレーション装置

【課題】寄生素子を考慮した半導体集積回路の回路シミュレーションにおいて、精度を落とさずにシミュレーション時間を短縮する。

【解決手段】半導体集積回路のレイアウトデータ110から寄生素子を含むネットリスト130を作成する寄生素子抽出部120と、寄生の影響を考慮する必要の無い回路ブロック情報を格納したデータベース部150と、データベース部150内に登録された回路ブロックが、対象としている半導体集積回路に存在するか否か判定する回路判定部160と、同じ回路ブロックが存在すると判定された時に、レイアウトデータ110から抽出したネットリスト130の中で、同じ回路ブロックと判断された部分のネットリストをネットリスト置換部180によって、寄生素子を含まない回路ブロックのネットリスト130Zに置換することで不要な寄生素子を削除しネットリストを簡素化して、回路シミュレータ190で回路シミュレーションを実施する。

(もっと読む)

プログラム、ライブラリ作成装置、及び方法

【課題】半導体装置の消費電力の見積もりを精度よく行えるようにするための技術を提供する。

【解決手段】コンピュータは、半導体装置の消費電力値を計算する評価条件となりうる範囲を表す範囲情報を取得し、半導体装置を構成する基本素子であるセル毎に、取得した範囲情報が表す範囲内の評価条件でセルの消費電力値の計算を行うための計算式として、評価条件の内容を表す所定の状態量を含む項に定数を項として追加した因子が存在する計算式を設定し、設定した計算式を表す計算式情報を前セル毎に格納したライブラリを作成する。

(もっと読む)

演算増幅器のマクロモデル及びこれを用いた回路設計シミュレータ

【課題】シミュレーション演算時の負荷増大を抑えつつより実機に近い応答を模擬する。

【解決手段】本発明に係るプログラムは、演算部と、記憶部と、操作部と、表示部と、を備えたコンピュータに実行され、前記コンピュータを回路設計シミュレータとして機能させる回路設計シミュレーションプログラムの一部品であり、前記回路設計シミュレータで用いられる演算増幅器のマクロモデルとして、前記回路設計シミュレータ上で演算増幅器の応答を模擬するように前記コンピュータを動作させるものであって、前記演算増幅器のマクロモデルは、前記演算増幅器の入力異常時や電源異常時に出力異常を発生させるための制御部(LMT1)を有する構成とされている。

(もっと読む)

半導体集積回路シミュレーション装置及び半導体集積回路のシミュレーション方法

【課題】バスアーキテクチャの変更があった場合にTLモデルの変更あるいは書き換えを不要にする半導体集積回路シミュレーション装置を提供する。

【解決手段】実施形態によれば、シミュレーション装置1は、半導体集積回路に含まれるバスのバスアーキテクチャ情報を取得するバスアーキテクチャ情報取得部と、取得したバスアーキテクチャ情報に基づいて、バスアーキテクチャに適合する転送サイズを算出する転送サイズ算出部と、シミュレーション実行部とを有する。シミュレーション実行部は、半導体集積回路に含まれるバスイニシエータからのトランザクションを、転送サイズに適合するサイズのトランザクションに変換してバスへ出力するトランザクション変換部を設定して、半導体集積回路のシミュレーションを行う。

(もっと読む)

モンテカルロ解析実行制御方法、およびモンテカルロ解析実行制御装置

【課題】モンテカルロ解析の結果に対して要求される精度を保証しつつ、モンテカルロ解析に要する時間を可及的に短縮する。

【解決手段】目標歩留まり、評価項目の仕様および信頼水準を設定し、モンテカルロ解析の実行を指示する。モンテカルロ解析のシミュレーションの実行により得られた評価項目の値、及び評価項目の仕様および信頼水準を用いて、前記評価項目の値が前記信頼水準でとり得る範囲である歩留まりの信頼区間を算出する。前記目標歩留まりが前記歩留まりの信頼区間内にあるか否かを判定する第1の判定処理を行う。前記目標歩留まりが前記歩留まりの信頼区間内にある場合、モンテカルロ解析の実行を指示する。一方、前記目標歩留まりが前記歩留まりの信頼区間内にない場合、前記歩留まりの信頼区間の下限が前記目標歩留まり以上のとき前記目標歩留まりを達成すると判定し、前記歩留まりの信頼区間の上限が前記目標歩留まり未満のとき前記目標歩留まりを達成しないと判定する第2の判定処理を行う。

(もっと読む)

消費電力検証支援装置

【課題】必要な波形データの取得ができ、かつ、シミュレーション時間を短縮することができる消費電力検証支援装置を提供することである。

【解決手段】実施の形態の消費電力検証支援装置は、消費電力概算部と、比較判定部と、遅延制御部と、ダンプ処理部とを有する。消費電力概算部は、指定信号を観測する第1のシミュレーションの所定時間毎に消費電力を概算する。比較判定部は、消費電力概算部で概算された消費電力の概算値を閾値と比較し、比較結果から所定時間毎にダンプ処理を行うか否かを判定する。遅延制御部は、全信号を観測する第2のシミュレーションを第1のシミュレーションに対して所定時間遅延させて実行させる。ダンプ処理部は、比較判定部の判定結果に基づき、ダンプ処理を行うと判定された所定時間の間の全信号の波形データを記録する。

(もっと読む)

FPGA、FPGAを用いた回路再構成システム、方法およびプログラム

【課題】回路の一部に不具合が生じて新たな回路を同一基板内に再構成する場合に、この新たな回路との関係で伝送される信号のタイミングに不具合が生じないようにすることが可能なFPGA、FPGAを用いた回路再構成システム、方法およびプログラムを得ること。

【解決手段】回路ブロック監視手段12が回路ブロックを構成する論理部に不具合があることを検出すると、これに代わる新しい回路ブロックを構成するとき最適化処理実行手段13は論理部同士を接続する接続部による信号の伝達タイミングを前の回路ブロックの接続部と可能な限り同一になるように最適化する。回路ブロック交代手段14は新しい回路ブロックの運用を開始させる。

(もっと読む)

41 - 60 / 1,280

[ Back to top ]