Fターム[5B046BA03]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 回路設計 (1,280)

Fターム[5B046BA03]に分類される特許

141 - 160 / 1,280

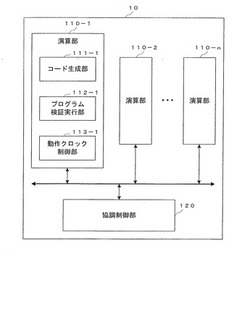

シミュレーション装置、シミュレーション装置の制御方法およびプログラム

【課題】複数の処理を協調動作させてそれぞれの処置の因果関係を検証するシミュレーション処理において、無用な待機時間を抑制し、シミュレーション効率を向上させる。

【解決手段】シミュレーション装置10に、コンピュータプログラムに含まれた複数の指令に従ってって異なる対象の動作をそれぞれシミュレートする複数の演算部110−1〜110−nと、これら演算部の動作タイミングを制御して前記演算部において実行される前記指令を協調させる協調制御部120とを備え、前記演算部の少なくとも1つは、当該演算部が実行する指令に応じてその指令を実行する際の動作クロックを制御するクロック制御部113−1〜113−nを備えることを特徴とする。

(もっと読む)

遅延ライブラリ作成方法及びプログラム

【課題】統計的STA用のセル遅延ライブラリの作成に要する時間を削減すること。

【解決手段】遅延ライブラリ作成方法は、(A)ノミナル遅延値を算出するステップと、(B)セル遅延値に対するばらつき変数の寄与度を表す感度係数を算出するステップと、(C)ノミナル遅延値及び感度係数を提供するセル遅延ライブラリを作成するステップと、を含む。ばらつき変数は、少なくとも1つのグループにグループ分けされている。感度係数を算出するステップは、グループ毎に実施され、1つのグループに対して1つの共通の感度係数が算出される。

(もっと読む)

半導体集積回路の設計装置、設計方法及びプログラム

【課題】クロックゲーティングされた前段FFと後段FFとの間に、クロックゲーティングされたホールドエラー補償用の挿入FFを接続する場合、挿入FFの挿入前後での半導体集積回路の動作結果が異なり、動作不正が発生する可能性がある。

【解決手段】本発明は、クロックゲーティングされた前段FFと後段FFとの間に新たに、クロックゲーティングされた挿入FFを接続する半導体集積回路の設計方法であって、前段FF、後段FFに対応したクロックゲーティングセルのタイプに応じて、挿入FFに入力するクロックゲーティングセルを決定する半導体集積回路の設計方法である。

(もっと読む)

回路検証装置および方法、ならびに、回路検証用書込データ生成装置およびプログラム

【課題】検証対象の回路が実装された半導体デバイスから観測対象の記憶素子の値をより効率よく読み出すことができる回路検証装置を提供すること。

【解決手段】第一番号および第二番号の組合せによって識別される複数の記憶素子を有する半導体デバイス504に実装する回路を表す回路データ100と、観測対象の記憶素子が記載された観測記憶素子リスト102と、半導体デバイス504内の各記憶素子の第一番号および第二番号を含む番号データベース101とを格納したデータ格納部110と、観測記憶素子リスト102および番号データベース101に基づいて、観測対象の各記憶素子の配置配線後の第一番号が連続するよう制約情報104を生成する制約情報生成部103と、制約情報104および回路データ100に基づいて配置配線を行い、半導体デバイス504に書き込む書込データ106を生成する配置配線部105と、を備える。

(もっと読む)

ノイズ解析装置及びノイズ解析方法

【課題】半導体集積回路の設計初期において、電源制御回路により内部回路の電源の接続及び切断を行った際に発生する電源ノイズの解析を短時間で精度良く行えるようにする。

【解決手段】電源ノイズ解析に係る基本単位回路の解析モデルを作成し、それを半導体集積回路の内部回路の解析モデルとして組み込み、半導体集積回路のレイアウトの前段階で、内部回路への電源供給を制御する複数のスイッチ群を有する電源制御回路を用いた半導体集積回路にて内部回路の電源の接続及び切断を行った際に発生する電源ノイズを算出する。

(もっと読む)

回路シミュレーション装置、回路シミュレーション方法及びプログラム

【課題】位相同期回路を含む回路シミュレーションにおいて、フィードバックループに分周器が存在している場合であっても正確にシミュレートできるようにすること。

【解決手段】フィードバックループに設けられた分周器の分周比を測定するための第1のクロック信号を生成する測定クロック生成部と、分周器が第1のクロック信号を受信して分周して出力した第2のクロック信号と、第1のクロック信号とを参照して、分周器の分周比を測定する分周比測定部と、入力クロック信号を受信し、入力クロック信号の周期と予め設定された逓倍比と測定された分周比の逆数に相当する逓倍比とに応じて、入力クロック信号を逓倍して第3のクロック信号として出力する逓倍クロック生成部と、第1のクロック信号及び第3のクロック信号を受信し、いずれかを出力クロック信号として出力するクロック出力制御部とを有する。

(もっと読む)

半導体装置設計支援方法、半導体装置設計支援プログラム、及び半導体装置設計支援装置

【課題】バイアス条件によらず、モデルに対する解析精度を向上させる。

【解決手段】本発明による半導体回路の設計支援方法は、第1モデル22を用いて、プロセスパラメータが変動したときのデバイス特性の変動量102を算出するステップと、第2モデル23を用いて算出されたデバイス特性と実測値21との誤差に対して、変動量102で規格化するステップと、演算装置11が、規格化された誤差を用いて第2モデル23に対する解析を行うステップとを具備する。

(もっと読む)

回路検証装置及び回路検証方法

【課題】メタステーブル状態をより確実に想定して、非同期順序回路を含む論理回路の機能を検証することができる回路検証装置及び回路検証方法を提供する。

【解決手段】論理回路の機能を検証するコンピュータ2に、非同期順序回路201のクロック周期Tdistと、非同期順序回路201の第1段目のフリップフロップ回路FF01のメタステーブル収束時間Tmcと、に基づいて、(1)式により、メタステーブル状態値の生成段数cを算出する生成段数算出部と、回路設計プログラムを解析することにより、フリップフロップ回路FF01から第n段目のフリップフロップ回路までを特定する順序回路特定部と、機能シミュレーションにおいて、第1段目から第n段目のフリップフロップ回路に、それぞれ生成段数cから(生成段数c−(n−1))に等しいクロックサイクル数分、メタステーブル状態値を出力させる機能シミュレーション制御部と、を備えた。

(もっと読む)

チェックリスト自動生成装置、チェックリスト自動生成方法およびチェックリスト自動生成プログラム

【課題】図面チェック用のチェックリストを自動生成可能なチェックリスト自動生成装置を得ること。

【解決手段】図面上に描画された形状等をそれぞれ1つのオブジェクトとし、オブジェクトごとの描画データを記憶し、各オブジェクトに対してIDおよびオブジェクト種類を付与するCAD図面作成部2と、オブジェクト種類と関連付けて、判定条件およびチェック項目文書を記載したルールを記録するためのチェック項目DB4と、オブジェクトごとにCAD図面作成部2から情報を取得し、チェック項目DB4からオブジェクト種類に該当するルールをすべて抽出し、オブジェクトごとの描画データおよび判定条件に基づいて、オブジェクトごとに当該判定条件に適合するかどうかを判定し、適合すると判定されたルールに記載されたチェック項目文書を用いてチェックリストを生成するチェックリスト生成部3と、を備える。

(もっと読む)

半導体集積回路設計装置、半導体集積回路設計方法及びプログラム

【課題】設計者の負担を軽減しつつ、定格を満たす半導体集積回路を設計できるようにすること。

【解決手段】半導体集積回路設計方法は、コンピュータが、各回路シミュレータのバイアスチェック定義の書式を格納したフォーマットファイルと、各デバイスの定格値情報を格納したデバイス定格値情報ファイルと、各デバイスのモデルの端子情報を格納したモデルファイルを参照し、使用する回路シミュレータに応じたバイアスチェック定義を生成する生成工程と、バイアスチェック定義を含むネットリストを回路シミュレータに入力して、定格違反となるデバイスの有無を検証する検証工程と、定格違反となるデバイスが存在する場合には、該デバイスに対する代替候補を、デバイス定格値情報ファイルに含まれるデバイスの中から抽出する抽出工程と、を含む。

(もっと読む)

端子割り当て装置及び端子割り当て方法

【課題】容易に各端子に割り付けられる機能が決定できる端子割り当て装置を提供する。

【解決手段】設計対象装置に含まれる端子と、割り当てることが可能な候補機能群との対応関係を示す情報を、端子情報として格納する、端子情報格納部と、前記端子情報に基づいて、前記各端子に割り当てられる機能を決定し、割り当て結果データを生成する処理部とを具備する。前記端子情報において、前記候補機能群に含まれる各候補機能には、前記各候補機能が所属する関連機能グループを示す関連情報が対応付けられている。前記処理部は、前記関連情報を参照して、前記選択機能が所属する関連機能グループを特定関連機能グループとして特定する。前記複数の端子の中から、前記特定関連機能グループに所属する候補機能を有する他の端子が、関連端子として選択される。前記関連端子に、特定関連機能グループに所属する候補機能が割り付けられ、割り当て結果データが生成される。

(もっと読む)

SPICEモデルパラメータ出力装置及び出力方法

【課題】高周波MOSFETやアナログMOSFETの基板抵抗を正確にモデル化することが可能なSPICEモデルパラメータ出力装置及び出力方法を提供。

【解決手段】MOSFETの形状データと、MOSFETの周波数特性に関する測定データとを入力するためのデータ入力部101と、測定データに基づいて、MOSFETに関する1端子基板抵抗モデルの基板抵抗を算出する基板抵抗算出部102〜105と、1端子基板抵抗モデルの基板抵抗と、形状データとに基づいて、SPICEモデルパラメータを算出して出力するSPICEモデルパラメータ出力部106とを備える。

(もっと読む)

回路シミュレータおよび半導体装置の設計方法

【課題】インパクトイオン化電流の算出精度を向上させる。

【解決手段】飽和ソース−ドレイン電圧Vdsatがソース−ゲート電圧Vgsおよびソース−ドレイン電圧Vdsの関数にて与えられたドレイン横方向電界Edの計算式に基づいて電界効果トランジスタのインパクトイオン化電流Iiiを計算する。

(もっと読む)

フロアプランデータ生成装置及び方法

【課題】チップの設計期間を短縮する。

【解決手段】CPU1は、設計対象の回路を構成するセルのうち、所定のサイズより大きいセルサイズを有するセルのみの回路情報をゲートレベルで記述した簡易ネットリスト43と、所定のサイズより大きいセルサイズを有するセルのみの仕様データを含むセルリスト44とを用いてフロアプランを行い、仮フロアプランデータ47を生成する。CPU1は、ユーザによって回路全体のフロアプランが行われるときに、回路を構成するセルの仕様データである全体ライブラリ42と、回路を構成するセルの回路情報をゲートレベルで記述した全体ネットリスト45と、仮フロアプランデータ47と、簡易ネットリスト43を全体ネットリスト45に整合させるためのセルリスト44とを出力する。

(もっと読む)

ノイズ解析方法、ノイズ解析プログラム

【課題】バッファ動作により発生するノイズを高精度に解析すること。

【解決手段】バッファは、電源端子、グランド端子及び出力端子を備える。バッファの過渡解析を行い、電源端子電流、グランド端子電流及び出力端子電流のそれぞれの波形を算出する。更に、それら波形に基づいて、電源端子から出力端子へ流れるチャージ電流、出力端子からグランド端子へ流れるディスチャージ電流、及び電源端子からグランド端子へ流れるリーク電流のそれぞれの波形を算出する。フーリエ変換を行い、3種類の電流波形のそれぞれの周波数成分を算出した後、AC解析により得られるインピーダンス周波数特性と掛け合わせることによって、ノイズの周波数成分を算出する。更に、ノイズの周波数成分の逆フーリエ変換を行うことにより、ノイズの波形を算出する。

(もっと読む)

半導体集積回路のタイミング解析装置、そのタイミング解析装置のためのプログラム及びそのプログラムを記録したコンピュータ読み取り可能な記録媒体

【課題】回路変更後にタイミングが悪化した箇所を効率的に特定できるようにする。

【解決手段】比較の基準となる基準回路のネットリスト及びタイミング情報を基準回路のライブラリ4,6から読み込む基準回路データ読込み手段12と、基準回路に対して少なくとも一部が異なっている改定版回路のネットリスト及びタイミング情報を改定版回路のライブラリ8,10から読み込む改定版回路データ読込み手段14と、両回路に共通のタイミング制約を読み込むタイミング制約読込み手段16と、読み込んだタイミング制約に基づいてそれぞれの回路のタイミングを解析する解析手段18,20と、基準回路についての解析手段による解析結果データである基準回路タイミングレポートと改定版回路についての解析手段による解析結果データである改定版回路タイミングレポートを並べて出力する手段32,34と、を備えている。

(もっと読む)

シミュレーション方法、シミュレーション装置、プログラム、及び記憶媒体

【課題】 本発明の課題は、設計空間の良不良の境界を特定すると共に、境界点のうち原点に一番近い最確点または最適設計点を特定することを目的とする。

【解決手段】 上記課題は、装置又は回路の動作をシミュレーションするシミュレーション方法であって、コンピュータが、任意の設計パラメータを原点とした設計空間における製品の良不良の境界を、動作の良不良を判別する判定指標とは別の動作状態に基づいて定義した探索用指標に基づいて探索することによって特定する境界特定手順を実行することを特徴とする、シミュレーション方法により達成される。

(もっと読む)

回路図表示装置及び回路図表示方法

【課題】効率良く正確に回路の論理を確認することが可能な回路図表示装置及び回路図表示方法を提供する。

【解決手段】回路の情報を記憶する記憶手段と、回路を表示する表示手段と、回路に入力する固定値の指定の入力を受ける入力手段と、入力手段により指定された固定値を回路に入力した場合に、当該回路のうち、当該固定値の伝播によりブロックされる部分を抽出する固定値伝播手段と、を有し、表示手段は、回路のうち、固定値伝播手段により抽出されたブロックされる部分を非表示する。

(もっと読む)

電子回路解析装置及び電子回路解析方法

【課題】電磁波解析シミュレータと回路解析シミュレータとを連携させる際に、電子回路の解析を任意の時刻で中断/再開させることが可能な電子回路解析装置及び電子回路解析方法を提供することを目的としている。

【解決手段】電子回路の電磁波解析を行う電磁波解析シミュレータと、前記電子回路についての回路解析を行う回路解析シミュレータとを連携させて電子回路の解析を行う電子回路解析装置であって、前記電磁波解析シミュレータによる解析結果を記憶領域に蓄積する蓄積手段と、前記電子回路の解析の再開において、前記記憶領域に蓄積された前記解析結果を用いた前記回路解析シミュレータによる回路解析を実行させた後に前記電磁波解析シミュレータと前記回路解析シミュレータとの連携を再開させる再開制御手段と、を有する。

(もっと読む)

回路シミュレーション装置

【課題】電源変動状況にある回路の回路シミュレーションの高速化を可能にする回路シミュレーション装置を提供する。

【解決手段】回路シミュレーション装置は、オン状態またはオフ状態となる特定素子を含む所定回路の回路構成と、所定回路の動作を制御する制御信号と、抵抗を介して前記所定回路に供給される電源電圧と、を表す回路情報を受け付ける受付部と、回路情報に基づき、制御信号および電源電圧に従った所定回路の動作を解析する回路シミュレーションを実行する実行部と、を含み、実行部は、特定素子のオン状態またはオフ状態が維持されている間の所定回路の回路シミュレーションとして、所定回路を簡略化した等価回路の回路シミュレーションを実行する。

(もっと読む)

141 - 160 / 1,280

[ Back to top ]