Fターム[5B046BA03]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 回路設計 (1,280)

Fターム[5B046BA03]に分類される特許

121 - 140 / 1,280

半導体設計装置

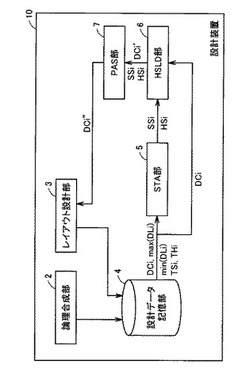

【課題】セットアップ違反やホールド違反を発生させずに、電力を消費するタイミングを分散させることができる半導体設計装置を提供する。

【解決手段】STA部5は、フリップフロップのクロックレイテンシの現在の設計値に基づいて、フリップフロップのセットアップ時間のマージンであるセットアップスラックを算出する。HSLD部6は、算出したセットアップスラックに基づいて、タイミング違反を起こさない範囲で、フリップフロップのクロックレイテンシを現在の設計値よりも早める方向に調整する。PAS部7は、HSLD部6によるレイテンシ制御の結果、クロックレイテンシ分布においてシンク数に閾値以上のピークが残る場合、HSLD部6による再計算後のタイミング情報により、タイミング違反を起こさない範囲で、フリップフロップのクロックレイテンシをスムージングする。

(もっと読む)

信号名設定方法およびシステム

【課題】重複しない信号名を付加し、ロジック処理設計における信号名付加作業を確実、容易にする信号名設定方法およびシステムを提供する。

【解決手段】一連のシーケンスロジックを適宜のシート単位に分割し、シートごとに入力名と、出力名をユニークに決定するための信号名設定方法において、シートの入力と出力に、このシート内でユニークなローカル信号名を付与し、このシートに、このシートの機能に関連して機能名を付与し、各シートの出力に機能名の後にローカル信号名を付した出力の本番信号名を決定し、各シートの信号名と、機能名を関連つけて抽出して、入力信号関連情報と出力信号関連情報の対比により、当該シートの出力を受ける他のシートの入力を決定し、決定された入力の信号名を、送り側のシートの出力の本番信号名に置換する。

(もっと読む)

検証支援プログラム、検証支援装置および検証支援方法

【課題】検証漏れの少ない効率的な検証の実現を支援すること。

【解決手段】検証支援装置100は、クロックドメインBのクロックサイクル毎に、回路ブロック2からの出力信号変化を観測する。1回以上の出力信号変化があった場合にはその変化時刻のいずれか一つをランダムに選択し、その時の出力信号値をサンプリングし(ステップS111)、サンプリング結果からその時刻に値変化のあった信号(回路ブロック2からの出力信号)の値をランダムな論理値に置換した後、クロックドメインBの動作クロックの立ち上がりに合わせて、回路ブロック3へ入力する(ステップS112)。すなわち、ステップS112では、回路ブロック2から出力された出力信号の中でサンプリング時刻に値変化があったものをランダムな論理値に置き換えて入力することによって、回路ブロック3にDCDジッタを発生させることができる。

(もっと読む)

回路モデル生成装置

【課題】 本発明の課題は、素子データを含むアナログ回路モデルを生成することを目的とする。

【解決手段】 上記課題は、回路図データとレイアウトデータとを格納する記憶領域と、前記レイアウトデータから寄生素子に係る素子データを抽出する抽出手段と、前記回路図データに前記素子データを含む回路モデルをハードウェア記述言語によって生成する回路モデル生成手段とを有する回路モデル生成装置により達成される。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】RCで鈍る出力電圧を再現し、遅延誤差を抑制すること。

【解決手段】電流テーブル群は、セルへ与える入力電圧の変化開始時からの複数の経過時間の各経過時間でのセルの出力電圧値をセルごとに保持し、設計支援装置がアクセス可能な記憶装置に記憶されている。設計支援装置は、設計対象回路の回路情報の中から選ばれた対象セルに関する各経過時間での出力電圧値を対象セルに基づいて抽出する。設計支援装置は、Vds(出力電圧)<Vgs(入力電圧)−Vth(ゲート閾値電圧)であるVdsの経過時間を補正対象の経過時間に決定する。設計支援装置は、補正対象の経過時間に対象セルの出力側の時定数を加算することにより、該経過時間を補正する。設計支援装置は、補正後の経過時間ごとの出力電圧値と補正対象に決定されなかった経過時間ごとの出力電圧値とを出力する。

(もっと読む)

積層チップコンデンサの等価回路モデル,その回路定数解析方法・プログラム・装置,及び回路シミュレータ

【課題】回路シミュレータを用いた積層チップコンデンサを含む回路と実際の回路性能との誤差の発生を良好に抑制する。

【解決手段】基本等価回路の等価直列キャパシタンスCと、等価直列レジスタンスRの一部を、スタティックキャパシタンスC0と、積層チップコンデンサ内における内部電極の角や端の近くに発生する電磁場分布の異常特性に関する回路素子として、キャパシタンスCm及びC1,レジスタンスRc1を設ける。更に、積層チップコンデンサ内部における内部電極の表皮効果と、電磁近接効果を考慮するとともに、誘電体材料の損失や寄生キャパシタンス,外部電極の寄生インダクタンスも考慮し、レジスタンスRp1,Rp2、キャパシタンスCp、インダクタンスLm,L1,レジスタンスRL1を追加する。

(もっと読む)

設計ライブラリデータベース

【課題】結晶化半導体薄膜に対して適正かつ効率的なフォトマスクの作成を可能にする。

【解決手段】1実施形態に係る設計ライブラリデータベースは、2次元的に区画して各々薄膜トランジスタのチャネル領域のサイズを超える複数の結晶粒規定領域が配置された結晶化半導体薄膜を用いる薄膜トランジスタ回路の設計ライブラリデータベースであって、各々のチャネル領域が単一の前記結晶粒規定領域内の固定位置に配置される2個以上の薄膜トランジスタおよび前記2個以上の薄膜トランジスタを相互接続する配線を含む様々な論理ゲート回路をそれぞれ表す複数のスタンダードセル、並びに前記様々な論理ゲート回路の様々な組み合わせをそれぞれ表す複数のマクロセルの少なくとも一方のセルのライブラリ、および前記複数の結晶粒規定領域が配置された結晶化アレイパターンのスタンダードセルのライブラリを含みハードディスクに登録される。

(もっと読む)

スキャンチェーン形成方法、プログラム及び設計支援装置

【課題】タイミングエラーを解消しつつも、遅延素子の増加及び試験コストの増大を抑制することのできるスキャンチェーン形成方法を提供する。

【解決手段】複数のスキャンFFを、各スキャンFFのスキャン端子間の配線長が最短となるようにスキャンチェーンを形成する。その後、複数のスキャンFFのうちタイミングエラーの発生した対象スキャンFFを中心とした、タイミングエラーの発生しない座標集合X3を算出し、その座標集合X3内に配置されたスキャンFFの中から、リオーダー処理前のスキャンチェーンのつなぎ順をできる限り保持するように1つのスキャンFFを選択する(ステップS17〜S19,S23)。続いて、その選択したスキャンFFと対象スキャンFFとを接続するようにつなぎ順を変更する(ステップS20)。

(もっと読む)

プロセッサ、プロセッサ生成装置及びプロセッサ生成システム

【課題】 プロセッサ内の未使用回路を削除し、必要な機能と性能を備えたプロセッサを安価なコストで提供する。

【解決手段】 記憶装置から命令を読み出し、その命令をデコーダで解釈し、その解釈に基づいて処理を順次進める専用プロセッサを生成するための設計記述されたプロセッサにおいて、プロセッサは、少なくとも命令を対象としたコンフィギュレーション定義記述と、専用プロセッサ内の回路を定義する回路記述とを有し、プロセッサは、予め備えている命令のうち任意の命令を削除可能、かつ該削除によって不要となる回路を削除可能になされたプロセッサである。

(もっと読む)

シミュレーション装置およびその方法

【課題】

電子システム製品のソフトエラー率と処理性能との最適値算出を支援するシミュレーション装置およびその方法を提供することを目的とする。

【解決手段】

定義された構成モデルの構成要素の部品情報である属性情報と該定義された構成モデルの構成要素間の接続関係を示す接続情報とに基づき、該定義された構成モデルの構成要素の離散型シミュレーションを行う離散事象シミュレーション部と、前記離散事象シミュレーション部のシミュレーション結果と前記属性情報の中のソフトエラー率データとに基づいて、該定義された構成モデルのソフトエラー率を算出するソフトエラー率計算処理部と、を備えたシミュレーション装置である。

(もっと読む)

回路シミュレーション方法および回路シミュレーション装置

【課題】精度の高い回路シミュレーションを実行する回路シミュレーション方法を提供する。

【解決手段】ゲートレベルでの電圧変動解析ステップを実行する(ステップS2)。ゲートレベルでの電圧変動解析ステップは、チップTP全体に対して実行する。そして、次に、電圧変動解析ステップに従う電源電圧および接地電圧(Vss)の電圧波形を取得するステップを実行する(ステップS4)。次に、トランジスタレベルでの信号解析ステップを実行する(ステップS6)。トランジスタレベルでの信号解析解析ステップは、チップTP全体よりも範囲の狭い例えば、すべてではない、1つ又はそれ以上の機能モジュールに対して実行する。そして、信号解析ステップに従う信号解析結果を取得するステップを実行する(ステップS8)。

(もっと読む)

ディレイライブラリ生成装置,ディレイライブラリ生成プログラムおよびディレイライブラリ生成方法

【課題】FF等の順序回路のディレイライブラリの生成を人手によることなく短時間で行なえるようにする。

【解決手段】順序回路の回路情報に基づき順序回路の出力端子と当該出力端子に影響を与える順序回路の入力端子とをグループ化するグループ化部11と、このグループ化部11によって得られたグループと順序回路の真理値表とに基づき、順序回路の入力端子に対する、ディレイ情報測定用の信号パターンを前記グループ毎に生成する信号パターン生成部12と、この信号パターン生成部12によって前記グループ毎に生成された信号パターンに基づき、順序回路のディレイを示すディレイ情報を前記グループ毎に測定し、順序回路のディレイライブラリを生成するライブラリ生成部13とをそなえる。

(もっと読む)

集積回路、集積回路設計装置及び集積回路設計方法

【課題】電圧が供給される電源の数が増大するのを抑えることが可能な集積回路を提供する。

【解決手段】開示の集積回路は、第1及び第2の電源配線と、フリップフロップ回路と、スイッチ素子とを備える。第1及び第2の電源配線は共通の電源に接続されている。フリップフロップ回路は、集積回路に対する電源からの電圧供給が停止された場合であっても、データを保持することが要求される。当該フリップフロップ回路は、第1の電源配線に接続されている。スイッチ素子は、例えばトランジスタスイッチであり、電源から電圧を供給するか否かを切り替えるためのものである。スイッチ素子は第2の電源配線に設けられている。

(もっと読む)

ゲート駆動回路の設計支援装置および設計支援方法

【課題】ゲート駆動回路の設計を、短TAT化する設計支援装置を提供する。

【解決手段】半導体素子のスイッチングを制御するゲート駆動回路に含まれる回路素子のパラメーを用いて前記半導体素子のスイッチング電圧を計算する回路解析部と、前記スイッチング電圧によって前記ゲート駆動回路を搭載するシステムに発生する電磁放射ノイズを計算する電磁界解析部と、前記電磁放射ノイズが目標値に収まっているか否か判定する第1の判定部と、前記電磁放射ノイズが目標値に収まっていない場合に、前記電磁放射ノイズを抑制するように前記回路素子のパラメータを改良する第1の回路改良部と、前記改良したパラメータを用いて前記回路解析部が計算したスイッチング電圧に基づいて電磁放射ノイズを推定するノイズ推定部と、を備え、中央処理装置が、前記回路素子のパラメータを最適化する。

(もっと読む)

モデル式生成方法、装置及びプログラム

【課題】SRAM設計のためのモデル式を生成するために実行するシミュレーション回数を削減する。

【解決手段】所定の指標についての平面における歩留検討対象の四辺形の頂点におけるスタティックノイズマージンSNM及びライトマージンWMのモデル式を生成する場合に、指定頂点の各々におけるSNM及びWM間の推定される関係に応じて予め設定されている重み値に応じて、初期シミュレーション回数を、指定頂点の各々におけるSNM及びWMの各々に配分し、所定パラメータ値を変動させつつ配分回数分シミュレーションを実施させる。また、初期のシミュレーション結果からモデル式を生成し、当該モデル式の近似精度評価指標値を算出し、当該モデル式が、予め定められている歩留モデル式に対する影響の有無を判定する。そして、各モデル式について、近似精度評価指標値及び歩留モデル式に対する影響の有無に応じて追加シミュレーションの要否を判定する。

(もっと読む)

MOSFETモデル出力装置及び出力方法

【課題】寄生素子の効果が適切に取り入れられた高精度のMOSFETモデルを作成可能なMOSFETモデル出力装置及び出力方法を提供する。

【解決手段】MOSFETの形状データを入力するための形状データ入力部101を備える。前記形状データを利用して、前記MOSFETモデルに付加するための寄生素子モデルのパラメータを算出するパラメータ算出部102を備える。前記寄生素子モデルのパラメータを利用して、前記寄生素子モデルが付加された前記MOSFETモデルを作成して出力するMOSFETモデル出力部103を備える。そして、前記MOSFETモデル出力部は、前記MOSFETがN型MOSFETである場合とP型MOSFETである場合とで、前記MOSFETモデルに対し、異なる前記寄生素子モデルを付加する。

(もっと読む)

シミュレーションパラメータ校正方法、装置及びプログラム

【課題】回路等のばらつき考慮シミュレータに対して入力すべきデバイス特性の統計パラメータ値等を適切に校正する。

【解決手段】本方法は、所定の製品特性の統計量の基準候補値に対する所定の製品性能のシミュレーション結果値を、ばらつき考慮シミュレーションによって取得する工程と、所定の製品特性の統計量についての確率密度関数と所定の製品性能についての確率密度関数とから定義される尤度関数であって所定の製品特性の統計量と所定の製品性能のシミュレーションとを合わせた尤度を算出するための尤度関数に対して、上記基準候補値と上記シミュレーション結果値と所定の製品特性の測定値の統計量と所定の製品性能の測定値とを代入して、上記尤度を算出する工程と、基準候補値を変動させつつ上記工程を複数回実行して、尤度が最大となる場合における基準候補値を特定する工程とを含む。

(もっと読む)

クロックジッター解析方法、該クロックジッター解析方法を実行する装置、該クロックジッター解析方法をコンピュータに実行させるためのプログラム、及び該プログラムを記録したコンピュータ読み取り可能な記録媒体

【課題】クロックジッターの最悪値を短時間で算出する。

【解決手段】動作シナリオ情報のうち選択されたクロックドメイン以外のクロックドメインに属する素子を停止状態とすることにより、ドメイン動作シナリオを作成する。次に、ドメイン動作シナリオを用いて、選択されたクロックドメインで用いられるクロックの1〜数周期の期間について電源ノイズ解析を行い、ドメイン電源ノイズ波形を取得する。次に、ドメイン電源ノイズ波形を繰り返し接続することで周期的な波形を作成し、この周期的な波形の一部を停止することでクロックパスを流れるクロックの周期以上のノイズ停止期間を有する加工ドメイン電源ノイズ波形を取得する。次に、複数のクロックドメインの各々の加工ドメイン電源ノイズ波形を重ね合わせ、それによって得られた電源ノイズ波形を元に、クロックパスを流れるクロックのジッターを算出する。

(もっと読む)

動作合成装置および動作合成プログラム

【課題】マニュアルでアーキテクチャの探索をすることなく、マルチ処理化されたアウトプット(回路)を得る動作合成装置等を提供することを提供すること。

【解決手段】動作合成装置は、動作合成ツールへマルチ処理に関する制約を与える動作合成制約記述、シングル処理の動作記述をもとに解析する手段と、解析結果をもとにマルチ処理部を抽出する手段と、抽出した部分をコントロールするCDFGを生成する手段と、CDFG、DFGに対してクロック・サイクルのスケジュールや構成を決定する手段と、スケジューリング、アロケーションされたRTレベルの回路を生成する手段とを備える。

(もっと読む)

検証支援プログラム、検証支援装置および検証支援方法

【課題】対象回路内の依存関係をもつ2つのノード間の信号の伝播に要する時間を、シミュレーションを実行することなく容易に特定する。

【解決手段】検証支援装置100によって、入力値110として調査対象変数(信号やレジスタ)111およびクロック信号名112と、それらを定義・参照しているRTLのソースコード113が入力されると、調査対象変数111についての遅延サイクル数121を出力値120として出力する。検証支援装置100では、RTLのソースコード113における調査対象変数111のパス上のノードを各ノードのクロックドメインごとに検出することによって遅延サイクル数121を特定できる。

(もっと読む)

121 - 140 / 1,280

[ Back to top ]