Fターム[5B046BA03]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 回路設計 (1,280)

Fターム[5B046BA03]に分類される特許

101 - 120 / 1,280

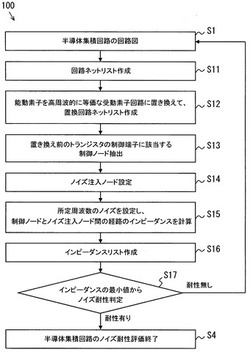

半導体集積回路のノイズ耐性評価方法およびノイズ耐性評価装置

【課題】大規模な半導体集積回路であってもノイズ耐性評価が短時間で可能なノイズ耐性評価方法を提供する。

【解決手段】回路ネットリストを作成する第1のステップS11と、能動素子を受動素子回路に置き換えて置換回路ネットリストを作成する第2のステップS12と、トランジスタの制御端子に該当する制御ノードを抽出する第3のステップS13と、ノイズ注入ノードを設定する第4のステップS14と、所定周波数のノイズを設定し、互いに異なる制御ノードとノイズ注入ノード間の経路のインピーダンスを計算する第5のステップS15と、制御ノード、ノイズ注入ノードおよび経路の各組み合わせにおけるインピーダンスのリストを作成する第6のステップS16と、インピーダンスの最小値から半導体集積回路のノイズ耐性を判定する第7のステップS17とを有してなるノイズ耐性評価方法100とする。

(もっと読む)

エラー信号パルス幅の計算方法及び計算装置及び計算プログラム

【課題】従来、計算負荷が大きいまたは計算時間が長くかかっていた。

【解決手段】ロジックセルを構成する第1のトランジスタの拡散層近傍に荷電粒子が入射した場合に、前記拡散層に接続された前記ロジックセルの第1の端子に生じる電圧パルス幅を算出する方法であって、前記第1の端子における電圧を固定した条件の下で荷電粒子が入射した場合に観測される前記第1の端子への電荷収集電流波形と、前記ロジックセルの前記第1の端子に接続される第2のトランジスタの電流駆動能力指標と、から前記第1の端子に生じる前記電圧パルス幅を算出することを特徴とするパルス幅計算方法。

(もっと読む)

回路設計支援装置、回路設計支援装置の制御方法および回路設計支援装置の制御プログラム

【課題】回路設計の検証を高速にすること。

【解決手段】回路設計支援装置1は、記憶部1aと選択部1bとトレース部1cと制御部1dとを有する。記憶部1aは、回路の回路接続情報2を記憶する。選択部1bは、入力端子から入力した信号をクロック信号に基づき保持して出力端子から出力する記憶素子を、回路接続情報2から選択する。トレース部1cは、回路接続情報2に基づき、選択した記憶素子の入力端子から論理接続のトレースを、信号の伝搬方向とは逆方向に向かって行う。制御部1dは、トレース部1cが論理接続のトレースを行うことにより、到達した素子の入力端子数が2以上である場合、トレース部1cによるトレースを停止する。

(もっと読む)

シミュレーション装置

【課題】 本発明の課題は、シミュレーションにより取得したトレースデータを用いて、変更可能な制約条件を付加して再シミュレーションするシミュレーション装置を提供することを目的とする。

【解決手段】 上記課題は、シミュレーションで取得した対象回路の動作に係る複数のプロセスに関するイベント情報を含む第一トレースデータと該対象回路の動作を再現するための動作モデルとを格納した記憶領域と、ユーザによる前記複数のプロセス間に対する制約条件の変更設定を適応させて、前記第一トレースデータに基づいて前記動作モデルを用いて再シミュレーションし、該再シミュレーションによる第二トレースデータを出力する再シミュレーション手段と、を有することを特徴とするシミュレーション装置により達成される。

(もっと読む)

設計記述書換装置およびその方法

【課題】デジタル回路の設計記述の開発および検証を効率化することを可能にする。

【解決手段】本発明の一態様としての設計記述書換装置は、設計記述と、書換指示データと、書換起点位置同定部と、時間消費命令探索部と、時間消費命令分割部と、設計記述追加部と、出力部とを備える。設計記述は、時間消費命令を含む複数の命令を有する。書換指示データは、書換起点命令と、経過時間と、設計記述に追加すべき追加命令と、を指定する。時間消費命令探索部は、設計記述において、書換起点命令から設計記述を実行方向に探索し、実行中に経過時間が経過することとなる時間消費命令である分割対象命令を検出する。時間消費命令分割部は、分割対象命令を元に、第1および第2時間消費命令を生成する。設計記述追加部は、設計記述において、分割対象命令を第1および第2時間消費命令に置換し、追加命令を第1および第2時間消費命令の間に追加する。

(もっと読む)

半導体集積回路のシミュレーション装置、シミュレーション方法およびシミュレーションプログラム

【課題】検証対象の回路が要求特性を満たしているか否かを、製造ばらつきを考慮して短時間で実行。

【解決手段】回路のネットリストを格納する回路情報格納部10と、検証する第1回路特性の種類を提供する検証項目提供部20と、各種素子の特性を、製造ばらつき範囲の下限値、Typ値、上限値の複数のパラメータファイルを格納するパラメータ格納部40と、回路に含まれる第1素子及び第2素子のそれぞれに対して、最小値用又は最大値用ばらつき項目リスト生成部50と、最小値と最大値との少なくとも一方を検証することを含むシミュレーション条件提供部60と、最小値と最大値との少なくとも一方を検証する情報に基づいて、製造ばらつき情報を生成する製造ばらつき情報生成部70と、製造ばらつき情報と、ネットリストと、シミュレーション条件とに基づいて、回路シミュレーションを実行する回路シミュレーション実行部90とを具備する。

(もっと読む)

ESD検証装置、ESD検証方法およびESD検証プログラム

【課題】半導体回路内のパッド間の電流の流れやすさを精度よく解析する。

【解決手段】ESD保護素子が接続された2つのパッド間の一方側から他方側に流れる電流の流れ易さを数値化した第1テーブル作成手段と、反対向きの電流の流れ易さを数値化した第2テーブル作成手段と、第1及び第2テーブルを合成して、最も電流が流れ易い経路を数値化した第3テーブル作成手段と、第3テーブルに基づいて、任意のパッド間で、ESD保護素子を経由する全経路について、電流の流れ易さを数値化した第4テーブル作成手段と、全ESD保護素子を削除した状態で、任意のパッド間の電流の流れ易さを数値化した第5テーブル作成手段と、第4及び第5テーブルとに基づいて、任意のパッド間で、ESD保護素子を通過する経路と通過しない経路の電流の流れ易さの比較結果が一致しない場合に、対応するパッド同士の組合せと、パッド間の経路とを提示する手段4と、を備える。

(もっと読む)

半導体集積回路の自動検証装置、検証方法

【課題】カレントミラー回路を構成するMOSFETの抽出、検証、表示を自動化する。

【解決手段】回路接続情報(ネットリスト)7に基づいて、まずステップS01の「カレントミラー抽出用データベース作成処理」を行い、続いてステップS02の「コピー元およびコピー先候補のMOSFETのデータベース作成処理」を行い、次にステップS03の「極性の等しいMOSFETのデータベース作成処理」を実行し、更にステップS04の「カレントミラー回路を構成するMOSFETの回路定数の比較検証処理」を実行する。

(もっと読む)

最適化ネットリスト作成プログラム、最適化ネットリスト作成装置および最適化ネットリスト作成方法

【課題】RTL内で複数回インスタンスとして使用されたモジュールについて非ユニーク状態でネットリストを生成し、全てのケースを網羅したタイミングの最適化を行なうこと。

【解決手段】パス選択部11は、バイオレーションデータベースD11と対応表D12を参照し、インスタンスの名称とモジュールの名称が一致するパスを選択する。対応表D12は、論理合成時に非ユニーク化される前のモジュールと論理合成後のインスタンスのパスとを対応づけたデータである。バイオレーションデータベースD11は、インスタンスのパスについてのタイミング違反の値を保持する。パス選択部によって選択されたパスをバイオレーション比較部12が比較し、バイオレーションデータがワーストのパスを残して他のパスを削除する。残ったモジュールについてタイミング最適化部13がタイミングの最適化を行って最適化ネットリストを作成する。

(もっと読む)

ライブラリ情報漏洩防止装置、ライブラリ情報漏洩防止方法及びライブラリ情報漏洩防止プログラム

【課題】計算機利用設計で用いるライブラリ情報の過度な漏洩を容易に防止できるライブラリ情報漏洩防止装置、ライブラリ情報漏洩防止方法及びライブラリ情報漏洩防止プログラムを提供することを課題とする。

【解決手段】ライブラリ情報漏洩防止装置であって、入力された設計データに含まれるライブラリ情報の項目を入力項目一覧データに登録する入力処理手段31と、入力項目一覧データ62を保持する入力項目一覧データ保持手段と、出力する設計データに含ませるライブラリ情報の項目を、入力項目一覧データ62に登録したライブラリ情報の項目に合わせる出力処理手段33とを有することにより上記課題を解決する。

(もっと読む)

回路性能見積装置、回路性能見積方法及び回路性能見積プログラム

【課題】回路性能見積もりの精度と処理時間とのバランスを図ることができる回路性能見積装置、回路性能見積方法及び回路性能見積プログラムを提供することを課題とする。

【解決手段】モデル式によるシミュレーションで回路性能を見積もるコンピュータに、回路性能とパラメータとの関係を示すモデル式に含まれる項が記録されている記録手段45から項を取得して、項の組み合わせで新たなモデル式を生成するステップと、新たなモデル式でシミュレーションを行い、精度要求を満たすモデル式を選択するステップとを実行させる回路性能見積プログラムにより上記課題を解決する。

(もっと読む)

シミュレーションネットリスト作成装置、シミュレーションネットリスト作成方法、及びコンピュータプログラム

【課題】 回路における電源制御に関するシミュレーションの時間を削減する。

【解決手段】 回路を構成する部品の「部品情報110、端子情報120、及び端子間の接続情報100」に基づき、探索開始部品を特定する。そして、探索開始部品の電源端子及びリセット端子と、電源回路の制御ネット名とを探索始点とする。また、電源回路の入出力ネット名と、電源ネット名と、グランドネット名と、部品情報110に基づいて特定される探索終了部品とを探索終点とする。そして、探索始点から探索終点までの探索経路にある部品を探索し、当該部品の接続情報を特定し、探索経路にある部品のシミュレーションネットリストを作成する。

(もっと読む)

設計支援装置、設計支援方法および設計支援プログラム

【課題】比較的少ない情報で設計対象の回路の検証を可能とすること。

【解決手段】設計支援装置1は、抽出部1aと、作成部1bと、修正部1cとを有している。抽出部1aは、複数の層2a〜2cを有する基板モデル2の層2aに配置される一対の信号伝送回路モデル3a、3bの信号伝送に関連する範囲2dを、電源層およびグランド層から抽出する。作成部1bは、与えられる制約条件に基づいて、抽出部1aにより抽出された範囲2dを加工した層モデル2fを作成する。修正部1cは、作成された層モデル2fに基づいて、基板モデル2を修正する。

(もっと読む)

設計支援装置及び設計支援方法

【課題】設計者が迅速、且つ正確に設計変更箇所の確認を行う事ができる設計支援装置及び設計支援方法を提供する。

【解決手段】回路の変更前の情報と回路の変更後の情報とを記憶する記憶手段と、変更前の情報と変更後の情報とに基づき、回路の変更前後における、回路の論理情報における差異と回路の物理情報における差異とを抽出する抽出手段と、回路とともに、回路の論理情報の差異と回路の物理情報の差異との出力も行う出力手段と、を有する。

(もっと読む)

ハードウェア/ソフトウェア協調シミュレーション装置及びそのデバッグ方法

【課題】シミュレーション時間を短縮可能なハードウェア/ソフトウェア協調シミュレーション装置等を提供すること。

【解決手段】本発明にかかるハードウェア/ソフトウェア協調シミュレーション装置は、ードウェアエミュレータとシステムシミュレータとを備え、ハードウェアエミュレータは、複数のユーザデータを生成するユーザロジックと、複数のユーザデータの変化をそれぞれ検出する複数の変化検出回路と、複数の変化検出回路による検出結果をそれぞれ格納する複数のフリップフロップと、複数のフリップフロップに格納された複数の検出結果に応じた終了フラグ信号を生成する論理和回路と、を備える。システムシミュレータは、終了フラグ信号に基づいて複数のユーザデータのいずれかが変化したと判断した場合に複数のユーザデータを順に読み込み、各ユーザデータの読み込みの終了に応じて対応するフリップフロップをクリアさせる。

(もっと読む)

情報処理装置、プログラム、および設計支援方法

【課題】設計対象の集積回路内での回路特性のばらつきに伴う遅延時間の変動を反映したタイミング解析技術を提供する。

【解決手段】情報処理装置は、複数の回路素子を含む対象経路の信号伝搬時間を変化させる物理特性値を所定の変動範囲で複数個発生させる物理特性値発生部と、発生させた物理特性値にしたがって、回路素子を通る信号の遅延時間を算出する素子遅延算出部と、信号の遅延時間を基に対象経路の信号伝搬時間を算出する伝搬時間算出部と、を備える。

(もっと読む)

半導体装置のシミュレーション方法及び装置

【課題】電気特性と熱特性の相互の影響を反映した電気-熱連携解析を短い計算時間で実行し、正確な解析結果を得る半導体装置のシミュレーション方法及び装置を提供する。

【解決手段】まず電気特性解析を実行する(ステップS1)。次に電流特性とチップ損失特性の平均化を実行する(ステップS2)。そしてモジュールの3次元形状モデルを作成し、第1の平均化式により得た平均化した電流値を3次元形状モデルの端面に設定してジュール損失解析を実行する(ステップS3)。そして上記ジュール損失解析と第2の平均化式で算出したチップ損失の平均値とを用いて発熱量が等しく時間ステップの長い熱解析特性データを得る(ステップS4)。温度変化が一定値以上に達した時点で電気特性解析のジャンクション温度を再設定し(ステップS5)、以降、電気特性解析から平均化、熱解析までの解析フローを繰り返して装置動作時の温度特性を得る(ステップS11〜S15)。

(もっと読む)

集積回路設計装置及び集積回路設計方法

【課題】クロック線上における消費電力を効果的に抑えることが可能な集積回路を設計する集積回路設計装置を提供する。

【解決手段】開示の装置は、消費電力算出手段と、消費電力比較手段と、クロックツリー生成手段とを備える。消費電力算出手段は、クロック線上における、クロックゲーティングセルをクロックソース側及びクロックシンク側に配置した場合の第1及び第2の消費電力を算出する。クロックツリー生成手段は、第1及び第2の消費電力の比較により、消費電力が小さいと判定された方の配置の仕方で、クロックゲーティングセルをクロック線上に配置する。ここで、消費電力算出手段は、クロックゲーティングセルのイネーブル率と、クロック線上における消費電力のダイナミック電力成分とスタティック電力成分との比率と、に基づいて、第1及び第2の消費電力を算出する。

(もっと読む)

半導体集積回路の設計装置および設計方法

【課題】回路規模の増大を抑制しつつスキャンテスト時の消費電力を削減する半導体集積回路の設計装置および設計方法を提供する。

【解決手段】対象抽出部102は、組み合せ回路のうちの活性化状態が評価される対象となる回路部分を抽出する。削減量算出部104は、組み合せ回路に入力されるスキャンフリップフロップのそれぞれの出力信号を1個ずつ固定化してスキャンフリップフロップ毎の消費電力の削減量を算出し、評価部108は、その結果に基づいて、スキャンフリップフロップの出力信号を固定化したときの消費電力の削減量が最も多いスキャンフリップフロップを選択する。固定化情報蓄積部106は固定化情報を保持し、対象抽出部102はその固定化情報に基づいて、評価対象となる回路部分を抽出する。評価部108は、抽出された回路部分毎に1つのスキャンフリップフロップを選択し、削減できる消費電力値の合計が所定の値になるまで上記を繰り返す。

(もっと読む)

論理検証装置および論理検証方法並びにプログラム

【課題】RTL検証によりグリッジの有無を判断する。

【解決手段】検出部110は、RTLデータが示す論理回路における各FFについて、該FFのクロック端子とリセット端子を夫々起点として、該起点の端子に入力される信号の入力経路を遡って、PLL回路と、他のFFと、外部端子とのうちのいずれかに辿りつくまで、複数入力の論理ブロックを検出する。RTLシミュレータ120は、上記RTLデータと、検証用の信号パターンとが入力され、検出部110により検出された各論理ブロックについて、該論理ブロックの複数の入力の変化タイミングを取得する。判断部130は、検出部110により検出された各論理ブロックについて、該論理ブロックの複数の入力の変化タイミング間の差と閾値とを比較することにより、グリッジの有無を判断する。

(もっと読む)

101 - 120 / 1,280

[ Back to top ]