Fターム[5B046BA03]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 回路設計 (1,280)

Fターム[5B046BA03]に分類される特許

21 - 40 / 1,280

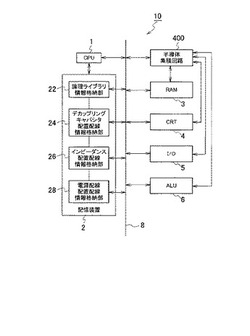

半導体集積回路システムおよび半導体集積回路システムの配置配線方法

【課題】EMI低減に有効な半導体集積回路システムを提供する。

【解決手段】バスライン8上に配置された中央演算処理装置1と、演算論理装置6と、デカップリングキャパシタ形成領域100・合成論理形成領域200・インピーダンス形成領域300を有する半導体集積回路400と、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26・電源配線配置配線情報格納部28を有する記憶装置2とを備え、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26のそれぞれの格納データに基づいて、それぞれ合成論理形成領域200・デカップリングキャパシタ形成領域100・インピーダンス形成領域300における配置配線を実行する半導体集積回路システム10。

(もっと読む)

検証支援プログラム、検証支援方法、および検証支援装置

【課題】シミュレーション時間の短縮化を図ること。

【解決手段】検証支援装置が、検証対象回路の回路情報に所定入力パターンを与えるシミュレーション101のうちの(1)の実行中に、CDCジッタJ1を検出する。検証支援装置が、CDCジッタJ1の検出時のシミュレーション101の実行状態を複製する。検証支援装置が、複製されたシミュレーション101の実行状態のうちの第2のクロックドメイン内の素子の出力を、検出された出力値と異なる論理値に設定する。検証支援装置が、設定後の実行状態に基づくシミュレーション102(第2のシミュレーション)をシミュレーション101と排他的に実行する。論理シミュレータは複数のシミュレーションを並列実行できないため、論理シミュレータがいずれか一方のシミュレーションを実行中には他方のシミュレーションの実行は待機する。

(もっと読む)

消費電力計算方法および装置

【課題】長時間のシミュレーションによる消費電力の見積もりを実現する。

【解決手段】消費電力計算装置は、回路のアクティブな消費エネルギーとフレーム長との関係を近似した近似式を導出する近似式導出部2と、回路のスタティックな消費エネルギーE_staticを算出するスタティック消費エネルギー算出部3と、入力フレームを発生させるフレーム入力部4と、フレーム長を取得するフレーム長取得部5と、近似式にフレーム長を代入して回路のアクティブな消費エネルギーE_iを算出するアクティブ消費エネルギー算出部6と、全てのフレームについて消費エネルギーE_iを積算したエネルギーE_activeを算出するアクティブ消費エネルギー積算部7と、消費エネルギーE_activeとE_staticとの合計をシミュレーション時間で除算して平均消費電力を算出する平均消費電力算出部8とを備える。

(もっと読む)

クロック・ネットワーク・メタ合成のためのシステムおよび方法

【課題】クロック到着時間の同時性を保証するクロック分配ネットワークの設計を容易にする。

【解決手段】クロック・ネットワークを構築する方法は、クロック・ネットワークについての設計仕様を受け取る段階を含む。本方法はさらに、前記設計仕様に基づいて前記クロック・ネットワークのトポロジーを決定する段階を含む。本方法はさらに、決定されたトポロジーに基づいて前記クロック・ネットワークについての設計パラメータを決定し、前記設計パラメータを含むクロック・ネットワーク合成ツール仕様ファイルを生成することを含む。本方法はまた、前記仕様ファイルを使って、前記クロック・ネットワークが前記決定されたトポロジーを含み、前記クロック・ネットワークがクロック発生器から前記クロック・ネットワークのエンドポイントまでクロック信号を同期的に分配するよう、前記クロック・ネットワークを合成することを含む。

(もっと読む)

歩留り算出のためのプログラム、情報処理方法及び装置

【課題】サンプル点間の支配関係に基づく歩留り率を高速に算出する。

【解決手段】本方法は、複数のサンプル点の複数種類の性能項目値を、当該複数種類の性能項目で張られる空間を分割することで得られる複数のメッシュ要素のうち該当するメッシュ要素の座標値に変換する工程と、複数のサンプル点の座標値の集合を表現する二分決定グラフを生成する工程と、複数のサンプル点に含まれる第1のサンプル点の各座標値以下の座標値に対応するノードを、二分決定グラフにおける根ノードから1を表す葉ノードに至るパスの数を計数することで、複数のサンプル点のうち第1のサンプル点を支配する第2のサンプル点及び第1のサンプル点の数を算出する工程と、算出された数を上記複数のサンプル点の数で除することで、第1のサンプル点の歩留り率を算出する工程とを含む。

(もっと読む)

回路動作の検証装置及び回路動作の検証方法

【課題】電圧規格や電流規格を満たさない箇所があった場合に、その影響を反映させて検証を行うことができる回路動作の検証装置を提供する。

【解決手段】回路動作の検証装置は、結線情報4と、定格情報6とを用い、回路に入力する信号パターン7が与えられると、その入力パターン7に基づいて回路動作を検証する(S1〜S5)。そして、検証の結果、回路素子に印加される電圧や通電される電流等が定格値を超えることで破壊に至る回路素子が存在すると、当該回路素子を破壊の態様に応じた破壊状態モデルに置換し(S6)、破壊状態モデルに置換した回路について検証を継続する。

(もっと読む)

消費電流算出装置、消費電流算出プログラムおよび消費電流算出方法

【課題】ミックスドシグナル回路の消費電流を短時間で見積もること。

【解決手段】消費電流算出装置100は、対象回路へ入力されるデジタル信号の値113と、デジタル信号とともに対象回路へ入力されるアナログ信号の値112と、を取得する。消費電流算出装置100は、デジタル信号の値113およびアナログ信号の代表値の組み合わせごとに組み合わせが入力された場合の対象回路の消費電流を示す消費電流テーブル114から、デジタル信号の値113が対象回路へ入力された場合のアナログ信号の各代表値と消費電流との対応情報115を抽出する。消費電流算出装置100は、抽出した対応情報115に基づいて、アナログ信号の各代表値の間の値に対応する対象回路の消費電流を補間する補間関数116を生成し、生成した補間関数116に基づいて、アナログ信号の値112に対応する対象回路の消費電流117を算出する。

(もっと読む)

シミュレーション装置、シミュレーションプログラムおよびシミュレーション方法

【課題】簡易にシミュレーションを行うこと。

【解決手段】シミュレーション装置10は、記憶部13と、実行部14bと、比較部14cと、出力部14dとを有する。記憶部13は、電圧の変化、伝送線路に係るパラメータを記憶する。実行部14bは、パラメータを用いて、伝送線路における電圧の変化のシミュレーションを実行する。比較部14cは、記憶された電圧の変化と、実行部14bにより得られたパラメータの電圧の変化との間で、次のような比較を行う。すなわち、比較部14cは、電圧が所定の閾値以上になってから所定の時間長までにおける変化、電圧が所定の閾値未満になってから所定の時間長までにおける変化の少なくとも一方を比較する。出力部14dは、比較部14cによる比較の結果に基づいて、電圧の変化が類似する場合におけるシミュレーションに用いられたパラメータを出力する。

(もっと読む)

検証装置、検証方法及びプログラム

【課題】検証する範囲を少なくして、検証コストや検証時間の増大を抑制する。

【解決手段】抽出部12が、第1のクロック信号で動作する回路部21と、第2のクロック信号で動作する回路部22とを含む検証対象回路(論理回路20)から、ハンドシェイクの手順に従って回路部21と回路部22間でのデータの送受信を行うハンドシェイク部23を抽出し、検証部13が抽出されたハンドシェイク部23の信号が、その手順を満たすかを検証し、手順を満たさない信号があるとき、回路部21と回路部22のうち当該信号を出力する側で、当該信号が手順を満たさなくなる条件が回路動作時に起こり得るか検証する。

(もっと読む)

非同期インターフェース検証装置、非同期インターフェース検証方法及びそのプログラム

【課題】RTLでの非同期インターフェースの検証を可能とする。

【解決手段】非同期インターフェース検証装置は、タイミング変更部120と、シミュレーション部121とを具備している。タイミング変更部120は、非同期インターフェースのRTL(Register Transfer Level)検証において、RTL100における非同期インターフェースの同期化部(F/F)の動作タイミングをクロックサイクルベースで変化させる。シミュレーション部121は、前記動作タイミングを変化させたRTLを用いてシミュレーションを実行し、非同期インターフェースが正常な動作をするか否かを検証する。

(もっと読む)

LSI設計方法,設計プログラムおよび設計装置

【課題】従来のLSI設計フローではクロックの遅延やスキューが無いことを前提とするため,クリティカルパスにてタイミングが仕様を満たさないことがSTA後に判明する。

【解決手段】ハードウェア記述ファイルと制約条件ファイルとから第1のクロックと第2のクロックのそれぞれのクロックツリーによる想定遅延値をそれぞれ生成し,第1のクロックと第2のクロックの想定遅延値をもとにしてクリティカルパスをデータベースへ登録するデータベース構築工程と,ハードウェア記述ファイルと制約条件ファイルについて論理合成を行うとともに,クリティカルパスをそれ以外のパスよりも優先して最適化し,ネットリストを生成する論理合成工程とを有するLSI設計方法。

(もっと読む)

半導体装置の設計方法、設計装置、及び半導体装置

【課題】スキャンフリップフロップ回路の所定の論理値になる確率を考慮することで、消費電力の削減を図る。

【解決手段】スキャンフリップフロップ回路のキャプチャ動作後の出力値が所定の論理状態になる確率を解析する解析処理(S31)と、この解析処理の結果に基づいて、キャプチャ動作後の出力値が所定の論理状態になる確率が同程度の複数のスキャンフリップフロップ回路毎にスキャンチェインを構築するスキャンチェイン構築処理(S32)とを演算処理部(3)に実行させる。スキャン動作時の遷移確率が低下されたスキャンチェインが形成されることによって、スキャンテスト時の消費電力の低減を図ることができる。

(もっと読む)

LSIの回路図復元装置

【課題】レイアウトパターンの任意の一部分の回路図を正確に復元する。

【解決手段】レイアウトパターン表示部400により、格納部200,300内に格納されているブロック/セルという階層構造をもったデータを展開して、画面上にレイアウトパターンを表示する。セル枠決定部600は、条件設定部800内のセル枠決定条件に基づく特定の図形群の外接図形として、表示中のレイアウトパターン上に仮想のセル枠を決定する。端子点決定部500は、このセル枠とセル間配線との交差位置に端子点を決定する。回路復元部700は、条件設定部800内の領域認識条件および素子認識条件に基づき、セル枠内の図形に対して、素子構成領域の認識を行い、認識した各領域と端子点との相互の接続関係に基づいて素子の認識を行い、認識した素子の接続関係を回路図として表示する。

(もっと読む)

配線抵抗網作成装置および配線抵抗網作成方法

【課題】配線形状の複雑化に起因するエレクトロマイグレーション解析の処理時間の増加を抑制する。

【解決手段】配線パターン分割部(22)と、ビア部分抵抗網設定部(25)と、配線部分抵抗網設定部(24)と、配線抵抗・ビア抵抗接続部(28)を有する配線抵抗網作成装置(10)を構成する。配線パターン分割部(22)は、レイアウトデータからビアとの接続位置情報を含む配線パターンを取得し、配線パターンをアレイビア部分と配線部分に分割する。ビア部分抵抗網設定部(25)は、アレイビア部分に対応するビアノードおよびビア部分抵抗を含むビア部分抵抗網を設定する。配線部分抵抗網設定部(24)は、配線部分に対応する配線ノードおよび配線部分抵抗を含む配線部分抵抗網を設定する。配線抵抗・ビア抵抗接続部(28)は、ビア部分抵抗網と配線部分抵抗網を接続して配線抵抗網データを生成する。

(もっと読む)

半導体集積回路及びその設計方法

【課題】半導体集積回路の外部端子としてTRSTがなくても、論理シミュレーションの際に、タップコントローラのステートを確定する。

【解決手段】タップコントローラ2は、リセット端子(端子p4)を有し、回路部3は、タップコントローラ2における状態遷移を制御するステート制御信号と、クロック信号を入力し、ステート制御信号とクロック信号に応じて、リセット端子p4にリセット信号を供給することで、タップコントローラ2のステートを確定する。

(もっと読む)

半導体装置設計方法および半導体装置設計支援プログラム

【課題】EBDに近いモデリング精度を維持しつつ、モデリングの効率を高める。

【解決手段】複数のチップ(CHIP1〜4)が積層され、それぞれのチップが共通の外部端子104に接続される積層型の半導体装置100の設計に関する。まず、電磁界解析ツールにより、外部端子104とチップを接続するプリント基板配線(共通配線106、個別配線108)の電気的なパラメータを算出し、それらをEBDのパラメータとして設定する。設定されたパラメータに基づいて半導体装置100の電気的な特性をシミュレーション計算する。パラメータの計算・設定に際しては、所定の配線、たとえば、共通配線106や個別配線108などのプリント基板配線の長さを示すパラメータをゼロに設定する。

(もっと読む)

論理セルのアナログモデルを生成する方法、製品及びコンピュータシステム

【課題】有効なレベルの検証を依然として保ちながら検証の複雑性を低減する方法等を提供する。

【解決手段】方法は、論理セルについて、論理セルの入力遷移に応答して起こる論理セルの出力遷移を示す少なくとも1つのエントリを含む論理遷移データを、論理セルのデジタルモデルの解析に基づき生成するステップを有してよい。方法は、論理セルについて、論理遷移データの各エントリに関連付けられた遷移タイミングパラメータを含む、パラメータ化された遷移に基づくアナログモデルを生成するステップを更に有してよい。方法は、論理セルについて、パラメータ化された遷移に基づくアナログモデルと、論理セルを特徴付ける1又はそれ以上のアナログネットリストとに基づき、アナログモデルを生成するステップを更に有してよい。

(もっと読む)

半導体集積回路装置の解析方法

【課題】半導体集積回路装置に含まれる回路素子および寄生素子の中から電位変動の発生源から観測点への電位変動の伝播経路の要因となる素子を容易に特定する。

【解決手段】半導体集積回路装置に含まれる回路素子および寄生素子の各々の電位変動量が登録された素子電位変動情報(11)と回路素子および寄生素子の各々の配置位置が登録された素子配置情報(12)とを入力する。素子電位変動情報(11)および素子配置情報(12)を参照して、回路素子および寄生素子の中から予め設定された電位変動閾値よりも大きい電位変動量に対応する素子を選別し、選別された素子の電位変動量および配置位置を示す情報を素子選別情報(10)に登録する。

(もっと読む)

多出力電源回路の設計方法及び多出力電源回路の設計装置

【課題】少ない工数で高効率の電圧コンバータの組み合わせを探索できる多出力電源回路の設計方法及びその設計装置を提供する。

【解決手段】複数の電源ドメインに出力電源を供給する多出力電源回路の設計方法は,入力電源(根)と複数の出力電源(葉)との間に電圧コンバータを有するツリー構造をランダムに生成する工程とそのツリー構造の多出力電源回路の電力効率を計算する工程とを,とりうる全てのツリー構造の数より少ない回数だけ繰り返し,最良の電力効率を有するツリー構造を探索する。さらに,前記探索工程で見つけたツリー構造のうち任意の出力電圧を出力する電圧コンバータ以前の入力側の複数の電圧コンバータを有する入力側ツリー構造について,前記探索工程を再度行い,当該探索で検出されたより良いコスト関数値を有する入力側ツリー構造に置き換える改善を行う。改善工程を任意の出力電圧を順次入力側に移動して繰り返す。

(もっと読む)

素子モデル、素子モデル作成方法、回路検証方法、及び回路検証装置

【課題】回路検証手段によらず素子の制限特性の検証を容易に行うことができる素子モデル、素子モデル作成方法、回路検証方法、及び回路検証装置を提供する。

【解決手段】少なくとも1つの素子で構成された回路の動作を検証するためのシミュレーションで使用される前記素子をモデル化した素子モデルであって、前記素子の固有の物理特性を定義した物理特性定義部と、前記素子の固有の物理特性を用いた電気的特性であって前記シミュレーションを行う電気的特性を定義する電気的特性定義部と、前記素子の固有の物理特性に応じた電気的特性の制限を示す制限特性を定義した制限特性定義部と、前記シミュレーション中に、前記素子の固有の物理特性に応じた電気的特性が前記制限特性に違反しているか否かを検証するための処理内容を示す制限特性検証部と、を含む素子モデルを作成する。

(もっと読む)

21 - 40 / 1,280

[ Back to top ]