Fターム[5B046BA04]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 実装設計、レイアウト設計 (2,049)

Fターム[5B046BA04]の下位に属するFターム

割付、配置、ネスティング (289)

ルート探索、配線 (682)

Fターム[5B046BA04]に分類される特許

1,061 - 1,078 / 1,078

集積回路製作におけるデルタ情報設計クロージャ

集積回路(「IC」)製作におけるタイミングドリブンの形状クロージャのためのシステム及び方法が提供される。これらの統合設計製造工程(「IDMP」)は、IC製作のタイミング及びジオメトリ検証工程の情報をIC設計に統合するデルタフローを含む。デルタフローは、回路特徴パラメータに関する差分情報を処理するためのデルタ−ジオメトリタイミング予測工程及び/又はデルタ−タイミング形状予測工程を含むインクリメンタルフローである。デルタフローは、回路特徴パラメータに対応する差分又はデルタ情報を用いてIC設計を独自に再特徴付けする。デルタフローは、新しい回路特徴パラメータを生成する必要がなく、更にIC設計の全ての情報を再処理することを必要とせずに、デバイス及び相互接続構造部の対応するパラメータを強調又は再特徴付けするデルタ出力(インクリメンタルの)を提供する。 (もっと読む)

集積回路製作におけるデルタジオメトリタイミング予測

集積回路(「IC」)製作におけるタイミングドリブンの形状クロージャのためのシステム及び方法が提供される。これらの統合設計製造工程(「IDMP」)は、IC製作のタイミング及びジオメトリ検証工程の情報をIC設計に統合するデルタフローを含む。デルタフローは、回路特徴パラメータに関する差分情報を処理するためのデルタ−ジオメトリタイミング予測工程及び/又はデルタ−タイミング形状予測工程を含むインクリメンタルフローである。デルタフローは、回路特徴パラメータに対応する差分又はデルタ情報を用いてIC設計を独自に再特徴付けする。デルタフローは、新しい回路特徴パラメータを生成する必要がなく、更にIC設計の全ての情報を再処理することを必要とせずに、デバイス及び相互接続構造部の対応するパラメータを強調又は再特徴付けするデルタ出力(インクリメンタルの)を提供する。 (もっと読む)

電子回路設計プログラム、電子回路設計方法および電子回路設計装置

設計対象の全電子回路(セル)のうち一部の電子回路に関するノイズ値を計算し、該ノイズ値が制限値を超えた場合、所定の方法により、該ノイズ値が制限値以下となるように電子回路のパラメータ(平行区間長、平行区間隣接距離等)を変更し(簡易ノイズチェック)、全電子回路について、信号伝送のタイミングを解析し、タイミングが解析済みの全電子回路に関するノイズ値を計算し、該ノイズ値が制限値を超えた場合、簡易ノイズチェックを実行させる。  (もっと読む)

(もっと読む)

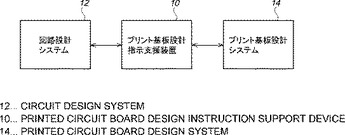

プリント基板設計指示支援方法およびその装置

プリント基板設計作業効率の向上ならびにプリント基板設計品質の向上に資する回路設計とプリント基板設計間におけるプリント基板設計指示支援方法、回路設計とプリント基板設計間におけるプリント基板設計指示支援装置、Webシステム、プログラムおよびコンピューター読み取り可能な記録媒体を提供するものであり、設計ルールが適用される回路部品を選択すれば、回路設計システムとプリント基板設計システムとの連携により、回路図とプリント基板上のチェック対象部分とを同時に表示して、チェック時間の短縮と手間を低減するようにした。  (もっと読む)

(もっと読む)

集積回路チップ内のボルテージアイランド上で電力ルーティングを行なうための方法、コンピュータープログラム、およびシステム

【課題】集積回路チップ内のボルテージアイランド上で電力ルーティングを行なう方法を提供する。

【解決手段】第1の電力網(31)は、金属レベル1からN1においてボルテージアイランドのために生成される。次いで、第2の電力網は、金属レベルN以上(32)において生成される。前記第2のロバスト電力網の境界領域が決まる(33)。最後に、1セットの電源からの最短距離接続は、前記第2の電力網(34)に対してルートが決められる。

(もっと読む)

製造を容易にする設計

【課題】製造容易性を改善するために、既存の超小型装置設計を変更する技術を提供する。

【解決手段】これらの技術により、設計者は、設計に於けるデータに関連した製造基準を受領する。次に、関連した設計データが識別されて、超小型装置設計者へ供給され、該設計者は、製造基準に基づいて設計変更を選択することが出来る。このようにして、設計者は、超小型装置の元の設計に於いて、半導体ファンドリからの製造基準を直接的に包含させることが出来る。

(もっと読む)

プリント配線基板製造方法及びプリント配線基板、並びに特性インピーダンス算出装置、特性インピーダンス算出方法、及び特性インピーダンス算出プログラム

【課題】 実測値と極めて高精度での一致を実現するマイクロストリップライン及びストリップラインの特性インピーダンスを算出する新たな算出式を提案し、この算出式を用いてプリント配線基板の製造を行う。

【解決手段】 プリント配線基板を製造する際の製造プロセスにおいては、ステップS1において、コンピュータを用いたシミュレーションに基づく導体パターンを設計して特性インピーダンスのシミュレーション値を算出する。このとき、製造プロセスにおいては、ステップS1において、少なくとも、導体パターン幅、導体パターン厚、及び絶縁層厚をパラメータとするとともに、これらパラメータに対して所定の係数を乗じて補正することによって表される実効導体パターン幅を導入し、実効導体パターン幅の関数として、特性インピーダンスのシミュレーション値を算出する。

(もっと読む)

プリント基板設計法およびプリント基板

【課題】スイッチング電源を実装するプリント基板において、部品点数を増加させることなくリンギングノイズを低減させる。

【解決手段】スイッチング電源のリンギングノイズが伝達するループ1を決定し、そのループ1の中で、寄生インダクタンスおよび寄生キャパシタンスを大きくできるプリントパターンp10を決定し、そのラインインダクタンスを調整する。そのときのリンギングノイズの周波数はそのループ1の固有周波数から求める。部品点数を増やすことなくプリントパターンp10のラインインダクタンスを大きくするよう調節するだけで、リンギングノイズの周波数を低減できるので、高周波リンギングが抑制されたプリント基板および安価なスイッチング電源を構成できる。

(もっと読む)

集積回路用フロアプラン設計支援方法、設計支援プログラム及び設計支援装置

【課題】最適で品質の高いフロアプランを短時間で作成でき、データや制約の変更に対しても大幅な変更なしに対応できるLSI用フロアプラン設計支援方法を提供すること。

【解決手段】フロアプラン全体を監視する戦略エージェント/その支配下で機能ブロック毎に用意されブロックの位置を管理するブロックエージェントを作成し、戦略エージェントがブロックの配置に関する制約を選択すると、各ブロックエージェントが各制約について対応する機能ブロックの制約に対する適応度をブロックの位置の関数として表す適応度関数を生成して合成し、合成した適応度関数に基づいて最も適応度の高い位置に対応する機能ブロックを配置する。戦略エージェントは、配置後にフロアプランの必要条件を満たすかを判断し、満たす場合にはフロアプランの設計を終了し、満たさない場合には制約を選択し直す。

(もっと読む)

設計チェックシステム、設計チェック方法、及び設計チェックプログラム

【課題】 インターネットで接続された環境においても、回路設計技術や基板設計技術を公開することなく、基板レイアウトの電気特性チェックを行うことができる設計チェックシステムを提供する。

【解決手段】 本発明では、入力された基板レイアウト情報の基板レイアウトの影響による電気特性不良の発生が予測される位置から特徴量を抽出する。修正判定手段は、この特徴量とデータベースから読み出した電気特性不良に対応する修正判定基準とを比較することでレイアウト修正の要否を判定する。これにより、ユーザに、修正判定基準や判定方法を公開することなく、電気特性のチェックを行うことができる。

(もっと読む)

レイアウト方法

【課題】 ノイズの発生量の削減を考慮したレイアウトを行うことによって、LSIの内部から発生するノイズを低減し、ノイズによるLSIの誤動作を防止することを目的とする。

【解決手段】 ノイズ量算出工程100および配線情報抽出手段120において求めたノイズ量とノイズ低減の度合いを用いて、配置配線工程130においてノイズを考慮したインスタンスの配置を行う。このことにより、ノイズを考慮した自動レイアウトを可能とし、LSI内部から発生するノイズを低減することによりノイズによるLSIの誤動作を防ぐことができる。

(もっと読む)

伝送線路の電気的特性の最適値取得方法

【課題】 仮想的にグランドプレーンを追加することにより、電源/グランド層を持たない伝送線路の電気的特性の最適値を取得することができるようにする。

【解決手段】 電源/グランド層を持たない二層基板(両面基板)4の配線パターンa,bの電気的特性の最適値を取得するに際し、基板体2の少なくとも一方向に仮想的なグランドプレーンである仮想の電源/グランド層6を配設し、基板体2の配線パターンa,bの電気的特性の最適値をたとえば電磁界解析ソフトによって解析するようにする。

(もっと読む)

レイアウト検証装置及びレイアウト検証方法

【課題】 配線1の終端部3の形状がL型であるときでも、終端部3における配線1の外周とコンタクト2の間隔が“a”未満のときはエラーメッセージを出力する。しかし、終端部3においては、図7に示すように、間隔が“a”より短い“b”以上であれば設計上許容される場合があるので、不要なエラーメッセージを出力してしまうことがある課題があった。

【解決手段】 配線1の終端部3の形状を判定し、その形状に応じた設計基準値を出力する。

(もっと読む)

プリント基板からの電磁放射簡易計算方法、プリント基板からの電磁放射簡易計算装置及び、電磁放射簡易計算プログラムを記録した記録媒体

【課題】 精度が良く、電界をベクトルとして考えて打ち消しの場合も考慮した、基板設計CADの中で会話的に利用できる電界強度計算の装置を提供する。

【解決手段】 電界強度計算手段1は、プリント基板レイアウトCADのデータaを読んで、配線ごとにその配線をドライブするICのピン、レシーバとなっているICのピンを抽出し、IC・配線情報bから得られるそれぞれのICと配線の情報と、電界観測点までの距離などのパラメータが定義された計算パラメータcの情報を使って、微小ループアンテナが作る電界の式に基づき、その配線が作る電界強度を計算し、結果データdを生成する。結果表示手段2は、結果データdから、計算パラメータcに定義してある許容値をこえている配線を抽出し、その周波数とネット名の一覧eを出力しまた、電界ベクトルを周波数ごとにベクトル加算し、基板全体の電界を得、周波数−電界強度グラフfを出力する。

(もっと読む)

電子回路基板設計用CADシステム及びそれに使用するプログラムを記憶した記録媒体

【課題】 メッキ線と側面メタライズ層との接合など、配線部の導通状況の把握あるいはチェックを簡単な処理により正確に行うことができ、しかも検査目的や基板品種の違い等に応じてその設定内容を柔軟かつ簡単に変更できる機能を有した電子回路基板設計用CADシステムを提供する。

【解決手段】 接続判定対象領域を、通電接続領域T,L,B,Rを含む複数の要素領域に細分化し、接続判定の対象となる要素領域T,L,B,R毎に、これに接続する配線ネット図形a〜gの集合を生成する。そして、それら集合間に所定の演算式に従う集合演算を施し、その演算結果に基づいて配線ネット接続情報を生成する。これにより、メッキ線と側面メタライズ層との接合など、配線部の導通状況の把握あるいはチェックを簡単な処理により正確に行うことができる。また、判別の目的や基板品種に応じて判別条件が異なる場合等においても、演算式を用いることで所望の判別条件を的確に設定することができるようになり、ひいては各種ニーズに柔軟に対応できる。

(もっと読む)

レイアウト設計支援装置、コンピュータ読み取り可能な記録媒体

【課題】 レイアウトパターンに対する補正結果と、この補正の検証結果とをレイアウトパターン設計者自身が設計中に逐次確認できるレイアウト設計支援装置、コンピュータ読み取り可能な記録媒体を提供する。

【解決手段】 縮小投影露光に使われるレチクルパターンを作成する設計支援装置であって、レイアウトパターンを作成するためのレイアウトエディタ1と、レイアウトパターンに対して補正および検証を行うためのOPC補正・検証装置2と、レイアウトパターン、補正および検証のデータを格納するためのデータベース3などから構成され、レイアウトエディタ1は、設計者がユーザインタフェースを通して操作することが可能とされ、レイアウトパターンを作成するための機能の他に、OPC補正・検証装置2の補正および検証を行うための機能を支援するために、画面上のメニューに補正・検証コマンドが追加されている。

(もっと読む)

放射ノイズ防止プリント基板配置配線処理システム

【課題】配置配線処理時にパスコン追加のEMC設計条件を検出及びパスコンの追加を行い放射ノイズ発生を防止し設計品質を保証するプリント基板配置配線処理システムの提供。

【解決手段】電子部品の電源ピンを抽出する電子部品電源ピン抽出部21、電源ピンから電源のヴィアまでの配線パターンを抽出する配線パターン抽出部22、抽出された配線パターンの線長、線幅を検査する線長、線幅検査部23、パスコンの追加が可能かを検査するパスコン追加可能性検査部24、現状の配線経路でパスコンが追加不可能な場合パスコン追加可能とする配線経路があるか検査する配線経路変更可能性検査部25と、配線経路を変更する配線経路変更実行部26、パスコン追加実行部27、配線経路を変更してもパスコンが追加不可能な場合エラー表示するエラー表示部28を備える。

(もっと読む)

画像処理方法および装置

本発明は、三次元表示内の画像物体を処理するための方法を開示し、ここでは、画像物体が画像生成手段によって仮想画像空間内に表示され、三次元画像空間内の画素には選択装置によって到達することができ、また、コンピュータが座標値を画像物体に応じた位置の画像物体に割り当てる。画像物体の少なくとも一つの画素を選択装置によって処理するためマークされる。また本発明は、三次元表示を処理し、かつ修正する装置について開示する。該装置は、画像データを生成するためのコンピュータと、仮想画像空間内にて三次元形態の画像データを表示するためのディスプレイスクリーンと、三次元表示を手動で動かすためのポイントデバイスとを有する。ポイントデバイスは、画像空間内を自由に移動でき、その位置を伝達するための伝達手段を有し、三次元表示の画素をその位置に応じてポイントデバイスに当てるコンピュータと接続されている。 (もっと読む)

1,061 - 1,078 / 1,078

[ Back to top ]