Fターム[5B046JA01]の内容

Fターム[5B046JA01]の下位に属するFターム

Fターム[5B046JA01]に分類される特許

1 - 20 / 1,237

プリント基板組立体の配線設計方法及び製造方法

閾値テーブルの作成方法、クロストーク解析の悲観性削減方法、クロストーク解析方法、及びクロストーク解析プログラム

設計支援装置およびその情報処理方法

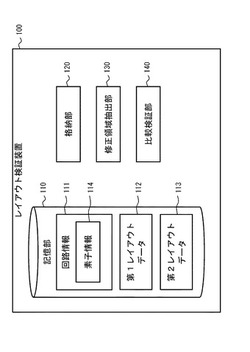

レイアウト検証装置、方法及びプログラム

【課題】LVS検証においてチップの一部にレイアウトの変更が発生した場合にレイアウト検証処理の負担を軽減すること。

【解決手段】レイアウト検証装置は、半導体集積回路のレイアウトを検証するものであり、論理回路の素子及び当該素子間の接続関係を定義した複数の素子情報を含む回路情報と、当該回路情報に基づき複数層のレイアウト領域が設計された第1のレイアウトデータと、を記憶する記憶部と、回路情報と第1のレイアウトデータとの比較検証においてエラーとなったことに起因して、当該第1のレイアウトデータのレイアウト領域が修正された第2のレイアウトデータを記憶部に格納する格納部と、記憶部を参照し、第1のレイアウトデータと第2のレイアウトデータとに基づいて、修正されたレイアウト領域である修正レイアウト領域を抽出する修正領域抽出部と、修正レイアウト領域と回路情報とを用いて再度の比較検証を行う比較検証部と、を備える。

(もっと読む)

HDL環境のためのグローバルクロックハンドラーオブジェクト

【課題】HDL環境において模擬クロック信号を発生しコントロールすること。

【解決手段】ハードウェア記述言語(HDL)環境に使用するためのグローバルなクロックハンドラーオブジェクトが開示される。HDLモジュールは、1つ以上のクロックステートメントを含む。コンピュータシステムがクロックステートメントを実行するとき、クロックハンドラーオブジェクトがコールされる。クロックハンドラーオブジェクトは、集積回路設計の1つ以上の模擬ファンクションブロックに対する模擬クロック信号を発生する。各模擬クロックは、個別の且つ独特のスレッドに指定される。クロックハンドラーオブジェクトは、集積回路設計に対する各模擬クロック信号を管理するように構成されたシングルトンオブジェクトである。各模擬クロック信号の発生及びコントロールは、ダイナミックアレイにおけるクロックハンドラーオブジェクトにより遂行される。ダイナミックアレイは、模擬クロック信号ごとにパラメータを指定するエレメントを含む。

(もっと読む)

遅延解析プログラム,遅延解析装置および遅延解析方法

【課題】故障要因を高い精度で推定する。

【解決手段】選択部12は、複数の要素のうち、複数の活性化パスが到達する要素について、複数の活性化パスのうちの一つを解析対象パスとして選択する。第1算出部13は、設計段階で得られた複数の活性化パスそれぞれの遅延分布に基づき、解析対象パスが複数の活性化パスの中で最も遅いという条件の下での、解析対象パスの遅延分布を算出する。第2算出部14は、第1算出部13によって算出された遅延分布に基づき、複数の活性化パスにおけるランダムばらつきが遅延に与える影響度合いを示す値を算出する。解析部15は、第2算出部14によって算出された影響度合いを示す値を、ランダムばらつきの影響に係る遅延要因の一つとして含む遅延解析を行なう。

(もっと読む)

受雷部保護範囲診断装置、及び、プログラム

【課題】受雷部による建築物の雷保護範囲を診断する。

【解決手段】受雷部保護範囲診断装置1は、診断対象とする建築物の受雷部による保護範囲を診断する。離散化処理部20は、建築物をモデル化した3次元モデルにおいて、建築物の屋根又は外壁に対応する3次元モデルの表面に含まれる第1の面を、複数の離散化領域に離散化する。雷保護範囲診断処理部40は、離散化領域が建築物における受雷部による保護範囲に含まれるか否かの判定結果に基づいて、離散化領域ごとに保護範囲の診断処理をする。

(もっと読む)

解析プログラム、解析方法、および解析装置

【課題】解析対象回路全体のリーク電流解析にかかる計算量を減らした関数を提供すること。

【解決手段】変動関数L1は、解析対象回路100内に含まれるセルごとの、定数aおよび第1の重み係数bとセルに固有のリーク電流のばらつきを表す第1の確率変数αとによって表現される正規分布から得られる平均値と、解析対象回路100内のセル群で共通のリーク電流のばらつきを表す第2の確率変数βと第2の重み係数cとの乗算結果と、により表現されている。変動関数L1では、第1の確率変数αがないため、第1の確率変数αの値を所定回数乱数で発生させる分の計算量が削減される。解析装置は、変動関数L1に、セルごとに取得した定数aの値、第1の重み係数bの値、および第2の重み係数cの値を与えることで、第2の確率変数βの値により変動する解析対象回路100のリーク電流量の変動関数を生成する。

(もっと読む)

回転機械

【課題】コンピュータ支援エンジニアリングに基づいて回転機械アセンブリを設計する方法を提供する。

【解決手段】回転機械アセンブリのレイアウトをコンピュータシステムのグラフィカルユーザインタフェース内に作成すること、および、レイアウトから回転機械アセンブリの機能モデル210を形成することを伴う。レイアウトは、回転機械アセンブリのための構成要素204,206を位置決めした後にそれらの構成要素間に関連性をもたらすことにより作成される。機能モデルは、関連性、選択された構成要素の相対位置、選択された構成要素の特性、および、関連性の特性のうちの1つ以上に基づいている。

(もっと読む)

半導体装置の設計方法及び半導体装置の製造方法

【課題】半導体装置の歩留まりが低下することを抑制する。

【解決手段】配線パターンを示す配線パターンデータを取得する(ステップS10)。次いで、配線パターンデータを解析して、第1方向パターン及び第2方向パターンを特定する(ステップS20)。第1方向パターンは、第1の方向に延伸するパターンであり、第2方向パターンは、第1の方向に直交する方向に延伸するパターンである。次いで、第1方向パターと第2方向パターンの交点を検出する。そして、この交点から延伸するパターンのうち、ビア、コンタクト及び他のパターンのいずれにも接続していないパターンを不要パターンとして検出し、検出した不要パターンを除去する(ステップS30)。そしてその後、設計した配線パターンに対して光近接効果補正を行う(ステップS40)。

(もっと読む)

配線の接続確認システム

【課題】大規模なシステムであっても、システムの設計者以外が単線単位で接続ルートを容易に特定できる配線の接続確認方法を提供する。

【解決手段】末端装置と、中継装置を介してケーブルにより接続され、かつ、ケーブルはコネクタを介して末端装置と、中継装置に接続されている配線構造における配線に対して、接続テーブルデータベースから読み出したコネクタとケーブルとの、及び、コネクタと、末端装置、及び、中継装置のいずれかとの、接続情報に基づき、指定された確認対象要素から接続情報を順次辿ることにより、その接続端までの接続ルートを特定する。

(もっと読む)

情報生成プログラム、情報生成方法、および情報生成装置

【課題】モデルの分解方向検出の高精度化を図ること。

【解決手段】+X〜−Zの6方向の各方向について、各方向からのEリング101の投影画像(a)〜(f)を生成する。投影画像(a)〜(f)は、所定サイズのビットマップに対し、所定倍率で投影される。他の部品を表示させてその色を背景色と同色の黒にして、各方向からのEリング101の投影画像(A)〜(F)を生成する。投影画像(A)〜(F)も、投影画像(a)〜(f)と同一サイズのビットマップに対し、同一倍率で投影される。両投影画像(a)〜(f),(A)〜(F)について、同一方向からの投影画像どうしで比較する。そして、一致する白のビット数が最大である組を検出し、その投影画像の組を投影した方向を、組付方向に決定する。図1の場合は、+X方向が組付方向となり、その逆の−X方向が分解方向となる。

(もっと読む)

3次元コンピュータ設計支援プログラム、コンピュータ読取可能な記録媒体、3次元コンピュータ設計支援システム及び3次元コンピュータ設計支援方法

【課題】3次元CAD上にてフレキシブルフラットケーブルを適切に設計可能にする。

【解決手段】3次元コンピュータ設計支援プログラムCPRは、コンピュータによって、3次元仮想空間上にて配線設計されたフレキシブルフラットケーブルの終点側の導体部が取り得る向き範囲を演算する。また、この導体部が接続される終点側コネクタの向きを取得する。そして、終点側コネクタの向きが設計されたフレキシブルフラットケーブルの終点側の導体部が取り得る向き範囲内にある場合は接続可能と判定する。一方、終点側コネクタの向きがフレキシブルフラットケーブルの終点側の導体部が取り得る向き範囲内にない場合は接続不能と判定する。

(もっと読む)

設計支援装置、設計支援プログラム、および設計支援方法

【課題】高密度な部品の実装設計を行うことができる設計支援装置、設計支援プログラム、および設計支援方法を提供する。

【解決手段】判別部15bは、記憶部13に記憶された実装情報に基づき、設計対象の基板上に配置された第1の部品と第2の部品を実装する製造工程の前後関係を判別する。取得部15cは、第1の部品および第2の部品のうち判別部15bにより製造工程が後と判別された部品については部品を基板に実装する際に確保すべき領域を示す第1の領域情報、製造工程が前と判別された部品については部品を基板に実装した際に占有する領域を示す第2の領域情報を記憶部13から取得する。判定部15dは、取得部15cにより取得された第1の領域情報と第2の領域情報を比較して干渉の有無を判定する。

(もっと読む)

航空機設計装置、航空機設計プログラム、及び航空機設計方法

【課題】より最適な航空機の設計を可能とすると共に、航空機の設計に要する労力及び時間を低減させる、ことを目的とする。

【解決手段】航空機設計装置は、航空機の設計に要する複数の設計変数に基づいて、航空機の諸元である機体諸元を算出し、算出した機体諸元が機体の成立性を示した予め定められた制約条件及び航空機を最適化させるものとして予め定められた最適化条件を満たすか否かを判定し、算出した機体諸元が制約条件を満たすと共に最適化条件を満たすように、設計変数を変更し、変更した設計変数に基づいた機体諸元の算出を繰り返す繰返処理を実行する。

(もっと読む)

排水負荷計算支援システム

【課題】排水設計の知識や経験を備えていない顧客が信頼性の高い安定した設計を行うとともに、取扱業者が顧客及び物件についての情報を早期に且つ確実に取得することができる排水負荷計算支援システムを提供する。

【解決手段】中央装置2が、予め設定してある排水負荷計算の適用条件による制限を加えつつ、既存の給排水設備基準に基づいて排水管の排水負荷計算を実行するとともに、その計算結果に計算要求した顧客10の情報と計算対象の物件の情報とを加えて生成した可視情報Vを所定の業者情報処理装置3に送信する。

(もっと読む)

プログラム検証装置およびプログラム検証方法

【課題】搬送装置の制御プログラムの検証を効率的に行う。

【解決手段】搬送装置の制御プログラムを実行して仮想搬送装置による搬送をシミュレーションする際に、制御プログラムの実行位置の履歴と、仮想搬送装置における搬送状態の履歴を、シミュレーション時刻と関連付けて記録する。そして、該搬送状態の履歴から搬送のエラー状態(W21,W23)を検出し、さらに、該エラー状態のシミュレーション時刻に対応する制御プログラムの実行位置(W22)を検出する。これにより、エラー発生時における搬送状態および制御プログラムの実行位置を容易に特定できる。

(もっと読む)

回路設計装置、デカップリング容量効果最適化方法、及びプログラム

【課題】 本発明の課題は、デカップリング容量効果を最適化した回路設計を行うことを目的とする。

【解決手段】 上記課題は、回路を構成する複数のセル間のネット毎の高電位電源側及び低電位電源側の配線容量と、各入力ピンの該高電位電源側及び該低電位電源側の容量とを記憶する記憶部と、前記記憶部に記憶された前記各ネットの配線容量と、前記各入力ピンの容量とを参照して、前記構成における非動作パスに対して、セルの置換前の該セルの組み合せと、セルを置換する際の制約に従った置換後のセルの組み合せのうち、該非動作パスの信号値の遷移状態に応じた、各ネット及び各入力ピンの前記高電位電源側又は前記低電位電源側の容量を加算した総容量に基づいて、該総容量が最大となるセルに置換することによって、デカップリング容量効果を最適化する最適化処理部と、を有する回路設計装置により達成される。

(もっと読む)

半導体回路性能見積装置、その方法及びそのプログラム

【課題】所定のアルゴリズムを実現する半導体回路の性能を簡易に見積もることのできる半導体回路性能見積装置を提供する。

【解決手段】半導体回路の性能を見積もるための半導体回路性能見積装置であって、前記半導体の設計データであるソースコードを基に、アクセス先のメモリ種類別のアクセス回数を求め、該アクセス先のメモリ種類別のアクセス回数とアクセス先のメモリ種類別のアクセスコストを基に、見積性能を算出する。

(もっと読む)

オブジェクト管理システム

【課題】車両構造物の構成を管理するための方法及び装置を提供する。

【解決手段】車両構造物のライフサイクルの種々のフェーズで、車両構造物のコンポーネントの識別情報を含む構成を示す各データセットを比較し、データセット内のコンポーネントの識別情報間の相違点を特定し、特定のオブジェクトに対して種々の部品表が一致していることを確認する。さらに、データセット内のコンポーネントの識別情報間の相違点がエラーであるかどうかを確定し、確定されたエラーのエラー記述及びデータセット間のコンポーネントの正しいが異なる識別情報の相違点記述を記録し、データセット内のコンポーネントの識別情報間で特定された相違点を視覚的に表示する。

(もっと読む)

1 - 20 / 1,237

[ Back to top ]