Fターム[5B060MB00]の内容

メモリシステム (7,345) | メモリバス技術 (414)

Fターム[5B060MB00]の下位に属するFターム

複数のバスの切替、接続制御 (155)

複数系システム(バス)間の接続制御 (30)

バス使用モード制御 (34)

データ幅とバス幅が異なるもの (43)

バスのライン数の削減技術 (52)

共通バスの他にメモリ専用バスを有するもの (16)

Fターム[5B060MB00]に分類される特許

61 - 80 / 84

メモリ制御回路

【課題】 複数のメモリを制御する場合に、データ転送効率の低下を抑制するメモリ制御回路を提供する。

【解決手段】 メモリ51、52、・・・・・、5nの動作を制御するコマンド信号CDを、メモリ51、52、・・・・・、5nに共通に出力するコマンド発行部11と、メモリ51、52、・・・・・、5nのアドレスを指定するアドレス信号ADを、メモリ51、52、・・・・・、5nに共通に出力するアドレス部12と、コマンド信号CDによるメモリ51、52、・・・・・、5nの制御をそれぞれ有効にする複数のメモリ選択信号S1、S2、・・・・・、Snを、メモリ51、52、・・・・・、5nに出力するメモリ選択部13と、メモリ51、52、・・・・・、5nとの間でそれぞれデータD1、D2、・・・・・、Dnの転送をするデータ転送部14とを備える。

(もっと読む)

異なるチップにおける異なる処理を制御するコマンド

いくつかの実施例は、本発明は、処理タイプ信号を有するレジスタを有するチップを有する。当該チップはまた、第1コマンドを受け付け、第1コマンドに応答して、処理タイプ信号が第1の値を有する場合、チップに第1処理を実行させ、処理タイプ信号が第2の値を有する場合、チップに第2処理を実行させる制御回路を有する。当該チップは、メモリシステムにおけるメモリチップであってもよい、他の実施例が記載及び請求される。

(もっと読む)

(もっと読む)

マルチチップシステム及びそれのデータ伝送方法

【課題】マルチチップシステム及びそれのデータ伝送方法を提供する。

【解決手段】本発明はメモリチップ間にデータを直接伝送することができるマルチチップシステム及びそれのデータ伝送方法に関するものである。本発明によるマルチチップシステムは第1及び第2メモリチップ、及び第1及び第2メモリチップの動作を制御するホストシステムを含む。第1メモリチップはホストシステムから入力されたローカル伝送情報に応答して第2メモリチップにデータが直接伝送されるように第2メモリチップを制御する。そして第1メモリチップはローカル伝送動作が実行される間にホストシステムが第1及び第2メモリチップをアクセスすることができないようにホストシステムを制御する。本発明によれば、ホストシステムの介入なしにメモリチップ間にデータを直接伝送することができるため、マルチチップシステムの効率が向上し、データ伝送速度が著しく速くなる。

(もっと読む)

記憶装置、データ処理システムおよび記憶制御方法

【課題】書き込み時の応答性に優れた記憶装置を提供する。

【解決手段】レジスタとメモリ領域とを各々が有する複数のメモリと、データを入力するインタフェースと、レジスタ転送処理とメモリ書き込み処理とを行う制御回路を有し、制御回路は、複数のメモリの各々に対して連続した異なる時間帯にレジスタ転送処理RPを行うように制御する。また、レジスタ転送処理終了後に続けてメモリセルアレイへの書き込み処理PPを開始し、書き込み最大時間経過後にレジスタ転送処理を再び行うように制御する。

(もっと読む)

メモリ制御装置

【課題】 本発明は、消費電力や不要輻射を減少できるメモリ制御装置を提供することを目的とする。

【解決手段】 メモリ制御部3に、メモリ7への書き込みデータとメモリからの読み出しデータが一致するかどうかの検査を実施してその良否を判定する検査実施/判定部2を設け、この検査実施/判定部2の比較結果によって、メモリインターフェース部7の出力電流とメモリインターフェース部の出力電圧、さらにメモリ制御部3のメモリ制御タイミングのパターンを調整する構成とする。この構成によれば、メモリデータエラーを回避しながらメモリ7の駆動電流と駆動電圧を最適化でき、消費電力や不要輻射を減少させることができる。

(もっと読む)

データ記憶装置

【課題】 バスに流れる電流量を減少させることができるデータ記憶装置を提供する。

【解決手段】 DRAMバス6が動作状態から非動作状態に切り替わったと判定した場合、VT電源14を介してDRAMバス6に流れる電流量を減少させるよう、SSTL2インターフェースバッファ121の出力状態を所定の出力状態に切り替える。

(もっと読む)

メモリバスターミネーション

メモリバスラインをターミネーション処理するための方法、装置及びマシーン読み出し可能な媒体が説明される。いくつかの実施例では、メモリバスラインは、メモリへの書き込み中にメモリバスラインの駆動に利用される出力バッファの1以上のトランジスタによりターミネーション処理される。  (もっと読む)

(もっと読む)

複数のメモリコントローラを持つメモリシステム及びその同期化方法。

本発明は、メモリシステムが、クロック制御されるバス(B)に並列に設けられる複数のメモリコントローラ(SCx)、及びメモリコントローラ(SCx)に付属するメモリチップ(Fx)により形成され、かつバス(B)を介して、論理メモリセクタ番号を使用して、メモリ操作指令を持つホストシステム(HS)と通信するものにおいて、ホストシステム(HS)により記憶操作が要求されると、論理メモリセクタ番号の範囲について関係せしめられるメモリコントローラ(SCx)が、アービトレーションによりホストシステム(HS)と通信するためのバスを受け継ぐことを特徴とする、メモリシステムに関する。  (もっと読む)

(もっと読む)

記憶デバイス制御装置

【課題】 メモリコントローラとメモリモジュールとの間をシリアルインターフェースとした場合でも十分な信頼性を確保できる記憶デバイス制御装置を提案する。

【解決手段】 本発明の記憶デバイス制御装置は情報処理装置からのファイル単位でのデータ入出力要求に応答して記憶デバイスに対するI/O要求を出力するチャネル制御部を備える。チャネル制御部はファイル単位でのデータ入出力要求を受信するCPUと、CPUの指令に応答してファイル単位でのデータ入出力要求に対応するI/O要求を出力するI/Oプロセッサと、CPUのファイルアクセス処理に要する情報を記憶するメモリシステムを備える。メモリシステムは複数のメモリモジュールと、メモリコントローラとを備えており、メモリモジュールとメモリコントローラとは二重化されたシリアルインターフェースで接続されている。

(もっと読む)

ディジーチェーン型メモリトポロジのメモリコマンド遅延バランシング

【解決手段】ディジーチェーン型メモリトポロジに関する手法であって、該手法では、メモリモジュール(DIMM)からの応答の受信タイミングの予測に加えて、メモリコントローラは、それが送ったコマンドが、宛先のDIMMで何時実行されるかを効果的に予期できる。DIMMのコマンド遅延ユニットにおけるDIMM固有コマンド遅延をプログラミングすることで、本開示に基づくコマンド遅延バランシング手法は、メモリチャンネルにおける全てのDIMMに渡ってコマンド信号の実行を「規格化」又は「同期化」する。コマンドの実行タイミングを予測するこのような能力によって、メモリコントローラは、ディジーチェーン型チャンネル上の全てのDRAMデバイス(即ちメモリモジュール)の電力プロファイルを効率的に制御できる。また、DIMMにおける個別のDIMM固有応答遅延ユニットが、応答経路でDIMM固有応答補償を与えるようにプログラムされて、さらに、メモリコントローラが、それによって先に送られたコマンドへの応答を受信するタイミングを正確に確かめることを可能とし、故に、応答のさらなる処理がより良く管理可能となる。 (もっと読む)

リングバス構造とフラッシュメモリシステムにおけるその使用法

システムおよびこのシステムで使用される集積回路チップは、ノード間でデータおよびコマンドを転送するために各コンポーネントのノードを相互接続するためにリング状のバスを利用する。説明されているシステムの例は、1つまたはそれより多い再プログラム可能な不揮発性メモリセルアレイを有するメモリであり、この不揮発性メモリセルアレイがリングバスによって互いに接続され、且つシステムコントローラに接続されている。  (もっと読む)

(もっと読む)

メモリターミネーション用直流安定化電源装置

【課題】 一つのメモリターミネーション用直流安定化電源装置で複数のメモリをターミネーションする際に、出力電圧の精度劣化を低減することができるメモリターミネーション用直流安定化電源装置を提供する。

【解決手段】 複数のセンス電圧端子(VSENSE1端子、VSENSE2端子)と、前記センス電圧端子に入力されるセンス電圧を平均化して出力するセンス電圧平均化回路1bとを備え、センス電圧平均化回路1bの出力に応じて出力電圧(VTT端子から出力される電圧)の安定化を行うメモリターミネーション用直流安定化電源装置。

(もっと読む)

半導体装置及びバスシステム

【課題】T−LVTTL伝送方式のバスに、近似の論理パターンを有する信号が連続して出力される結果、終端抵抗1電流が大になり終端電圧VT が変動することを防ぐ。

【解決手段】アドレスが所与のアドレスと一致したとき、アドレス比較器7は一致信号73を送出する。反転回路6は、一致信号73を受けたとき、バス1Dと内部回路101との間を伝送する信号を反転する。アドレスが連続する一連のデータが、所定アドレス指定時のみ反転して入出力されるから、近似の論理パターンがそこで反転して途切れ、近似の論理が連続して出力されない。また、終端電圧VT が所定範囲を超えたとき、無効なバスに論理「1」又は「0」のダミー信号を出力して、終端電圧を修正する。

(もっと読む)

高速メモリモジュール

メモリバスに接続された複数のブランチを有するメモリモジュールを製造するための装置および方法である。各ブランチは、少なくとも1つの伝送信号(TS)経路および/または少なくとも1つの下位伝送信号(STS)経路を介してメモリバスに接続された、少なくとも1つのダイナミックランダムアクセスメモリ(DRAM)デバイスまたは同期ランダムアクセスメモリ(SDRAM)デバイスを含む。メモリモジュールは、TS経路またはSTS経路に接続され、抵抗を含み、DRAMデバイスまたはSDRAMデバイスと直列に接続され、かつ、メモリバスに接続された抵抗を含む、少なくとも1つのブランチを有する。また、メモリモジュールを実装したコンピュータシステムが説明される。  (もっと読む)

(もっと読む)

トレース上のコンデンサを利用した高速メモリモジュール

【課題】 トレース上のコンデンサを用いた高速メモリモジュールを提供する。

【解決手段】 メモリバスに接続された複数のDRAM(Dynamic Random Access Memory)デバイスもしくは複数のSDRAM(Synchronous RAM)デバイスを備えるメモリモジュールを製造する装置および方法を提供する。ここで、各DRAMデバイスもしくは各SDRAMデバイスは送信信号(TS)線を介してメモリバスに接続されている。該メモリバスは少なくとも1つの、コンデンサが接続されたTS線を有する。該コンデンサは、該複数のDRAMデバイスもしくは該複数のSDRAMデバイスと並列になるように該TS線と接続され、該TS線は、メモリバスの信号入力端と第1DRAM/SDRAMデバイスのTS線の接着ポイントの間で、メモリバスに接続されている。また、このようなメモリモジュールを備えるコンピュータシステムも開示する。

(もっと読む)

DMA転送を用いたコンピュータシステム

【課題】メモリを占有することなくデータ転送に要する時間を短縮し、さらにLSIなどへの適用時におけるレイアウト上の面積を最小限にする、DMA転送を用いたコンピュータシステムを提供。

【解決手段】コンピュータシステム10は、バス16を介して接続される中央処理装置12および主記憶装置14を有し、送受信データを記憶する主記憶装置14に対して、外部装置20と送受信データ転送を行うI/Oモジュール18を直接的に接続することにより、主記憶装置14のメモリマクロ22にアクセス可能な最小単位のサイクルでデータ転送を行うことができ、バスを介したDMA転送より高速なデータ転送を実現することができる。

(もっと読む)

情報処理装置、外部装置、ホスト装置、及び通信方法

【課題】回路規模を増大させることなく一対多の通信を行う。

【解決手段】 ホストデバイス10には、メモリカード20を装着する複数の装着部11が設けられている。装着部11に挿入されたメモリカード20は、一組の信号線CLK(クロック),BS(バスステート),DIO(データ入出力)を共有している。ホストデバイス10は、どのメモリカード20と通信しているために夫々のメモリカード20に識別子を割り当てる。識別子の割り当ては、メモリカード20の挿抜を検出する信号線XINSで行われる。

(もっと読む)

シリアルデータ転送システム、シリアルデータ転送装置、シリアルデータ転送方法及び画像形成装置

【課題】 同一アドレス割当ての複数のシリアルメモリ装置を使用可能にする。

【解決手段】 各々クロック端子SCLとデータ端子SDAとを有するシリアルインターフェースを備える同一アドレス割当て構成のn個のシリアルメモリ装置2,3,4と、1個のクロック端子SCLとn個のデータ端子SDA0〜SDA2とを有し、n個のデータ端子SDA0〜SDA2にn個のシリアルメモリ装置2,3,4の各々のデータ端子SDAが接続され、1個のクロック端子SCLにn個のシリアルメモリ装置2,3,4のクロック端子SCLが共通に接続されたシリアルデータ転送装置1と、を具備し、クロック端子が接続されるシリアルクロックラインを共通化し、データ端子が接続されるデータラインをシリアルメモリ装置毎に個別に分けることで、汎用で省スペース向きの同一アドレス割当て構成の複数のシリアルメモリ装置2,3,4を接続可能とした。

(もっと読む)

ピン上のコンデンサを使用する高速メモリモジュール

メモリバスに接続された複数の分岐を持つメモリモジュールを製造する装置および方法であって、各分岐は、前記メモリバスに少なくとも一つの送信信号(TS)ラインおよび/または少なくとも一つの副送信信号(STS)ラインを介して接続された少なくとも一つの動的ランダム・アクセス・メモリ(DRAM)デバイスあるいはSDRAMデバイスを含む。前記メモリモジュールは、前記TSラインあるいはSTSライン及び前記DRAMデバイスあるいはSDRAMデバイスに並列接続されたコンデンサを含む少なくとも一つの分岐を含む。前記メモリモジュールを実装するコンピュータ・システムもまた開示されている。 (もっと読む)

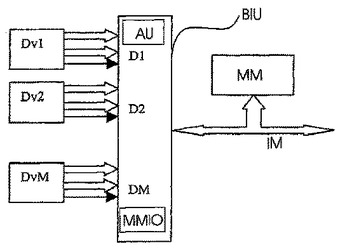

データ処理システム及びインターコネクト・アービトレーション方法

データを処理する複数の処理ユニット(Dv1〜DvM)と、複数の処理ユニット(Dv1〜DvM)からのデータを保存する少なくとも一つのメモリ手段(MM)と、複数の処理ユニット(Dv1〜DvM)と少なくとも一つのメモリ手段(MM)とを接続するインターコネクト手段(IM)とを備えたデータ処理システムが提供される。処理ユニット(Dv1〜DvM)は、少なくとも一つのメモリ手段(MM)にデータを書き込むためにインターコネクト手段(IM)を介して少なくとも一つのメモリ手段(MM)に書き込みアクセスを要求することに適応している。複数の処理ユニット(Dv1〜DvM)から少なくとも一つのメモリ手段(MM)へのアクセスのためにインターコネクト・アービトレーションを行う少なくとも一つのアービター手段(AU)が提供され、複数の処理ユニット(Dv1〜DvM)から少なくとも一つのメモリ手段(MM)への書き込みアクセスによりもたらされるインターコネクト手段の最低論理レベル変化に基づいてインターコネクト・アービトレーションが行われる。従って、異なる処理ユニットからの二つ以上の書き込み要求が受け付けられる場合、その処理ユニットに対して、インターコネクト・アービトレーション、即ち、インターコネクトへのアクセスが許可され、インターコネクトを介してメモリ手段へ送出されるデータがインターコネクト手段に対して最低論理レベル変化となる。それにより、論理レベルのスイッチングに起因する電力消費が低減される。  (もっと読む)

(もっと読む)

61 - 80 / 84

[ Back to top ]