Fターム[5B060MB00]の内容

メモリシステム (7,345) | メモリバス技術 (414)

Fターム[5B060MB00]の下位に属するFターム

複数のバスの切替、接続制御 (155)

複数系システム(バス)間の接続制御 (30)

バス使用モード制御 (34)

データ幅とバス幅が異なるもの (43)

バスのライン数の削減技術 (52)

共通バスの他にメモリ専用バスを有するもの (16)

Fターム[5B060MB00]に分類される特許

21 - 40 / 84

マルチプロセッサ装置

【課題】バスを共有しつつもメモリに対するアクセス性能を向上させることが可能なマルチプロセッサ装置を提供すること。

【解決手段】CPU0(1−0)およびCPU1(1−1)と、フラッシュメモリ0〜3(2−0〜2−3)とが、共通バスによって接続される。CPU0(1−0)およびCPU1(1−1)には、位相シフトされたクロック信号が供給される。たとえば、フラッシュメモリ0(2−0)は、CPU0(1−0)からの読み出し要求に応答して、CPU0(1−0)に供給される位相シフトされたクロック信号に同期してメモリマットから読み出したデータを共通バスに出力する。したがって、バスを共有しつつもメモリに対するアクセス性能を向上させることが可能となる。

(もっと読む)

多様に配置されたメモリ・コンポーネントからメモリ・オペレーションを調整する方法と装置

【課題】 さまざまな位置に配置されたメモリ・コンポーネントの間でメモリ動作を調整する方法および装置を提供すること。

【解決手段】 本発明の実施形態によれば、複数のメモリ・コンポーネントに結合されたアドレス・バスについて、ウェーブパイプライン化が実施される。複数のメモリ・コンポーネントが、アドレス・バス伝搬遅延およびデータ・バス伝搬遅延に関係する調整に従って構成される。アドレス信号および/または制御信号に関連する、これらの信号の伝搬遅延を複製するタイミング信号が、メモリ動作の調整に使用される。

(もっと読む)

相互接続システム

【課題】コンピュータ又は遠隔通信システムの構成要素と共に使用する相互接続システムを提供する。

【解決手段】データメモリシステム、コンピュータシステム、又はデータ経路がシステムの電力消費及びデータスキュー特性を制御するように配置されて作動される通信システムとすることができる、ネットワークにおいて要素を配置するための相互接続システム、装置、及び方法。構成可能なスイッチング要素を使用して、ノードでの相互接続を形成することができ、制御信号及び他の情報を使用して、構成可能なスイッチング要素の他の態様の電力ステータスが管理される。ネットワークのノード間で送信されているデータの時間遅延スキューは、ネットワークの1つ又はそれよりも多くのノードでデータの論理的及び物理的ライン割当てを交換することによって変更することができる。また、トレース経路指定の複雑さを低減する相互接続マザーボードを配置する方法も開示する。

(もっと読む)

電子機器

【課題】波形品質の確保と消費電力の低減とを両立する電子機器を提供することを目的とする。

【解決手段】データ信号線11に終端抵抗7が接続された回路構成を有する電子機器1であって、データ処理手段2と、データ処理手段2の主記憶装置となる1つ以上のデータ記憶手段3と、データ処理手段2とデータ記憶手段3とを接続するデータ信号線11に終端抵抗7を介して終端電圧を印加する終端電圧生成手段6と、データ信号線11と終端抵抗7との間に接続される通電遮断手段8と、を有し、データ処理手段2はデータ記憶手段3の構成を検知し、その検知結果に基づいて、通電遮断手段8によりデータ信号線11と終端抵抗7との間を通電させて終端抵抗7を有効にし、又はデータ信号線11と終端抵抗7との間を遮断して終端抵抗7を無効にすることにより上記課題を解決する。

(もっと読む)

光相互接続

本発明の様々な実施形態は光相互接続を対象とする。本発明の一実施形態において、光相互接続は、光信号を出力するように構成されたレーザ、及びレーザに電子的に結合されたレーザダイオードドライバを含む。レーザダイオードドライバは、レーザダイオードドライバにより受信された電気信号に応じてレーザに光信号を出力させる。光相互接続は、回折光学素子および複数の光検出器を含む。光相互接続は、光信号を受け取るように配置されて、その光信号を複数の光信号に分割するように構成され、各光検出器が、別個の信号線に出力される電気信号へ複数の光信号の1つを変換する。 (もっと読む)

メモリ装置、メモリシステム、及びメモリ装置の設計方法

【課題】データ転送速度が向上しても、複雑な設計手法を用いることなく、信号反射による信号品質劣化を防止することができるメモリ装置、メモリシステム、及びメモリ装置の設計方法を提供する。

【解決手段】メモリシステムは、メモリコントローラ10、所定の特性インピーダンスを有する伝送線路L1〜L3を含んでなる伝送線路、及び伝送線路に接続されるメモリモジュール21,22,31,32を備えるメモリ装置11,12を備える。メモリ装置11は、メモリモジュール21,22に関して対称的に伝送線路上に配置され、メモリモジュール21,22とともにローパスフィルタをなすチップインダクタ23〜25を備える。同様に、メモリ装置12は、メモリモジュール31,32に関して対称的に伝送線路上に配置され、メモリモジュール31,32とともにローパスフィルタをなすチップインダクタ33〜35を備える。

(もっと読む)

チェーン化デバイスシステムにおいてパラメータを設定し待ち時間を決定する方法

【課題】チェーン化デバイスシステムにおいてパラメータを設定し待ち時間を決定する新規な記憶システム及び方法。

【解決手段】記憶ノードが情報(112、114)を記憶し、記憶ノード(120、130、140)がデイジーチェーン化ネットワークとして組織化される。記憶ノードの少なくとも1つがアップストリーム通信バッファ(132、134)を含む。記憶ノードへの情報の流れは、記憶ノード内部の通信バッファの制約条件に基づく。一実施形態では、マスタコントローラ(110)と複数の記憶ノード(120、130、140)との間の通信が、決められた最大待ち時間を有する。

(もっと読む)

記憶システム及び方法

【課題】能率的で好適な記憶システム及び方法を提供すること。

【解決手段】一実施形態では、記憶システム100は、複数の記憶ノード120、130、140、及びマスタコントローラ110を含む。記憶ノードは情報を記憶する。記憶ノード120、130、140は、アップストリーム通信の際の衝突の解決を容易にするように局所的に記憶ノード120、130、140で制御されるアップストリーム通信バッファ160を含む。マスタコントローラ110は、アップストリーム通信バッファの制約条件に基づいて、ノード120、130、140へのトラフィックの流れを制御する。一実施形態では、マスタコントローラ110とノード120、130、140の間の通信が、決められた最大待ち時間を有する。記憶ノード120、130、140は、チェーンメモリ構成によりマスタコントローラ110に結合することができる。

(もっと読む)

アドレス線配線構造及びこれを有するプリント配線基板

【課題】 メモリを搭載したプリント配線基板において、アドレス信号の波形歪や立ち上がり波形の鈍りが少ない実装方式を提供する。

【解決手段】 本発明は、少なくとも3つのメモリ素子とこれら3つのメモリ素子とデータを授受するバッファ素子との間を、前記メモリ素子のアドレス信号を伝送するアドレス信号線で結び、該アドレス信号線は、主線101Rから各メモリ素子に支線が分岐するスタブ構造を有するアドレス線配線構造に適用される。前記バッファ素子のアドレス端子の出力インピーダンスは、前記アドレス信号線の線路の特性インピーダンスよりも低い。また、前記バッファ素子から該バッファ素子に最も近い距離で支線が分岐する分岐点S1までの距離TL0は、前記分岐点S1から2番目に支線が分岐する分岐点S2までの距離TL1と等しいか、あるいは長い。更に、前記分岐点S2から3番目に支線が分岐する分岐点S3までの距離TL3は、前記距離TL0及びTL1よりも長い。

(もっと読む)

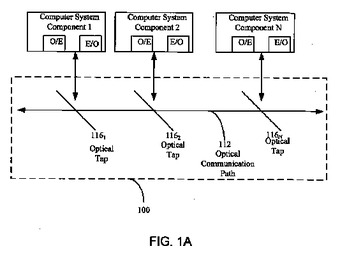

コンピュータシステム構成要素間の伝達をもたらす光相互接続システム

コンピュータシステム構成要素(106)間の伝達のための光相互接続システム(100)が記載されている。該システムは、光学データ伝達経路(112)と、複数の光学タップ(116)とを備える。各光学タップ(116)は、それぞれのコンピュータシステム構成要素(106)を、該光学データ伝達経路(112)に光学的に結合させる。各光学タップ(116)は、該データ伝達経路(112)からか又は光源(210)から受け取った光学信号から、電力を分割して、その関連付けられたコンピュータ構成要素からのデータ信号を生成して、結果として別の光学信号を生成する。各光学タップ(116)が、反射率と透過率との間のそれぞれの電力比率関係に従って、光を分割する。該光学タップ(116)の該比率関係は、共に合わせて、コンピュータシステム構成要素(106)間において前記光相互接続システム(112)を横切る信号に、所定の通信信頼度の測定基準を提供する。  (もっと読む)

(もっと読む)

メモリ制御装置

【課題】ボード上の遅延の大小に関わらず、メモリが出力するストローブ信号を正しく受信クロックとして受け取れるメモリコントローラを提供する。

【解決手段】本発明のメモリ制御装置は、終端抵抗のオン/オフが可能である双方向バッファを有し、上記終端抵抗のプルアップ側とプルダウン側の抵抗値を異なる値に制御することが可能であり、上記双方向バッファがストローブ信号の送受信に用いられることを特徴とする。

(もっと読む)

インタフェース回路および電子機器

【課題】正規の信号とノイズとを的確に識別して信頼性の高いデータ転送を実現する。

【解決手段】本発明のインタフェース回路は、第1の装置(例えば、CPU11)により生成されるクロックに同期して、第1の装置と、第2の装置(例えば、MEM20)との間で信号の送受信を行うインタフェース回路22であって、クロックの位相を所定時間分遅延させる位相制御部(例えば、遅延素子221)と、位相制御部が出力するクロックに基づき、第2の装置により生成出力される信号が正規の同期信号であるか否かを判定したタイミング信号を生成する信号生成部(例えば、セットリセット端子付きDタイプフリップフロップ222)と、により構成される。

(もっと読む)

多様に配置されたメモリ・コンポーネントからメモリ・オペレーションを調整する方法と装置

【課題】 さまざまな位置に配置されたメモリ・コンポーネントの間でメモリ動作を調整する方法および装置を提供すること。

【解決手段】 本発明の実施形態によれば、複数のメモリ・コンポーネントに結合されたアドレス・バスについて、ウェーブパイプライン化が実施される。複数のメモリ・コンポーネントが、アドレス・バス伝搬遅延およびデータ・バス伝搬遅延に関係する調整に従って構成される。アドレス信号および/または制御信号に関連する、これらの信号の伝搬遅延を複製するタイミング信号が、メモリ動作の調整に使用される。

(もっと読む)

メモリ制御回路

【課題】 信号品質の観点だけでODTを切替えると不要なODTの切替えが増えてしまい、結果的にメモリデバイスの消費電力を増やしてしまう。

【解決手段】 On-Die Termination機構を有する複数のメモリデバイスを接続可能なメモリ制御回路であって、複数のメモリデバイスの内、アクセス対象のメモリデバイスに対応して前記機構を有効にするか無効にするかを示すODT制御情報を複数のメモリデバイスのそれぞれに対応して記憶するODT制御レジスタ104,105と、複数のメモリデバイスのアクセス対象のメモリに対応するODT制御情報に基づいて、複数のメモリデバイスのそれぞれのODT機構を制御するODT制御回路112とを有する。

(もっと読む)

電子装置

【課題】1チップマイコンにCMOSメモリを接続した電子装置において、1チップマイコンのアドレスバスのプルアップ抵抗による消費電力を低減する。

【解決手段】リセット信号がラッチ7に入力されると、そのローレベル出力によりトランジスタTR0〜TR20がオンするので、バス2及びラインLiはプルアップ抵抗RA0乃至RA20によりプルアップされる。アドレスデコーダ5で生成されたCS信号がラッチ7に入力されると、ラッチ7のハイレベル出力によりトランジスタTR0〜TR20がオフするので、バス2及びラインLiは電源から切り離される。CS信号生成後はプルアップ抵抗RA0乃至RA20の電流は0になる。

(もっと読む)

高速双方向通信を制御するためのシステム

高速双方向通信を制御するためのシステム(10)は、例えばメモリコントローラなどのマスタデバイス(100)に結合された、例えばメモリデバイス(410)などのスレーブデバイス(110)を有する。前記マスタデバイスは、前記マスタデバイスと前記スレーブデバイス間のデータ転送を制御するように構成されうる。前記マスタデバイスは、前記スレーブデバイスに1つ以上のクロック信号(118)を供給するように構成され、初期化モード中に前記マスタデバイスは前記1つ以上のクロック信号の位相アライメントを変更しうる。更に、前記マスタデバイスは、その後、前記スレーブデバイスから受信される情報に基づいて、前記マスタデバイスから送信するデータの位相アライメントを変更しうる。  (もっと読む)

(もっと読む)

パフォーマンス・モニタリングを提供するメモリ・システム・方法

【課題】メモリ・システムにおいてパフォーマンス・モニタリングシステムおよび方法を提供する。

【解決手段】メモリ・システムは、メモリ・コントローラ、複数のメモリ・デバイス、メモリ・バス、およびメモリ・ハブ・デバイスを含む。メモリ・コントローラは、メモリ・アクセス要求を受信しそれらに応答する。メモリ・ハブ・デバイスは、アドレス情報、制御情報、およびデータ情報の1つ以上を、メモリ・バスを介してメモリ・ハブ・デバイスとメモリ・コントローラとの間で転送するためのメモリ・インタフェースを含む。メモリ・ハブ・デバイスは、メモリ・デバイスに接続するメモリ・デバイス・インタフェースも含む。メモリ・ハブ・デバイスは、システム動作中の規定時間間隔に亘って、メモリ・バスの利用、メモリ・デバイスの利用、およびパフォーマンス特性の1つ以上をモニタし報告するためのパフォーマンス・モニタをさらに含む。

(もっと読む)

自動計算機のためのメモリ・システム

【課題】 自動計算機のためのメモリ・システムを提供すること。

【解決手段】 メモリ・コントローラ及びアウトバウンド・リンクを含み、メモリ・コントローラがアウトバウンド・リンクに接続されている、メモリ・システムが開示される。アウトバウンド・リンクは、典型的には、メモリ・コントローラから第1のメモリ層内のメモリ・バッファ装置にメモリ信号を伝える幾つかの伝導経路と、第1のメモリ層内の少なくとも2つのメモリ・バッファ装置とを含む。第1のメモリ層内の各々のメモリ・バッファ装置は、典型的には、メモリ・コントローラからメモリ信号を受信するようにアウトバウンド・リンクに接続される。

(もっと読む)

リードデータ用のシステムレイテンシーレベライゼーション

【課題】高速メモリシステムにおける全てのメモリデバイスのシステムリードレイテンシーを均一化させるメモリデバイスを提供する。

【解決手段】高速メモリサブシステムにおいて、各メモリデバイスの最小デバイスリードレイテンシーの差と、メモリデバイスとメモリコントローラとの間の信号伝搬時間の差があるため、システムリードレイテンシーが大幅に変化する。そこで、各デバイスのシステムリードレイテンシーの差を比較し、全てのデバイスが同一のシステムリードレイテンシーを示すようにさせるデバイスシステムリードレイテンシーで、各メモリデバイスをオペレートさせることによって、

(もっと読む)

不揮発性メモリのデイジーチェイン配置

フラッシュメモリシステムは、システム・イン・パッケージ(SIP)容器の中に実装されている。前記システムは、フラッシュメモリコントローラと複数のフラッシュメモリデバイスとを有する。単一パッケージまたはモジュールに適用されるSIPは、多数の集積回路(チップ)を有する。フラッシュメモリコントローラは、SIP内の複数のメモリデバイスと外部システムとをインタフェースするように構成されている。メモリデバイスは、デイジーチェインカスケード接続に構成されており、前記デイジーチェインカスケードを通じて転送されたコマンドを介してフラッシュメモリコントローラに制御される。  (もっと読む)

(もっと読む)

21 - 40 / 84

[ Back to top ]