Fターム[5B079BC03]の内容

Fターム[5B079BC03]に分類される特許

41 - 60 / 265

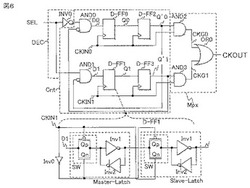

半導体集積回路およびその動作方法

【課題】クロック選択回路の最終選択出力でのメタステーブルの障害の発生確率を低減する。

【解決手段】半導体集積回路に内蔵のクロック選択回路は、デコーダDEC、制御ユニットCnt、マルチプレクサMpxを有する。DECに選択信号SELが供給され、Cntに第1と第2のクロック信号CKIN0、1とデコーダDECの第1と第2の選択出力信号が供給され、MpxにCntの第1と第2の選択制御信号Q´0、1が供給される。Cntの第1と第2のゲートAND0、1の一方の入力にDECの第1と第2の選択出力信号が供給される。第1ゲートAND0の出力と第2ゲートAND1の他方の入力の間に直列接続の第1と第2のD型フリップフロップD−FF0、2と、第2ゲートAND1の出力と第1ゲートAND0の他方の入力の間に直列接続の第3と第4のD型フリップフロップD−FF1、3を含む。

(もっと読む)

半導体集積回路の設計方法、設計プログラム

【課題】半導体集積回路の階層レイアウト設計において、タイミング収束を容易化すること。

【解決手段】第1ブロックは、第1クロック端子と第1フリップフロップを有し、第2ブロックは、第2クロック端子と第2フリップフロップを有する。クロック分配経路は、クロック分岐点から、第1クロック端子を通して第1フリップフロップへつながり、且つ、第2クロック端子を通して第2フリップフロップへつながる。データ経路は、第1フリップフロップのデータ出力端子から第2フリップフロップのデータ入力端子へつながる。本発明に係る設計方法は、(A)製造ばらつきに起因するクロック分配経路におけるクロック信号の遅延変動を反映させながら、データ経路のスラックを算出するステップと、(B)算出されるスラックが増加するように、クロック分岐点、第1クロック端子及び第2クロック端子の位置を変更するステップ、とを含む。

(もっと読む)

クロック供給装置およびクロック供給方法

【課題】インピーダンス整合のためのコストを増大させずに高周波クロック信号の伝送効率を高める。

【解決手段】一実施形態に係るクロック供給装置は、クロック信号を生成するクロックジェネレータ21に接続される第1伝送線路T1と、このクロックジェネレータ21の出力インピーダンスとは異なる入力インピーダンスを持つクロック供給先12Aに接続される第2伝送線路T2と、第1および第2伝送線路T1,T2を容量結合するキャパシタCP1と、第1伝送線路T1上でクロック信号の反射を抑制するプルアップ抵抗RP1と、分圧で得られる電位をクロック信号の基準電位として第2伝送線路T2に印加する一対の分圧抵抗RP3,RP2とを備える。一対の分圧抵抗RP3,RP2は第2伝送線路T2上のインピーダンスをクロック供給先12Aの入力インピーダンスに整合させる抵抗比に設定される。

(もっと読む)

クロックスキュー自動調整回路及びその調整方法

【課題】従来のクロックスキュー調整回路では、精度の高いクロックスキュー調整を行うことができないという問題があった。

【解決手段】本発明にかかるクロックスキュー自動調整回路は、クロックのドライブ能力を調整するクロックドライバ101と、クロックの信号変化開始から信号変化終了までに要する時間を計測する計測回路102と、前記計測時間と予め設定された基準時間とに基づいて制御信号を生成し、前記クロックドライバに対して出力する制御回路103と、を備える。このような回路構成により、精度の高いクロックスキュー調整を行うことができる。

(もっと読む)

クロック分配回路及びクロックスキュー調整方法

【課題】消費電力とクロックスキューを最小限に抑える。

【解決手段】クロック分配回路は、クロック分配領域に格子状に配置され、クロックメッシュを駆動する複数のクロックドライバと、各クロックドライバに対して格子状に割り当てた分割領域毎に、クロックドライバが駆動するクロックメッシュの配線容量及びクロックメッシュに接続した回路素子のクロック端子容量を抽出し、分割領域毎に抽出した総容量から必要なクロックドライバの駆動力を割り出して、ディジタルデータとして保持するクロックドライバ駆動力保持回路と、各分割領域内で必要なクロックドライバの駆動力保持データと、上下方向及び左右方向の分割領域内で必要なクロックドライバの駆動力保持データとをそれぞれ分割領域毎の抵抗比率により平均化して、クロックドライバの駆動力を調整するクロックドライバ駆動力制御回路とを有する。

(もっと読む)

半導体集積回路、動作周波数変更方法及びプログラム

【課題】LSI内部での動作モジュールの切り替え、動作周波数の変更時の急激な電流変動に伴うバウンスノイズにより、電源電圧を動作保証範囲内に抑える事が困難になってきている。また、LSI外部の電圧測定結果に基づき、LSIの動作モジュール、周波数切り替え等を実施する事が可能であるが、パッケージの影響を受け、正確な電圧測定が困難となる。

【解決手段】半導体集積回路に集積され、電源電圧の特定時間内の最大電圧ないし最小電圧を測定する測定手段(042)と、この測定の結果を保持する測定結果保持手段(041)と、測定結果保持手段(041)から測定の結果を読み出すための読み出し手段とを備える。このような構成を備えることで、半導体集積回路内での動作モジュールの切り替え、動作周波数の変更時にも、LSI電源電圧の変動を動作保証電圧範囲内に抑える事が可能となり、LSIの安定動作が可能となる。

(もっと読む)

信号切り替え装置、信号切り替え方法及びデータ受信装置

【課題】互いに非同期で且つ周波数の異なるクロック信号を、ハザード及びデューティ比崩れのいずれも発生させずに切り替えられるようにする。

【解決手段】クロック信号に同期したマスク信号及び同期切り替え信号を切り替え信号に基づいて生成する信号同期生成手段110a及び110bと、クロック信号をマスク信号でマスクすることによりマスククロック信号を生成するクロック信号マスク手段120a及び120bと、第1及び第2の同期切り替え信号のうちのいずれかを選択切り替え信号として選択する同期切り替え信号選択手段130と、選択切り替え信号に基づいて第1及び第2のマスククロック信号のいずれかを選択(出力)クロック信号として選択するマスククロック信号選択手段140とを備える。

(もっと読む)

半導体装置

【課題】 積層された演算LSI間の通信及び演算を同期化することで、システム全体の性能向上を図る。

【解決手段】 積層されたCOMLSI及びLGLSI1は、水晶発振器クロック信号を逓倍するPLL、クロック信号を分配するクロックパルスジェネレータ、フリップフロップ回路を具備する。LGLSI1は、クロック位相比較器(CMP)、ディレイコントローラ(Delay_CTL)、ディレイチェイン(Delay_Chain)からなるDLL回路を具備する。COMLSIとLGLSI1の通信及び演算を同期させるため、COMLSIから同期用基準クロック信号が貫通電極(TVCLK)を介してLGLSI1に送信される。DLL回路により、LGLSI1の内部クロック信号はCOMLSIから同期用基準クロック信号に同期する。

(もっと読む)

クロック制限回路、信号出力回路及び信号入力回路

【課題】対象となる回路の制約を受けずに適用可能なゲーテッドクロック回路を提供すること。

【解決手段】入力回路30への動作クロックCLK2の入力を制限するゲーテッドクロック回路10であって、入力回路30に入力される非同期信号ASYNCと次クロックにおいて入力回路30に入力される次信号DATAとの排他的論理和の信号を出力するXOR101と、XOR101の出力信号を、CLK2に応じて出力するLAT102及びCGFF103と、CGFF103の出力とCLK2の論理積であるゲーテッドクロック信号GCLKを出力するAND104を含む。

(もっと読む)

光データリンク

【課題】クロックストレッチすることなく外部機器とI2C通信を行うことができる光データリンクを提供する。

【解決手段】シリアルクロック線(SCL)におけるシリアルクロック信号SCLのレベルがHレベルの時に、シリアルデータ線(SDA)におけるシリアルデータ信号SDAのレベルがHレベルからLレベルに変化したことを検知すると、内部機器12’の動作クロック速度を上げ、高速な実行が必要な処理を完了した時点で内部機器12’の動作クロック速度を元の状態に下げる動作クロック速度制御部13を備えている。

(もっと読む)

クロック生成回路

【課題】広帯域の周波数範囲におけるどの周波数の基準クロックを受けてもロックする時間を短くできるクロック生成回路を簡易な回路構成で実現。

【解決手段】基準クロックを第1の個数の電圧制御遅延素子12−1〜12−Nで遅延させて第1の遅延クロックを生成し、第2の個数の電圧制御遅延素子12−1〜12−Kで遅延させて第2の遅延クロックを生成する遅延部11と、前記基準クロックの位相と前記第1の遅延クロックの位相とを比較する位相比較部21と、遅延制御電流を出力するチャージポンプ22と、遅延制御部23と、前記基準クロックの位相と前記第2の遅延クロックの位相とを比較し、前記基準クロックと前記第1の遅延クロックとの位相差を判定する判定部13aと、前記位相差が閾値より大きい場合、前記遅延制御電流が第1の値になり、前記閾値以下の場合、前記第1の値より小さい第2の値になるように制御するチャージ制御部13bとを備える。

(もっと読む)

メモリアクセス制御回路とメモリアクセス制御方法

【課題】処理装置と同期式メモリの間のACタイミング条件を緩和することができるメモリアクセス制御回路等を提供する。

【解決手段】プロセッサ1の基準クロック信号CLKは位相調整部10,20に与えられ、それぞれ位相の遅れたクロック信号CKDと位相の進んだクロック信号CKLが生成される。クロック制御部30は、プロセッサ1からデータの読み出し要求が行われると、クロック信号CKLを選択してクロック信号CKを同期式SRAM2へ与えると共に、データ制御部40へ出力する。データ制御部40は、位相の進んだクロック信号CKに同期して同期式SRAM2から読み出されたデータ信号DT2を、このクロック信号CKに同期してデータ信号DT1としてプロセッサ1へ出力する。一方、同期式SRAM2へのデータ書き込み動作は、位相の遅れたクロック信号CKDに同期して行われる。

(もっと読む)

デューティ感知回路およびこれを備えるデューティ補正回路

【課題】デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供すること。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

(もっと読む)

マイクロコンピュータ

【課題】チップ外に出力されるクロック信号と、チップ内のクロック信号との間の位相差を低減する。

【解決手段】第1クロック信号を発生可能な発振器(101)と、上記第1クロック信号とフィードバック信号との位相比較を行い、それに基づいて第2クロック信号を形成するPLL回路(102)とを設ける。さらに、上記第2クロック信号に基づいて、チップ内部に供給される第3クロック信号と、チップ外部に出力される第4クロック信号(CLK(φ))とを形成するクロックパルスジェネレータ(103)と、クロック遅延補正データが格納されるクロック遅延補正データ記憶部(105)とを設ける。上記PLL回路に、上記フィードバック信号を補正するための可変ディレイ回路(13)を設け、上記位相差低減のためのクロック遅延補正を行う。

(もっと読む)

同期メモリアクセス調整回路及びその調整方法

【課題】簡略な構造で、クロック周期以上の遅延に対しても安定したアクセスを実現する同期メモリアクセス調整回路及び調整方法を提供する。

【解決手段】クロック信号30に同期して動作する同期メモリ2にアクセスする同期メモリアクセス調整回路1において、同期メモリ2にデータ読み出し、書き込みのアクセスのために与えるクロック信号31を位相遅延調整するための第1の遅延回路16と、前記アクセス後に同期メモリ2から出力される読み出しデータ46を取り込むためのクロック信号32を位相遅延調整するための第2の遅延回路17と、同期メモリ2から出力される読み出しデータ46をサイクル遅延調整するためのファーストインファーストアウト回路12とを備える。

(もっと読む)

クロック信号供給回路の設計方法、情報処理装置およびプログラム

【課題】半導体集積回路におけるクロック信号の供給において、回路全体を通しクロックラインを短縮し得る構成を提供することを目的とする。

【解決手段】回路素子のグループ間で回路素子の交換、移動を実行し、当該実行の前後でグループごとに回路素子の位置と中心位置との距離の合計し更に全グループについて合計した値が減少する場合には当該実行後のグループを維持し減少しない場合には当該実行前のグループを維持する最適化を実行する構成である。

(もっと読む)

半導体装置およびデータ伝送システム

【課題】メモリ側の多相クロックのずれを補正する。

【解決手段】複数のデータ入出力端子に接続されたデータ入力回路とデータ出力回路とを備えた半導体装置であって、データ入力回路あるいはデータ出力回路の少なくとも一方が、データを取り込むタイミング信号となる位相の異なる多相クロック信号によりデータを取り込み、データを取り込む有効範囲が多相クロック信号ごとにほぼ均一になるように調整する。本発明によれば、入力あるいは出力タイミング信号である多相クロック信号を個別に調整することにより、データのウィンドウ幅を均一にすることができるため、半導体装置の特性を改善することができる。

(もっと読む)

半導体装置及びその制御方法

【課題】半導体装置の製造ばらつきや経年劣化に起因するクロックスキューを補正することができる半導体装置を提供する。

【解決手段】スキュー検出部6は、スキューを検出するための少なくとも1個のクリティカルパス7又はレーシングパス7を含む。クロック調整部5は、スキュー検出部6により検出されたスキューに基づいて、ディレイの設定値を設定する。クロックセル4は、ディレイの設定値に応じて、第1のクロックのディレイを調整して、第2のクロックとして出力する。

(もっと読む)

クロック信号出力回路及びクロック信号出力回路の発振動作方法

【課題】外部発振子を用いずとも、継続して逓倍クロック信号を生成出力できるクロック信号出力回路を提供する。

【解決手段】記憶用メモリ12に、基準クロック信号PREFの周期をリングオシレータ1及び周期カウンタ5によりカウントしたデータを記憶させ、クロック信号出力回路11は、セレクタ13を介すことで、除算器7及びシステムクロック生成部9が記憶用メモリ12に記憶させたデータに基づいて演算処理を行い、逓倍クロック信号を生成して出力する。したがって、外部発振子3を発振動作させて基準クロック信号を常時得る必要がなくなる。

(もっと読む)

DLL回路

【課題】高精度な同期特性を有するDLL回路を提供する。

【解決手段】第1クロック信号CLK1が入力され、第1クロック信号CLK1を遅延した第2クロック信号CLK2を出力するとともに、制御信号Vcにより遅延時間が可変される可変遅延回路11と、第1クロック信号CLK1および第2クロック信号CLK2が入力され、第1クロック信号CLK1と第2クロック信号CLK2との位相を比較して、その位相差ΔΦに応じた信号を出力する位相検出回路12と、位相検出回路12の出力V1を積分する積分回路13と、積分回路13の出力V2を予め定めた基準値Vrefと比較し、比較結果を出力する比較回路14と、比較回路14の出力V3を平均化し、高周波成分を除去した信号を、制御信号Vcとして可変遅延回路11に出力するローパスフィルタ15と、を具備する。

(もっと読む)

41 - 60 / 265

[ Back to top ]