Fターム[5B079BC03]の内容

Fターム[5B079BC03]に分類される特許

61 - 80 / 265

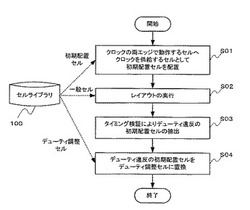

半導体集積回路の設計方法

【課題】レイアウト後のクロックのデューティ調整を容易に行なうことのできる、半導体集積回路の設計方法を提供する。

【解決手段】、クロックの両エッジで動作するセルへクロックを供給するセルとして初期配置セルを配置した後、クロックツリーの配置、クロック配線、セル間配線などのレイアウトを実行し、レイアウト実行後の実配線長にもとづくタイミング検証を行って、デューティ値の規定を満たさないデューティ違反が発生している初期配置セルを抽出し、デューティ違反の初期配置セルを、レイアウト上の配置位置はそのままで、外形サイズ、入出力端子位置、入力容量および出力駆動力が初期配置セルと同じで、デューティが規定値を満たすように調整されたデューティ調整セルに置換する。

(もっと読む)

半導体集積回路

【課題】クロック信号の位相、デューティー比等の変動に対し耐性の強い、小型の半導体集積回路を提供する。

【解決手段】複数配設される回路部と、クロック信号の立ち上がりエッジから前記クロック信号を逓倍した周期の第1信号を生成する第1カウンタと、前記クロック信号の立ち下がりエッジから前記クロック信号を逓倍した周期の第2信号を生成する第2カウンタと、前記第1信号が転送される第1ラインと、前記第2信号が転送される第2ラインと、前記第1ライン及び前記第2ラインと接続され前記第1信号と前記第2信号との位相差から第3信号を生成し前記回路部に前記第3信号を出力する位相比較器と、を備え、前記位相比較器は、前記第1ライン及び前記第2ライン上に配設され且つ前記第1ライン及び前記第2ラインの末端と前記回路部との間に複数配設される。

(もっと読む)

信号同期のための改善された方法、システムおよび装置

本稿で開示されるシステムは、二つ以上の放送/マルチメディア設備源から発する関係しない情報および/または参照信号を同期させるのに好適である。ここで、前記信号は異なる信号フォーマットである、および/または受信装置において異なる遅延を受けるのでもよい。本システムは、パケット・ネットワークを介して複数のスレーブ参照信号生成器の少なくとも一つに接続されたマスター参照時間生成器を有する。マスター参照時間生成器は、マスター参照時間カウンタおよび該マスター参照時間カウンタをサンプリングするためのサンプリング装置を有する。マスター参照時間生成器は時間データをマスター参照時間パケットにエンコードし、これらのパケットをパケット・ネットワークにフィードする。複数のスレーブ参照信号生成器のうちの前記少なくとも一つは、参照信号を生成するために、エンコードされた時間データを入力として受け入れるよう適応されている。生成される参照信号の位相は、ある初期時間点からの経過時間に基づいて計算される。スレーブ参照信号生成器は、前記初期時間点から経過した時間データを生成するためのスレーブ参照時間カウンタを有する。スレーブ参照時間カウンタは、スレーブ参照時間カウンタをサンプリングするためのサンプリング装置に接続される。マスター参照時間カウンタおよびスレーブ参照時間カウンタは、マスター参照時間生成器およびネットワークのスレーブ参照信号生成器のすべての上で同期された時間ベースから導出された時間点においてサンプリングされる。  (もっと読む)

(もっと読む)

絶対遅延時間発生装置

【課題】外部水晶体を参照信号源とせずに、正確な周波数を発生する。

【解決手段】PVT検知装置は複数の遅延モジュールと信号位相/周波数制御モジュールを含む。各遅延モジュールは対照ユニットと参照ユニットを含む。対照ユニットと参照ユニットは互いにPVTに対する異なる感度の遅延特性を有する。各遅延モジュールは入力信号がそれぞれ対照ユニットと参照ユニットを通ってから生じた位相又は周波数の相違を対照し、各遅延モジュールの遅延パラメータを発生する。信号位相/周波数制御モジュールは各遅延パラメータを受けて対照し、絶対遅延時間発生装置の外部環境のPVT状態を検出し、遅延時間発生器を制御して補正することにより、正確な絶対遅延時間を発生する。

(もっと読む)

半導体装置

【課題】ノイズ又はジッタの影響により不安定な位相比較結果が出ても、クロック整合トレーニング動作の安定した結果を外部コントローラに伝送することができる回路を提供する。

【解決手段】第1クロックHCKの位相を基準として第2クロックWCKの位相を検出し、当該検出結果に対応する第1検出信号DET_SIG1を生成する第1位相検出手段430と、第2クロックWCKを所定時間だけ遅延したクロックDLY_DIV_WCKの位相を、第1クロックHCKの位相を基準として検出し、当該検出結果に対応する第2検出信号DET_SIG2を生成する第2位相検出手段440と、出力信号を出力し、第1検出信号DET_SIG1、第2検出信号DET_SIG2、及びフィードバックされた出力信号TRAINING_INFO_SIGに応答して、出力信号TRAINING_INFO_SIGの論理レベルを決定する論理レベル決定手段450と、を備える。

(もっと読む)

信号処理装置および信号処理方法

【課題】 相互に異なる周期のクロック信号が与えられ、かつ相互に非同期で所定の処理を行う複数の処理部のリセットを、簡単な構成で、確実に行うことができる信号処理装置および信号処理方法を提供する。

【解決手段】 モジュール回路部14は、モジュールA,B,Cのうちのいずれかに対するリセット指令が与えられると、指令されたモジュールを指定する信号を含み、かつCPUCLKの1周期分の長さを有する1shotリセット信号を生成する。同期リセット生成回路部15は、1shotリセット信号が与えられ、この1shotリセット信号の長さを指令されたモジュールに対応する長さに引き延ばした伸長リセット信号を生成し、生成した伸長リセット信号を指令されたモジュールのクロックに同期させて同期リセット信号を生成し、指定されたモジュールでは、同期リセット信号が与えられた状態で、クロック信号が立上がりまたは立下ると、リセットされる。

(もっと読む)

半導体集積回路

【課題】LSI チップ内に互いに独立した電源を使用する複数の領域が混在する場合、両領域で発生する信号の相対的な遅延差を補償し、信号のタイミングマージンを余計に確保する必要をなくし、チップの面積や消費電力の増大を抑制する。

【解決手段】同一チップ内に互いに独立した電源を使用する複数の領域11,12 が混在するLSI において、複数の領域で発生する信号の相対的な遅延差をチップ内に保持されている設定情報に応じて補償し、複数の領域相互で信号のタイミングを調整する手段13,14 を具備する。

(もっと読む)

冗長切替制御システム、方法及びプログラム

【課題】冗長構成において、切替事象発生時に、それまでの運用系の用いていたクロックを予備系に対して迅速に同期させ、対向装置との間でクロック同期外れを回避できるようにする。

【解決手段】本発明の冗長切替制御システムは、複数の運用系と、各運用系の収容する各対向装置と接続している受信回線を収容し、いずれかの受信回線の接続を選択する受信回線選択手段と、受信回線選択手段の選択した受信回線から通常時でのクロックを抽出してクロック同期を行うクロック同期手段とを有する1以上の予備系と、切替事象発生時に、受信回線選択手段に対して切替先回線の選択指示を行う冗長切替制御手段とを備えることを特徴とする。

(もっと読む)

クロック分配回路のレイアウト生成方法、および半導体集積回路装置

【課題】再収斂分岐構造を含むクロック分配回路のレイアウト生成において、冗長な迂回配線を生じさせることなく、クロックスキューを低減可能にする。

【解決手段】クロック分配回路の基本セル構成を解析し(S201)、解析された基本セル構成を基にして、クロック経路にクロックバッファを挿入する(S202)。その後、基本セルとクロックバッファとを配置し(S203)、配線を配置する(S105)。解析ステップ(S201)において、クロックの各経路における基本セルの段数の最大値を求め、挿入ステップ(S202)において、クロックの各経路におけるセル段数が、この最大値以上でかつ同じ値になるように、クロックバッファを挿入する。

(もっと読む)

クロック信号分周回路および方法

【課題】大きな回路規模を必要とすることなく、有理数分周した出力クロック信号のサイクル時間変動を抑制するとともに、分周時に出力クロック信号の位相を調整する。

【解決手段】クロック選択制御回路100により、入力クロック信号のサイクルごとに、分周比に応じた一定サイクル時間を有する基準分周クロック信号と入力クロック信号との位相関係を示す位相計算値111を計算するとともに、位相調整信号に応じてその値を増減し、この位相計算値111に基づいて、出力動作のうち、基準分周クロック信号の位相と近いクロック信号を生成するための出力動作を指示する制御信号102,103を生成する。クロック選択回路101により、制御信号102,103に基づいて、入力クロック信号のクロックパルスをそのまま非反転で出力するか、反転して出力するか、マスクして出力しないか、のいずれかの出力動作を選択して実行することにより、出力クロック信号を生成する。

(もっと読む)

信号処理装置

【課題】0と1の出現確率が異なるデータ信号のデューティサイクルの歪みを補正する。

【解決手段】位相検出回路21は、0と1の出現確率が異なるデータ信号の位相の進みおよび遅れを検出する。AND回路43はデータ信号の立ち上がりを検出し、AND回路44は立ち下がりを検出する。+DCD検出回路45は、位相検出回路21とAND回路43および44の検出結果に基づいて、デューティサイクルのプラス側の歪みを検出し、−DCD検出回路46は、デューティサイクルのマイナス側の歪みを検出する。デューティ調整回路12は、+DCD検出回路45と−DCD検出回路46の検出結果に基づいて、デューティサイクルを調整することにより、デューティサイクルの歪みを補正する。本発明は、例えば、データ信号を受信する受信装置に適用することができる。

(もっと読む)

半導体装置及びデータプロセッサ

【課題】並列動作される複数のメモリデバイスに共通接続するコマンド及びアドレス信号とメモリデバイスに接続するクロック信号との同期化をクロック配線長の増大を極力抑えて実現する。

【解決手段】配線基板に搭載されたデータ処理デバイスとこれによって並列アクセスされる複数個のメモリデバイスとを有する。データ処理デバイスはコマンド及びアドレス端子から第1の周波数でコマンド及びアドレス信号を出力し、前記クロック端子から第2の周波数でクロック信号を出力する。前記第2の周波数は第1の周波数の複数倍とされ、前記コマンド及びアドレス端子から出力されるコマンド及びアドレス信号には前記クロック端子から出力されるクロック信号のサイクル開始位相と同等又はそれよりも早い出力タイミングが選択可能にされる。

(もっと読む)

クロック供給回路

【課題】動作条件が厳しい場合でも、クロックゲーティング信号を含む経路のタイミング違反の発生を防ぐことができるクロック供給回路を提供する。

【解決手段】クロック供給回路1は、クロックツリー13からのクロック信号に基づく信号を複数のインバータ回路32a及び32bによって遅延させ、複数のインバータ回路32a及び32bによる遅延量に基づいてタイミング違反を推定するモニタ回路17を有する。さらに、クロック供給回路1は、モニタ回路17の推定結果に基づいて、組合せ回路16により生成されたクロックゲーティング信号を制御するOR回路18と、OR回路18の出力信号に基づいて、クロック信号を供給又はクロック信号の供給を停止するクロックゲーティング回路12とを有する。

(もっと読む)

クロック分配システム、分配方法、それらを利用した集積回路

【課題】消費電力と劣化を低減する。

【解決手段】集積回路にクロック信号を分配する装置100、方法が提供される。低速モード動作において、周期ごと、少なくとも、異なる第1、第2オン時間を有する第1、第2オンパルスを含み、第1、第2オン時間の合計が、各周期のオフ時間の合計と略等しい第1クロック信号200が生成される。分配クロック信号204それぞれを生成する複数の最終段のバッファ回路17が終点である分配ツリー16を介して第1クロック信号200が分配される。分配クロック信号204それぞれから、集積回路の少なくとも一部に供給すべき対応する第2クロック信号202が生成される。

(もっと読む)

入出力端子共用クロック周波数選択発振回路

【課題】本発明は、クロックを数多く変更可能で、LSIのクロック入力用のピン数を大幅に削減でき、クロックが安定したら自動的に信号入力用のピンに変更できる入出力端子共用クロック周波数選択発振回路を提供することを目的とする。

【解決手段】選択信号が入力されることで選択信号に応じた所定の周波数のクロック信号を発生させると共に、発生させたクロック信号が安定したことを示すロック信号を出力するPLL発振回路2と、入力手段を介して入力される入力信号を保持しPLL発振回路2に選択信号として出力するフリップフロップと、入力手段とフリップフロップとの間に設けられ該入力手段からの入力信号をフリップフロップへ伝達すると共に、PLL発振回路2からのロック信号が入力されると入力手段からの信号をI/O制御回路4へ伝達するよう切換えるI/O切換え回路3とを備えたことを特徴とする。

(もっと読む)

半導体集積回路

【課題】雑なクロック選択回路に対応できる半導体集積回路を、簡単な配置クラスタリング工程で作製できるようにする。

【解決手段】クロック信号を種々の遅延量で遅延調整するクロックツリー回路と、遅延調整されたクロック信号が供給されるクロック同期回路とを備える。クロックツリー回路は、クロック信号導入端の後段に設けられた第一のクロックツリーセルと、クロック同期回路の前段でかつ第1のクロックツリーセルより後段に設けられた第二のクロックツリーセルと、第二のクロックツリーセルの前段に設けられたクロック分岐点とを備える。クロック同期回路は第二のクロックツリーセルで遅延調整されたクロック信号が供給される第一のクロック同期回路とクロック分岐点でクロックツリー回路から出力されるクロック信号が供給される第二のクロック同期回路とを備える。

(もっと読む)

クロック分配回路の設計方法

【課題】消費電力を抑制しつつ、スキューの抑制およびスラックの増大を可能にするクロック分配回路の設計方法を提供する。

【解決手段】クロック分配回路の設計方法は、バッファの位置および配線の位置を設定し、クロック分配回路の共通ノードから第1の回路素子までのクロック伝達時間およびクロック分配回路の共通ノードから第2の回路素子までのクロック伝達時間を計算し、共通ノードから第1の回路素子までの第1の経路と共通ノードから第2の回路素子までの第2の経路との間のいずれかの箇所を短絡する短絡配線を設定することによって、共通ノードから第1の回路素子までのクロック伝達時間のばらつきおよび共通ノードから第2の回路素子までのクロック伝達時間のばらつきだけ、第2の回路素子が受け取るデータと第2の回路素子が受け取るクロックとの間のスラックを改善することを具備する。

(もっと読む)

分周回路及び分周方法

【課題】複数段の1/2分周器により分周された各信号において、全ての分周信号同士が同期し、かつクロック信号の同一のエッジに同期した分周信号を出力することが可能な分周回路及び分周方法を提供する。

【解決手段】第1の同期回路群は、分周器群と第1の同期回路群との間に設けられ、分周器群からの各分周信号を入力とし、その出力が第1の同期回路群のラッチ回路の各入力端子に接続されたN段のラッチ回路からなり、第1段目から第M段目のラッチ回路のクロック入力端子にはクロック信号が入力され、クロック信号に同期した信号を出力し、第(M+1)段目から第N段目までのラッチ回路のクロック入力端子には第M段目のラッチ回路の出力信号が入力され、M段目のラッチ回路の出力に同期した信号を出力する第2の同期回路群を有する。

(もっと読む)

遅延制御回路及び遅延制御方法

【課題】遅延制御回路における定常位相誤差を排除できる構成の提供。

【解決手段】第1の可変遅延回路及び第1の位相制御回路を備えた遅延制御回路において、更に、第1、第2のクロックパスのいずれか一方に配された第2の可変遅延回路と、前記第2の可変遅延回路に対する遅延値を用いて、前記第1のクロックパス又は第2のクロックパスに対し、前記第1の位相調整回路にて発生する定常位相誤差を相殺する追加のフィードバックループを形成するよう配設される第2の位相調整回路と、を備える。

(もっと読む)

クロック配線処理装置、クロック配線処理方法、及びプログラム

【課題】 パス始点F/F終点F/F間の遅延を最小化する、最終段クロックドライバから始終点F/Fへクロック信号クロックを配線する。

【解決手段】 始終点F/Fリストを記憶部に抽出し、始終点F/Fへ接続する最終段クロックドライバ候補を選択して記憶部に格納する始終点F/F処理部と、始点F/F終点F/Fへ接続する最終段クロックドライバ候補の組み合わせから、最終段クロックドライバ間クロックスキューが最小になる始終点F/Fに接続する最終段クロックドライバを選択して記憶部に格納するクロックスキュー処理部と、を備えることを特徴とする。

(もっと読む)

61 - 80 / 265

[ Back to top ]