Fターム[5B079BC03]の内容

Fターム[5B079BC03]に分類される特許

1 - 20 / 265

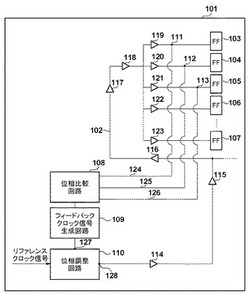

クロック分配回路及びクロック分配回路の形成方法

【課題】 28nm以降の半導体プロセスでは、チップ内バラツキが顕著になったため、フィードバックパスにトランジションフォルトが発生する頻度が上がった。従来技術ではフィードバックパスのトランジションフォルトが発生した場合の対策がなく、歩留まり低下につながる。

【解決手段】 クロック信号が分配されるクロックツリーと、クロックツリーの異なる分岐点から出力される複数のフィードバッククロック信号を受信し、各フィードバッククロック信号の位相差を検知する位相比較回路とを有する。位相比較回路によって検知した位相差に基づいて、半導体集積回路内の製造バラツキを補正するためのバラツキ補正済フィードバッククロック信号を生成するフィードバッククロック信号生成回路を有する。フィードバッククロック信号生成回路によって生成されたバラツキ補正済フィードバッククロック信号と基準クロック信号との位相差が小さくなるようにクロック信号を遅延する位相調整回路を有する。

(もっと読む)

クロック出力回路

【課題】クロック出力回路1にて電流消費を抑えつつ、周波数が安定したクロックを出力する。

【解決手段】 発振回路10から出力される発振信号を論理否定するNOTゲート21A、22Aと、NOTゲート21Aの出力信号を論理否定するNOTゲート23と、NOTゲート22A、23の出力信号を入力信号とするRSフリップフロップ回路24とを備え、NOTゲート21Aの第1の閾値Th1はNOTゲート22Aの第2の閾値Th2よりも大きく、発振信号の周波数が高くなるほど第1の閾値Th1が大きくなり、発振信号の周波数が高くなるほど第2の閾値Th2が小さくなる。発振回路10の発振子11の発振が安定化する前では、RSフリップフロップ回路24が源クロックの出力を待機し、周波数が低くなるとRSフリップフロップ回路24が源クロックを出力する。

(もっと読む)

クロック分周装置

【課題】緩い制約条件の下で、複数の分周回路の分周動作開始タイミングを揃える。

【解決手段】ゲート信号生成回路14は、分周回路11及び12のリセット信号入力点B及びCに入力されるべきリセット信号を入力点Fにて受け、入力点Fでのリセット信号を数クロックサイクルだけ遅延させた信号をゲート信号として出力する。ゲート回路13は、自身に入力されるソースクロックを出力点hから出力するか否かをゲート信号に応じて制御する。出力点hから出力されたソースクロックは、ゲーテッドクロックとして分周回路11及び12のクロック入力点b及びcに入力される。入力点B及びCへのリセット信号によって各分周回路のリセットが解除され各分周回路の分周動作が許可された後に、ソースクロック(ゲーテッドクロック)が入力点b及びcに入力されるよう、リセット信号の遅延によるゲート信号生成及びゲート回路制御が成される。

(もっと読む)

位相補間回路及びその設計方法

【課題】トランジスタのばらつきによる影響を抑制し、位相歪みを解消する位相補間回路を提供する。

【解決手段】位相補間回路は、位相の異なる入力波形を受け付ける複数の差動対を含み、複数の差動対のうち、第1の差動対及び第2の差動対の出力波形を合成する位相補間回路である。さらに、複数の差動対にバイアス電流を供給する電流源をn個含み、第1の差動対に供給するバイアス電流を、n個の電流源のうち、m個の電流源から供給可能であると共に、第2の差動対に供給するバイアス電流をn個の電流源のうち、n−m個の電流源から供給可能であって、n個の電流源が供給する電流は、予め定められた単位電流値を基準として、それぞれ重み付けがされている可変電流源と、出力波形の位相シフト量に基づいて、可変電流源のm個の電流源の数を変更する制御回路と、を備えている。

(もっと読む)

マイコンのクロック制御回路

【課題】 プロセッサクロックの切替によって不具合が生じることを防いで、実行中の動作を正常に継続させることが可能なマイコンのクロック制御回路を提供する。

【解決手段】 本発明の代表的な構成は、プロセッサ102のプロセッサクロック132を変更可能なマイコンのクロック制御回路110において、入力クロック(PLLクロック130)を分周してプロセッサクロック132を生成する分周器114と、プロセッサクロック132と他の回路のクロック(周辺クロック134、通信クロック136)との同期タイミングを検出して分周器114に対し分周比の変更を指示する変更イネーブル信号140を出力する変更イネーブル回路122と、を備えることを特徴とする。

(もっと読む)

デイジーチェーンカスケードデバイス

【課題】デバイスをデイジーチェーンカスケード配列でシリアルに連結する。

【解決手段】デバイスはデイジーチェーンカスケード配列で連結され、第1デバイスの出力部は、データ、アドレス及びコマンド情報等の情報並びに制御信号を第2デバイスに第1デバイスから転送するように、デイジーチェーンカスケードの後方にある第2デバイスの入力部に連結されている。デイジーチェーンで連結されたデバイスは、シリアル入力部SIとシリアル出力部SOとを備える。情報がデバイスにSIを通じて入力され、該情報がデバイスからSOを通じて出力される。デイジーチェーンカスケードの前方のデバイスのSOは、デイジーチェーンカスケードの後方のデバイスのSIに連結されている。前方のデバイスにSIを通じて入力された情報は、該デバイスのSOを通じて出力される。該情報は次いで、後方のデバイスのSIに転送される。

(もっと読む)

タイマ回路、その制御方法、マイクロコンピュータ及び空気清浄機

【課題】クロック信号が切り替えられた際の不具合の発生を低減する。

【解決手段】本発明に係るタイマ回路110は、入力クロック信号115を用いてカウント値134をカウントするカウンタ123と、入力クロック信号115が変更された際に、基準値135として第3設定値133を選択する選択部125と、カウント値134が基準値135分変化したタイミングで変化するタイマ出力信号116を生成する比較部127と、現在のカウント値より大きい値を第3設定値133として演算する第3設定値演算部124とを備える。

(もっと読む)

グリッチフリークロック信号マルチプレクサ回路および動作の方法

【課題】クロックマルチプレクサを駆動する第1のクロック入力から第2のクロック入力への切換えにおいて起こるグリッチを低減する。

【解決手段】クロックマルチプレクサ116は、第1のクロック入力を受信し、クロック出力118を提供し、第1のクロック出力における低フェーズ入力レベルに応答してクロック出力における低フェーズ出力レベルを判定する。限定された期間、低フェーズ出力レベルは、第1のクロック入力信号のフェーズレベルに関わらず維持される。クロックマルチプレクサ116は、第2のクロック入力を受信し、第2のクロック入力信号における低フェーズ入力レベルを判定する。第2のクロック入力に応答してクロック出力118を提供することへの切換えは、第2のクロック入力信号における低フェーズ入力レベルの間に起こる。その後、クロックマルチプレクサ116の出力は第2のクロック信号のフェーズレベルに従う。

(もっと読む)

クロック逓倍回路及び半導体装置

【課題】逓倍されたクロック信号のパルス数が逓倍数の値からずれる状態を原理的に阻止することができるクロック逓倍技術を提供する。

【解決手段】第2クロック信号(CLK2)のサイクル単位で、第1クロック信号(CLK1)の計数値を逓倍数で除した商の値に対応するサンプリングクロックサイクル数を単位として第3クロック信号(CLK3)を順次生成すると共に、生成された一つの逓倍クロックサイクルにおいて前記商の余りに対応する当該サンプリングクロックのサイクル期間に対応して逓倍クロック信号の変化を抑止する制御(106)を行う。

(もっと読む)

半導体装置

【課題】クロック生成回路からクロック信号を受けるドライブ回路の経年劣化を抑制する。

【解決手段】半導体装置1は、クロック信号INT1−SIGを生成して出力するクロック生成回路2と、クロック生成回路2からクロック信号INT1−SIGを受けるドライブ回路3とを備え、クロック生成回路2は、クロック信号INT1−SIGを生成して出力ノード2aから出力するクロック出力モードと、出力ノード2aの電位をハイレベルに固定する第1のクロック停止モードと、出力ノード2aの電位をロウレベルに固定する第2のクロック停止モードとを有する。

(もっと読む)

クロック供給装置およびクロック供給方法

【課題】発振器のウォームアップの完了を容易に判定できるようにする。

【解決手段】クロック供給装置1は、通信装置内の処理に用いられるクロック信号を供給する。発振器1aは、クロック信号を生成する。測定部1bは、通信装置に接続された伝送路から抽出されたリファレンスクロック信号を取得し、クロック信号とリファレンスクロック信号との周波数ずれを測定する。判定部1cは、周波数ずれの測定結果と電力供給の状況とに基づいて、発振器1aのウォームアップが完了したか否か判定する。

(もっと読む)

集積回路設計装置及び集積回路設計方法

【課題】クロック線上における消費電力を効果的に抑えることが可能な集積回路を設計する集積回路設計装置を提供する。

【解決手段】開示の装置は、消費電力算出手段と、消費電力比較手段と、クロックツリー生成手段とを備える。消費電力算出手段は、クロック線上における、クロックゲーティングセルをクロックソース側及びクロックシンク側に配置した場合の第1及び第2の消費電力を算出する。クロックツリー生成手段は、第1及び第2の消費電力の比較により、消費電力が小さいと判定された方の配置の仕方で、クロックゲーティングセルをクロック線上に配置する。ここで、消費電力算出手段は、クロックゲーティングセルのイネーブル率と、クロック線上における消費電力のダイナミック電力成分とスタティック電力成分との比率と、に基づいて、第1及び第2の消費電力を算出する。

(もっと読む)

情報処理装置又は情報処理方法

【課題】情報処理装置と外部装置の夫々が異なる周波数変動範囲を有する周期信号で動作する場合であっても、同期信号(基準クロック)の周波数偏差に起因するホスト間接続の不具合を抑制する方法を提供する。

【解決手段】第1同期信号を生成する生成手段と、前記生成手段の生成した第1同期信号と外部装置から受信する第2同期信号から1つを選択する制御手段と、前記制御手段の選択した同期信号に基づいて前記外部装置と通信する第1通信手段との構成で実現する。

(もっと読む)

制御装置

【課題】起動時間をより短縮すること。

【解決手段】決済端末装置1は、主電源VMのオン/オフを操作する電源操作部14と、バッテリ電源VBを利用してクロック信号を常時生成する外付けの時計IC20と、時計IC20が生成したクロック信号に従って、主電源VMからの電力を利用して各種制御処理を実行するCPU16と、を備え、CPU16は、電源操作部14によって主電源VMがオフ状態からオン状態に切り替えられたとき、時計IC20が生成したクロック信号に従って起動処理を実行する。これにより、水晶発振器からのクロック信号を用いずに起動処理を開始することができるので、水晶発振器の発振出力が安定するまで待機する必要がなくなり、起動時間を短縮することができる。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

クロック発生回路

【課題】ピーク電力の抑制が可能なクロック発生回路を提供すること。

【解決手段】基準クロック11のエッジをカウントし所定のクロックサイクル数毎にタイミング信号を生成するカウンタ回路5と、所定のクロックサイクル数と等しいビット数を有するビットマップ情報14aを記憶するビットマップ回路4aと、基準クロック11からビットマップ情報14aが示す組み合わせでパルスを間引きして間欠するパルス列である間欠クロック12aを生成しタイミング信号に応じて出力する間欠クロック生成回路2aと、所定のクロックサイクル数と等しいビット数を有するビットマップ情報14bを記憶するビットマップ回路4bと、基準クロック11からビットマップ情報14bが示す組み合わせでパルスを間引きして間欠するパルス列である間欠クロック12bを生成しタイミング信号に応じて出力する間欠クロック生成回路2bと、を有する。

(もっと読む)

半導体装置及び遅延量調整方法

【課題】クロック信号の位相を遅延させる遅延回路とその遅延量を調整する回路とを備えた半導体装置において遅延量がクロック信号の周期的なジッタの影響を受けないようにする半導体装置及び遅延量調整方法を提供する。

【解決手段】第1のクロック信号を遅延させた第2のクロック信号を出力する可変遅延回路と、可変遅延回路における遅延量を制御する制御信号を出力する遅延量調整回路と、遅延量調整回路が制御信号を更新するタイミングを決定するタイミング信号を出力するタイミング信号発生回路と、を備えた半導体装置であって、タイミング信号発生回路は連続してタイミング信号を出力するものであって、互いに隣接するタイミング信号の間隔の内、少なくとも2つの間隔が互いに異なる。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

デジタル信号処理回路、デジタル信号処理方法、及び、プログラム

【課題】セットアップタイム及びホールドタイムのマージンを十分に確保することが可能なデジタル信号処理回路を提供すること。

【解決手段】回路は第1の遅延量を複数の判定用遅延量のそれぞれに設定する。回路は入力データ信号を、第1の遅延量だけ遅延させた第1の遅延データ信号と第2の遅延量だけ遅延させた第2の遅延データ信号とを出力する。回路は、第1の遅延データ信号をラッチすることにより第1のラッチデータを取得し、第2の遅延データ信号をラッチすることにより第2のラッチデータを取得する。回路は、複数の判定用遅延量のそれぞれに対して、第1のラッチデータと第2のラッチデータとが一致しているか否かを判定し、当該判定結果に基づいて第1のラッチデータと第2のラッチデータとを一致させるように、第1の遅延量を第1の制御遅延量に設定し且つ上記第2の遅延量を第2の制御遅延量に設定する。

(もっと読む)

データ伝送回路

【課題】互いに独立した非同期のクロックパルスで動作する前段フリップおよび後段フリップフロップを含むデータ保持回路において、クロックパルス同士が競合する場合でも、後段のフリップフロップにおける出力間の不整合を防止する。

【解決手段】データ伝送回路は、入力されるデータを第1のクロックパルスに応じて保持し、前段の出力データを、第1のクロックパルスとは非同期の第2のクロックパルスに応じて保持し、後段のデータ保持回路に転送する。パルス生成手段は、第1のクロックパルスのエッジと第2のクロックパルスのエッジが異なるタイミングで生じている場合には、第2のクロックパルスに同期したパルスを生成し、二つのクロックパルスのエッジが同一のタイミングの場合には、第2のクロックパルスに生じているエッジを除去したパルスを生成する。後段のデータ保持回路は、パルス生成手段のパルスに同期して前段の出力データを保持する。

(もっと読む)

1 - 20 / 265

[ Back to top ]