Fターム[5B079BC03]の内容

Fターム[5B079BC03]に分類される特許

81 - 100 / 265

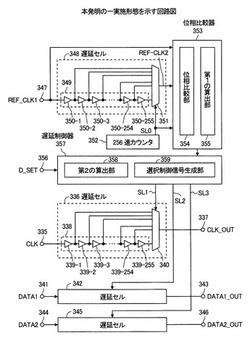

遅延調整回路

【課題】遅延セルとして専用のハードマクロを必要とせず、かつ、遅延調整対象信号について高精度の遅延調整を行うことができる遅延調整回路を提供する。

【解決手段】位相比較器353で、セレクタ351なしに基準クロック信号REF_CLK1を1周期遅延させるのに必要な遅延セル348内のユニットセルの段数pと、ユニットセルの段数に換算したセレクタ351の遅延分qとを、基本情報として算出する。遅延制御器357で、クロック信号CLK及びデータ信号DATA1、DATA2を位相量θa°、θb°、θc°だけ遅延させるのに必要な遅延セル336、342、345内のユニットセルの段数wa、wb、wcを{(遅延位相量指示信号D_SETが指示する遅延位相量θa°、θb°又はθc°/360°)×p−q}という計算式で算出する。

(もっと読む)

制御装置

【課題】簡易な処理でノイズによる誤動作を低減できる制御装置を提供する。

【解決手段】デジタル回路10全体にわたって複数の箇所に配置された複数のノイズモニタ11により得られたノイズに関するアナログ量は、アナログ/デジタル変換器12により最大デジタル量へ変換され、周波数/電圧制御回路40へ入力される。周波数/電圧制御回路40は、最大デジタル量のうち基準デジタル量を上回るものが一つでもあった場合には、電源電圧がNGであると判定し、クロック発生装置20から出力されるクロックの周波数やレギュレータ30から出力される電源電圧を変更しない。

(もっと読む)

機能拡張装置

【課題】 近年、MEAP-Lite等のインテリジェンスを持つオプション機器が開発されるなど、その高機能さゆえにオプション機器の消費電力が増大している。しかしながら低速SFPなど電源能力の乏しい製品では、電源容量の制限から複数のオプションスロットを設定ができないという課題が存在する。また、オプション機器の装着数に応じて均等に供給電力を分配し、オプション機器側では供給電力に合うように動作周波数を下げて動作することで前記課題に対する提案がなされているが、高性能を要求されるオプションへの供給電力が小さくなった場合に性能が著しく低下するという課題が残っている。

【解決手段】 本体側に電力供給情報保持手段を持つ。拡張機器側には、周波数-消費電力対応情報保持手段と周波数切り替え手段と性能情報保持手段を持つ。

(もっと読む)

クロック発生回路

【課題】高精度な周波数変調が可能なスペクトラム拡散クロック発生回路を提供する。

【解決手段】このスペクトラム拡散クロック発生回路において、PLL回路31は、それぞれ位相の異なるクロック信号CLKV1〜CLKV5を出力する。セレクタ23は、クロック信号CLKV1〜CLKV5のうちのいずれか1つを選択し、制御回路24はセレクタ9の信号選択動作を制御する。入力分周回路1は選択クロック信号を分周して基準クロック信号CLKRを出力する。PLL回路21は、基準クロック信号CLKRを周波数逓倍した発振クロック信号CLKOを生成する。これにより、発振クロック信号CLKOの位相を微調整することができる。したがって、高精度な周波数変調が可能なスペクトラム拡散クロック発生回路が実現できる。

(もっと読む)

入出力回路

【課題】チップ温度が上昇した場合でも外部と通信できる入出力回路を提供する。

【解決手段】入出力回路は、複数の周波数のクロックを発生するクロック発生部11と、チップの温度を測定する温度測定部12と、前記チップの温度と、その温度における最大転送速度とを対比させたテーブルを記憶する記憶部13と、前記温度測定部から入力された測定温度と、前記テーブルとを照らしあわせ、前記チップの温度に応じた最大転送速度で外部とのリンクを確立するように前記クロック発生部を制御する制御部14とを具備する。

(もっと読む)

メソシンクロナス・データ・バス装置及びデータ伝送方法

メモリ・システムにおける指定されたポイント間の全体の時間遅延が一定に維持されるように、メモリ・モジュール間のデータの伝送時間が管理される、メモリ・システムについて説明される。多数のレーンのバスの各レーンを別個に管理することができ、中間モジュールにおいてスキュー除去する必要なしに、宛先モジュールにおいてデータフレームを評価することができる。バス・シリアル・データ速度の1つ又それ以上の約数でモジュールを通してデータ経路を作動させ、受信されたデータのサンプリング・ポイントを選択し、温度変化又は時間経過に起因する時間遅延の変動を調整することによって、データを経路指定するためのスイッチを有するモジュールを通したデータの伝播における時間遅延が低減される。 (もっと読む)

タイミング制御回路及び半導体記憶装置

【課題】プロセスや動作環境等の変化に対して、遅延変動の小さいタイミングを生成しアクセス時間を短縮可能とする、タイミング制御回路及び該タイミング制御回路を備えた半導体記憶装置を提供する。

【解決手段】周期T1を持つ第1のクロック信号と、周期T2の第2のクロック群(CKb)が入力され、疎調遅延回路(CD)と微調遅延回路(FD)を備え、疎調遅延回路(CD)は活性化信号の活性化から第1のクロック信号の立ち上がりエッジをカウントするカウンタを有し、第1のクロック信号からの遅延量がほぼm・T1である疎調タイミング信号(CT)を生成し、微調遅延回路(FD)はL個の並列した多相クロック制御遅延回路からなり、それぞれL相の第2のクロック群による疎調タイミング信号(CT)のサンプリングのタイミングをn・(T2/L)だけ遅延させ、遅延されたパルスのORをとることで微調タイミング信号(FT)とする。

(もっと読む)

クロック制御回路および半導体集積回路

【課題】回路設計を容易に行うことができる。

【解決手段】半導体集積回路10は、クロック制御回路11と、モジュール12〜14とを有している。クロック制御回路11は、半導体集積回路10の外部から入力され、他の回路(図示せず)との同期を取るためのシステムクロックsys_CLKおよびモジュール12〜14を動作させるためにそれぞれ供給されるinput信号群およびモジュール12〜14からそれぞれ出力されるoutput信号群に基づいて、モジュール12〜14をそれぞれ所定期間だけ動作させるために必要なクロックCLKを生成し、モジュール12〜14に供給する。すなわち、外部からモジュール12〜14をクロック制御するための専用信号を受け取ることなく、また、モジュール12〜14の内部でクロック制御するためだけの専用回路を設計することなくクロックCLKの制御を行っている。

(もっと読む)

安定したクロック信号を生成させうるクロック信号発生器、該クロック信号発生器を備える半導体メモリ装置及びその方法

【課題】安定したクロック信号を生成させうるクロック信号発生器、該クロック信号発生器を備える半導体メモリ装置及びその方法を提供する。

【解決手段】クロック信号発生器は、クロック信号を発生させるクロック信号発生部と、基準時間の間にクロック信号のパルス数をカウンティングしてカウンティング結果と基準値とを比べて、該比較結果に基づいて制御信号を発生させるクロック信号制御部と、を含み、クロック信号発生部は、制御信号に基づいてクロック信号のパルス数を増減させうる。本発明によれば、温度及び電圧のような環境的要因に関係なく、安定したクロック信号を生成させうる効果がある。

(もっと読む)

通信システム

【課題】マスタの第1のデバイスからスレーブの第2のデバイスに確実且つ容易にアクセスすることである。

【解決手段】バスコントローラFPGA1と、バスコントローラFPGA1と通信接続され、ライトクロック信号WCLKが一線路で順に伝送される複数のローカルFPGA21〜24と、を備え、バスコントローラFPGA1からのライトクロック信号WCLKの線路が最も長いローカルFPGA24は、リードクロック信号RCLKを出力して他のローカルFPGA23〜21を一線路で順に介してバスコントローラFPGA1に伝送し、各ローカルFPGA21〜24は、リードクロック信号RCLKに同期して入力信号を出力してバスコントローラFPGA1へ伝送し、各ローカルFPGA21〜24及びバスコントローラFPGA1の間のリードクロック信号RCLKの線路長と、前記入力信号の線路長とが等しい。

(もっと読む)

半導体装置

【課題】 号伝送速度が高速になるに伴い、データを正常に取り込めるタイミング幅が縮小する為、電源投入時にタイミング調整をしても、周囲環境、例えば、ノイズ等による電源電圧の変化、半導体装置の周囲温度(半導体装置自体の温度も含む)の変化により信号のタイミング変位が生じて正常な信号伝送ができなくなる問題が生じる。

【解決手段】 LSI1の内部に変位量検出回路部7を新たに設け、変位検出回路部内の回路が電源投入後に動的に変化する変位量を出力し、その出力された変化量に基づいてタイミング制御回路が再度タイミングを調整することで、タイミング変位が生じても正常な信号伝送が行なわれるようにする。

(もっと読む)

半導体集積回路装置、データ処理装置及びマイクロコンピュータ

【課題】SDRAMの動作マージンを拡大させて直接にアクセスすることができる半導体集積回路装置を提供する。

【解決手段】中央処理装置、外部に接続されるメモリのインタフェース機能を有する制御回路、中央処理装置に対する第1クロック信号、外部に接続されるSDRAMに供給するための第2クロック信号を含む複数のクロック信号を形成可能なクロック発生回路、SDRAMのクロック端子に対し、第2クロック信号を供給するための第1端子、SDRAMに対するクロックイネーブル信号を出力するための第2端子、及びSDRAMに対し、セレクト信号を出力するための第3端子を有する。制御回路は、SDRAMに対し、第2クロック信号に同期して、第2端子を介して前記クロックイネーブル信号を出力し、第3端子を介してセレクト信号を出力する。

(もっと読む)

クロック供給回路及びクロック供給方法

【課題】クロック信号のシームレスな切り替えが可能なクロック供給回路を提供する。

【解決手段】マルチプレクサ110は、供給された複数のクロック信号のうちクロック指定信号SELにより指定されたクロック信号を第1の中間クロックCLK_M1として出力する。反転回路120は、クロック反転信号INVERTに応答して、供給された第1の中間クロックCLK_M1を、そのまま、又は、信号レベルを反転させて第2の中間クロックCLK_M2として出力する。Dフリップフロップ130、131は、停止信号STOPを第2の中間クロックCLK_M2の立ち上がりエッジ及び立ち下がりエッジに同期させてマスク信号MASKを生成する。ANDゲート140は、第2の中間クロックCLK_M2とマスク信号MASKとから出力クロックCLK_Oを生成し、出力する。

(もっと読む)

通信装置、ベースバンド信号処理装置及び受信処理方法

【課題】入力信号におけるデューティ比の制約を無くし、コストや基板面積や回路設計上の制約を取り払うことができる通信装置、ベースバンド信号処理装置及び受信処理方法を提供する。

【解決手段】VCTCXO16と、VCTCXO16からの第1クロック信号aを分周するクロック分周回路27と、クロック分周回路27から出力された分周クロック信号bが入力され、入力された分周クロック信号bを所定倍して第2クロック信号cを生成するPLL部28と、PLL部28で生成された第2クロック信号cによってベースバンド信号処理を行うベースバンド信号処理部22と、を含む。第1クロック信号aと第2クロック信号cとが同じ周波数となるように生成する。

(もっと読む)

内部クロックドライバ回路

【課題】本発明は、動作周波数の制限なく、ライジングDLLクロックとフォーリングDLLクロックのオーバーラップがない内部クロックドライバ回路を提供する。

【解決手段】本発明に係る内部クロックドライバ回路は、ライジングクロックとフォーリングクロックを遅延させて遅延ライジングクロックと遅延フォーリングクロックを出力する遅延部と、前記ライジングクロック、前記フォーリングクロック、および前記遅延ライジングクロックの入力を受けて組み合わせてライジングDLLクロックを出力するライジングDLLクロック生成部と、前記ライジングクロック、前記フォーリングクロック、および前記遅延フォーリングクロックの入力を受けて組み合わせてフォーリングDLLクロックを出力するフォーリングDLLクロック生成部とを含む。

(もっと読む)

動作モード設定装置、それを含む半導体集積回路および半導体集積回路の制御方法

【課題】クロックの状態変化による誤動作に対する適応性を向上させる動作モード設定装置、それを含む半導体集積回路および半導体集積回路の制御方法を提供する。

【解決手段】本発明の動作モード設定装置は、基準クロックとフィードバッククロックの位相を判別して固定猶予信号を生成する動作モード設定制御部およびリセット信号と前記固定猶予信号の制御によって位相比較信号とパルス信号に応答して固定完了信号を生成する動作モード設定部を含む。

(もっと読む)

半導体集積回路、情報処理システム

【課題】低速クロック信号と高速クロック信号とにより動作する情報処理システムにおいて、高速クロック信号により動作するノーマルモードへの移行時に、高速発振器から高速クロック信号が安定して生成されていることの検知の信頼性を高める。

【解決手段】低速クロック信号の所定クロック周期内に、高速クロック信号がいくつ生成されたかをカウンタでカウントする。低速クロック信号と同期して、カウント値と所定値とを比較し、高速クロック信号の周波数が所定周波数に達しているか判定する。発振が安定するにつれて周波数の変動が小さくなるため、前記判定が複数回にわたって肯定的は判定であると、高速発振器の発振が安定していると検知する。

(もっと読む)

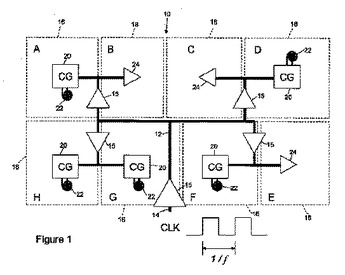

共鳴クロックされたシステムのためのクロック分配ネットワークアーキテクチャ

本明細書に開示されているのは、基準クロックを運ぶための分配ネットワークと、基準クロックによる同期作動のために基準クロックを受信するように分配ネットワークと結合された複数のサーキットドメインと、を含んでいるデジタルシステムである。複数のサーキットドメインの各サーキットドメインは、共鳴クロック信号を発生させるように基準クロックによって駆動されるそれぞれのクロックジェネレータと、共鳴クロック信号に従って作動するためにクロックジェネレータと結合されたそれぞれの回路であって、回路は、共鳴クロック信号のための容量性負荷を含む、回路と、回路の容量性負荷に共鳴するために回路およびクロックジェネレータに結合されたそれぞれのインダクタンスと、を含む。  (もっと読む)

(もっと読む)

DDR−SDRAMへのデータ書き込み回路

【課題】回路内のクロック信号のデューティが崩れた場合でも、製造後にライトデータ信号とデータストローブ信号との位相関係を調整できるDDR−SDRAMへのデータ書き込み回路を提供する。

【解決手段】第1のクロックデューティ制御回路の出力信号のレベルに応じて、2つのデータを切り替えてライトデータ信号を出力するライトデータ信号生成回路と、データストローブマスク信号によって、第2のクロックデューティ制御回路の出力信号の不要な部分をマスクし、データストローブ信号を出力するデータストローブ信号生成回路とを備える。クロックデューティ制御回路は、クロック信号をその立ち上がりおよび立ち下がりで2分周した信号をそれぞれ保持する第1および第2の記憶回路と、第1および第2の記憶回路の出力信号を、それぞれ、第1および第2の一定時間だけ遅延する第1および第2のDLL回路と、両方のDLL回路の出力信号の合成回路とを備える。

(もっと読む)

クロック分配回路およびそれを用いたインターフェース装置

【課題】データの伝送速度および信頼性の低下を防止できるようにしたクロック分配回路およびそれを用いたインターフェース装置を提供する。

【解決手段】入力されたクロックを制御電圧によって可変とされた遅延を有するようにして分配クロックとして出力する電圧制御分配手段、及び前記データと前記分配クロックの位相差を用いて前記制御電圧を生成する制御電圧生成手段を備える。

(もっと読む)

81 - 100 / 265

[ Back to top ]