Fターム[5B079CC01]の内容

計算機・クロック (4,131) | 位相/タイミングの調整 (657) | 調整手段 (364)

Fターム[5B079CC01]の下位に属するFターム

遅延回路を用いるもの (210)

静電容量の調整 (10)

線路長の調整 (7)

シフトレジスタ (28)

遅延量を計測するもの (50)

Fターム[5B079CC01]に分類される特許

21 - 40 / 59

クロック信号発生器

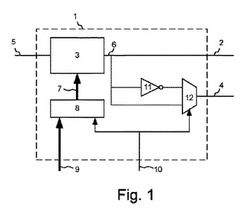

【課題】集積回路のクロック信号を柔軟に発生するためのクロック信号発生器を実現する。

【解決手段】集積回路のクロック信号を発生するためのクロック信号発生器(1)である。クロック信号発生器は、基準クロック信号に基づいて複数の相互に遅延したクロック位相を発生するようになった遅延同期ループ(3)を備える。遅延同期ループはさらに、第1の制御信号に応答して、複数のクロック位相のうち1つを、遅延同期ループ(3)の出力信号として選択するようになっており、この出力信号は第1のクロック信号である。クロック信号発生器はさらに、出力信号の逆を発生するように配置したインバータ(11)と、クロック反転信号に応答して、出力信号かまたは出力信号の逆かのいずれかを第2のクロック信号として転送するように配置したマルチプレクサユニット(12)とを備える。

(もっと読む)

半導体集積回路

【課題】システムクロック信号に同期した分周クロック信号を生成できるクロック供給回路を備えた半導体集積回路を提供する。

【解決手段】システムクロック信号SCKは逓倍部11で逓倍されて逓倍クロック信号XCKが生成され、遅延回路を構成するFF14a〜14dからなるシフトレジスタと、分周回路を構成するFF12に与えられる。リセット信号/RSTは、保持回路を構成するFF13にシステムクロック信号SCKの立ち下りに同期して保持され、信号SAとしてFF14aに与えられる。信号SAは、遅延回路でシステムクロック信号SCKの1/2周期だけ遅延され、分周回路に動作制御信号として与えられる。従って、リセット信号/RSTが“H”となった後、システムクロック信号SCKの立ち上がりの直前に分周回路が動作可能となり、分周クロック信号DCKはシステムクロック信号SCKに同期する。

(もっと読む)

同期型メモリ制御装置及びデータ転送システム

【課題】同期型メモリのデータピンを追加することなく、データとクロック信号との位相差を正確に算出することが可能な同期型メモリ制御装置及びデータ転送システムを提供すること。

【解決手段】データバス接続部28は、同期型メモリに与えられるクロック信号CLKに基づいて、同期型メモリから出力されるデータを受信する。コマンド発生器23は、遅延調整用に、同期型メモリからデータを読み出すためのリードコマンドを、前記データバスが用いられない期間に発生する。遅延計算器22は、リードコマンドに応じて同期型メモリから送信されたデータを、経由するバッファ29の数を選択することにより遅延量を調整したクロック信号CLKに応じて取り込み、取り込んだデータに基づいて遅延量を調整する。

(もっと読む)

数値制御型オシレータ(NCO)出力クロック位相平滑化

【課題】 入力クロックに基づく選択可能周波数において複数個のNCOクロックパルスを発生する形態とされている数値制御型オシレータ(NCO)を包含する位相平滑化回路が記載される。

【解決手段】 該複数個のNCOクロックパルスのエッジは該入力クロックのエッジに整合している。位相エラー計算モジュールが該NCOへ結合されており且つ該複数個のNCOクロックパルスの各々に対する対応する位相エラーを発生する形態とされている。クロック位相選択可能遅延が該位相エラー計算モジュールへ結合されており且つ該選択可能周波数において出力クロックを発生するために該対応する位相エラーに従って該複数個のNCOクロックパルスの各々を調節する形態とされている。

(もっと読む)

クロック切り替え回路

【課題】消費電力を節約する。

【解決手段】N(Nは3以上の整数)ビットの選択信号に基づいて,同じ周波数でそれぞれ位相がずれた2N相の入力クロックから1つを選択して出力クロックとして出力するクロック切り替え回路において,それぞれ,入力される2つのクロックから1つを選択して出力する2N−1個のセレクタを有するセレクタ群と,前記2N−1個のセレクタをアクティブ状態かスリープ状態かに制御する2N−1の動作制御信号を生成する動作制御回路とを有する。前記セレクタは,選択信号によりそれぞれクロックの選択を行う。そして,動作制御回路が,選択信号に基づいて,2N−1個のセレクタのうち一部のセレクタをアクティブ状態に制御し,残りのセレクタをスリープ状態に制御する。

(もっと読む)

メモリ制御装置

【課題】DDR/DDR1/LPDDR SDRAMの動作クロックの切り替わりに応じてデータ・ストローブ信号DQSの位相を好適に調整する。

【解決手段】メモリ・コントローラは、動作周波数レンジの異なる複数のDLLを備え、動作周波数毎にDLLを選択的に使用して動作周波数レンジを切り替えることによって、SDRAMの広い動作クロック範囲に対応する。また、DLLの他に1以上のDLも備え、DLを使用して位相調整を行なうモードと、DLLを使用して位相調整を行なうモードを有し、SDRAMを低速動作で使用するときには、DLLを使用せずにDLモードで動作させて、消費電力を削減する。

(もっと読む)

分相器

【課題】分相器を提供する。

【解決手段】外部クロック信号を入力し、相互180°の位相差を有する第1内部クロック信号及び第2内部クロック信号を発生させる分相器において、外部クロック信号をバッファリングして出力する第1バッファと、外部クロック信号を反転させて出力する反転部と、反転部の出力信号をバッファリングする第2バッファと、外部クロック信号を反転させて出力する第1補間用信号発生部と、反転部の出力信号を反転させて出力する第2補間用信号発生部と、を備え、第1バッファから出力される信号と第2補間用信号発生部から出力される信号とを補間して第1内部クロック信号を発生させ、第2バッファから出力される信号と第1補間用信号発生部から出力される信号とを補間して第2内部クロック信号を発生させることによって、分相器のスキューが最小化される。

(もっと読む)

ジッタ測定回路

【課題】サイクルトゥサイクルジッタのジッタ量を測定できるジッタ測定回路を提供する。

【解決手段】データ保持手段13は、クロック信号に従ってデータラッチを行う。第1の可変論理遅延手段14は、安定化電源で動作し、データ保持手段13の出力を、可変に設定される遅延時間で遅延し、かつ、論理を反転させて、データ保持手段13の入力に戻す。第2の可変論理遅延手段16は、通常電源で動作し、データ保持手段13の出力を、可変に設定される遅延時間で遅延し、かつ、論理を反転させて、データ保持手段13の入力に戻す。ジッタ判定手段19は、データ保持手段13の出力が期待したデータに一致するか否かを判定する。制御部20は、可変論理遅延手段14、16の遅延時間を、データ保持手段13が期待したデータを出力する最大の遅延時間に設定する。

(もっと読む)

高精度クロック・トリガ連続遅延装置

【課題】コントローラから直交変調器に入力する制御信号を連続的に変化させて基準クロックの周期内のまたは周期を超えた連続的な任意の遅延量の設定を行う。

【解決手段】直交変調器(任意の位相遅延を与える回路)と組み合わせたコントローラおよびカウンタを用いて基準クロックに同期したパルス信号に対し任意の遅延時間のパルス信号および遅延クロック信号を高精度で発生させる方法において、コントローラから直交変調器に入力する制御信号を連続的に変化させて基準クロックの周期内のまたは周期を超えた連続的な任意の遅延量を設定して、無限の連続位相変化が可能な特性をもつ直交変調器とカウンタとの組み合わせによる高周波およびトリガ信号の連続遅延を行う。

(もっと読む)

可変分周器および検波器

【課題】可変分周器の出力信号のデューティー比を任意の比率に設定する。

【解決手段】入力クロックを予め設定された分周比で分周した分周クロックを出力する可変分周器であって、入力クロックを分周した内部クロックを出力する分周部と、内部クロックを2分周して分周クロックとして出力する固定分周器と、分周クロックの論理値に応じて第1分周比および第2分周比のいずれかを選択し、分周部が入力クロックを分周する分周比として設定する選択部とを備える可変分周器を提供する。

(もっと読む)

クロックアンドデータリカバリ回路及びSERDES回路

【課題】クロックアンドデータリカバリ回路の動作余裕度の大きさを測定可能とするSERDES回路の提供。

【解決手段】シリアルデータサンプリング回路(101)と、クロックとデータの位相関係を検出する位相比較器(102)と、位相比較結果(UP/DOWN)に基づき位相制御信号を出力する位相制御器(103)と、互いに異なる位相の複数のクロック信号よりなる多相クロックを受け、位相制御信号に基づき位相を補間したクロック信号をデータサンプリング回路(101)に供給する位相補間器(104)とがループを構成する。この位相制御器(103)は、位相制御信号とは別の位相制御信号Aを生成して別の位相補間器(105)に供給し、多相クロックを受け位相制御信号Aに対応して補間したクロック信号に基づき入力データをサンプルする別のデータサンプリング回路(106)を備え、好ましくは、データをサンプルするための閾値レベルが可変に設定される。

(もっと読む)

タイミング調整方法および同期回路

【課題】フリップフロップでセットアップ時間を確保できるようにした同期回路を提供する。

【解決手段】後段のフリップフロップ13でセットアップ時間に余裕があるとき、前段のフリップフロップ12に供給するクロック信号CLK1を組合せ論理回路21の出力データ信号DATA1よりも遅らせる。このために、データ信号DATA1が変化してからクロック信号CLK1が出力するようクロックタイミング調整回路30を設ける。

(もっと読む)

スキュー補正機能を有する回路ブロック

【課題】機能回路(回路ブロック)単位に部分的な同期設計を行い、相互に接続された各機能回路間のスキュー補正を、的確にかつ低消費電力で行い、システム性能の低下を防止するスキュー補正機能を有する回路ブロックを提供する。

【解決手段】本発明の回路ブロックは、データ処理機能毎に分割され、各々が遅延調整して相互接続されて、全体回路を構成する回路ブロックであり、入力される入力データに対し、所定のデータ処理を行う論理回路と、論理回路を初期化するリセット信号が入力されると、設定された期間にわたり、論理回路のリセット状態を保持するリセット調整回路とを有する。

(もっと読む)

クロック信号を生成する電気回路および方法

サンプリング装置(31)のためのクロックサンプリング信号(CLK)を生成するための電気回路(30)は、複数のクロック信号(21〜24、51〜54、61〜64)を生成するためのクロックジェネレータ(1、40、50、60)と、デジタル信号(DS)の特徴的な信号部分(LE)と複数のクロック信号(21、22、23、24、51〜56、61〜64)を相関させる相関装置(L)と、および相関装置(L)による相関に基づいて、クロック信号(21、22、23、24、51〜55、61〜64)のうちの1つを、クロックサンプリング装置のためのクロックサンプリング信号(CLK)として、選択する選択装置(MX)を備える。クロック信号(21〜24、51〜54、61〜64)は、同じサイクル周期(T)を有し、互いに位相シフトする。サンプリング装置(31)は、その後、クロックサンプリング信号(CLK)によってデジタル信号(DS)をサンプリングする。  (もっと読む)

(もっと読む)

半導体集積回路のレイアウト設計方法、装置及びプログラム

【課題】クロックスキューを原因とする誤動作を防止することができると共に容易に実現可能なレイアウト設計方法を提供する。

【解決手段】このレイアウト設計方法は、フリップフロップに対してクロック信号を入力するための第1の端子とクロック信号を出力するための第2の端子が定義されたセルライブラリを用いて、データ出力側のフリップフロップの第2の端子からデータ入力側のフリップフロップの第1の端子に向けてクロック信号が供給されるようにクロック信号配線の接続状態を設定することによりネットリストを作成するステップ(a)と、セルライブラリ及びネットリストに基づいてレイアウトを自動的に作成するステップ(b)と、各フリップフロップの第1及び第2の端子を1つのクロック信号入力端子に置き換えることにより、ステップ(b)において作成されたレイアウトを修正するステップ(c)とを具備する。

(もっと読む)

ラインスキュー最小化装置

【課題】集積度が高くなると、ルーティング金属配線は、より長い距離を引き回され、スキューが大きくなりやすい。本発明は、タイミングの変化が非常に小さい、タイミングスキュー最小化装置を提供する。

【解決手段】4つの位相信号を、4つの位相情報を含む1つの信号に圧縮する。したがって、全ての位相情報を含む信号は、同じラインを介して伝送され、この結果、金属配線の寸法が異なるために生じるスキューの問題を回避することができる。1つの信号が、2つの立ち上がりエッジ及び2つの立ち下がりエッジを有するので、第1及び第2の立ち上がりエッジ及び立ち下がりエッジを選択するイネーブル信号線を用いる。この処理では、クリティカル信号出力は1つのみであり、したがって、信号線は1本でよい。これにより、信号のスキュー及び必要なパワーの両方を削減することができる。

(もっと読む)

クロック信号を発生するクロック発生回路及び方法

【課題】クロック信号を発生するクロック発生回路及び方法を公開する。

【解決手段】クロック発生回路は、外部クロック信号を直接受信して、反転された外部クロック信号を発生するインバータと、一番目のループ回路が反転外部クロック信号を受信してn(nは2以上の定数)個のノードをそれぞれ備え、M−1(Mは1以上の定数)個のループ回路のそれぞれがn個のノードの対応する1つからn個の中間内部クロック信号それぞれを発生し、n個の中間内部クロック信号の周波数が外部クロック信号及び反転外部クロック信号の周波数の倍数であることを特徴とする直列に配列されたM個のループ回路と、それぞれが直列に接続されて以前のループ回路から対応する中間内部クロック信号を受信し、対応する中間内部クロック信号を次のループ回路に出力するM−1個のインバータそれぞれと、を具備するn個のインバータの集合で構成されている。

(もっと読む)

半導体集積回路のクロック構成方法およびそのプログラム

【課題】実際のデバイス上でのクロックスキューの増大を抑制し、オンチップばらつき耐性を強くする。

【解決手段】所定数のフリップ・フロップ(FF)を含む領域G1〜G8を2つの群に群分けする。このとき、境界線の横切るデータ接続経路の数が最小となるようにする。ここでは、データ接続経路A1、A2を横切るようにすると、境界線が横切るデータ接続経路数が2で最小となる。さらに、領域G1〜G4、領域G5〜G8を群分けした後に、クロックツリー合成(CTS)を行う。このようにしてクロック構成を行うことにより、実際のデバイス上でのクロックスキューの増大を抑制し、オンチップばらつき耐性を強くすることができる。

(もっと読む)

位相同期回路

【課題】ジッタを含まない信号を出力できるようにする。

【解決手段】位相同期回路10は、位相比較器14と、電圧制御発振器18と、電圧制御発振器18の出力したクロック信号fVCOを1/n分周して出力する可変分周器20とを備えた同期ループ回路12を有する。また、位相同期回路10は、電圧制御発振器18の出力側に切替え部22を介して接続した帯域フィルタ部24を有する。切替え部22は、電圧制御発振器18の出力するクロック信号fVCOの周波数を切り替えるために可変分周器20に入力する分周比設定信号が切替え信号として入力し、周波数の切替えに同期して帯域フィルタ部24に設けた複数の帯域フィルタを電圧制御発振器18に切り替えて接続する。

(もっと読む)

クロックツリー合成装置、クロックツリー合成方法、制御プログラムおよび可読記録媒体

【課題】複数のクロック信号源と、複数のクロック信号源が各入力端子に接続された論理回路との各クロック出力について、同期関係を解析してクロックツリーを最良に生成する。

【解決手段】複数のクロック信号源と、この複数のクロック信号源が各入力端子に接続された論理回路との各クロック出力について、クロック同期関係解析手段10によって、同期関係を解析し、この解析結果に基づいて、クロックツリー構成手段20によって、クロックツリーを生成するため、クロックツリーを再構成することなく、クロックスキューを低減することができる。また、論理回路からクロックが供給されるクロック同期素子(フリップフロップ)が、どちらの信号源に同期して動作するかが分かるため、クロックスキューが小さく、消費電力が少ないクロックツリーを簡単に構成してタイミング違反による回路誤動作を防ぐことができる。

(もっと読む)

21 - 40 / 59

[ Back to top ]