Fターム[5C006BF25]の内容

液晶表示装置の制御 (150,375) | 機能素子(画素単位回路含まず) (24,965) | 増幅回路(差動増幅、オペアンプ等) (1,336)

Fターム[5C006BF25]に分類される特許

1 - 20 / 1,336

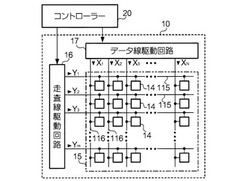

データドライバ、表示パネル駆動装置及び表示装置

電気光学装置、電子機器および駆動方法

【課題】電圧依存性を有する現象により電圧変動が起こる場合に、フリッカーおよび焼き付きを抑制する。

【解決手段】電気光学装置は、共通電極と、画素電極と、一の走査線を選択する走査信号を出力する走査線駆動回路と、走査線駆動回路により選択される一の走査線に対応する画素電極に書き込まれるデータ電圧を示すデータ信号を出力し、データ電圧の極性が、第1フレームにおいて第1極性であり、第1フレームに後続する第2フレームにおいて第1極性と逆の第2極性であるデータ線駆動回路とを有する。ここで、(1)第1フレームの時間長は、第2フレームの時間長に対し所定の割合で長く、(2)データ電圧は、電圧値に応じて補正されており、(3)共通電極の電位は、(1)の条件で(2)により補正された、第1極性のデータ電圧と第2極性のデータ電圧との中心電位と共通電極の電位とのずれが、所定の基準電圧においてゼロになるように調整されている。

(もっと読む)

タッチパネルを備えた液晶表示装置およびその駆動方法

【課題】LCDノイズの影響を低減することにより、誤動作を防止し、操作感を向上させることができるタッチパネルを備えた液晶表示装置およびその駆動方法を得る。

【解決手段】ホストコントローラ50から入力される水平同期信号に同期した水平制御信号を生成するタイミングコントローラ30Aと、LCD10に供給される共通電圧のフィードバック電圧および水平制御信号に基づいて、共通電圧を安定化制御するVcomフィードバック回路60Aとを備え、Vcomフィードバック回路60Aは、フィードバック電圧と所定の参照電圧とを比較するオペアンプと、オペアンプの反転入力端子と出力端子との間に接続された抵抗と、液晶ディスプレイの液晶書き込みに伴って発生するLCDノイズを低減するように、抵抗と協働して、オペアンプの反転入力端子と出力端子との間の抵抗値を調整するVcomフィードバック調整回路61と、を有する。

(もっと読む)

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

電源供給装置、液晶表示装置、およびテレビジョン受像機

【課題】電源オフ時にドライバが正常機能する様に電圧の遮断シーケンスを制御可能な電源制御装置の実現。

【解決手段】第一の電源と、該第一の電源より低い電圧を供給する第二の電源と、降圧回路と、第一及び第二のスイッチ部とを備え、該第二のスイッチ部は該入力電圧又は該第一の電源の出力電圧が所定の電圧以下になるとオフに、該第一のスイッチ部は該第二のスイッチ部がオフになるとオンになる。

(もっと読む)

半導体装置

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

液晶表示装置

【課題】液晶表示装置において、共通電圧の電位変動をキャンセルし、液晶表示パネルに表示する画面の画質が劣化するのを防止し、高品位の画像を提供する。

【解決手段】各画素が、画素電極と、対向電極とを有し、1表示ライン上の互いに隣接する2つの画素を画素Aと画素Bとするとき、映像電圧の書き込み時に、前記画素Aの前記画素電極に対して前記対向電極に供給される前記共通電圧よりも高電位の映像電圧を印加し、前記画素Bの前記画素電極に対して前記対向電極に供給される前記共通電圧よりも低電位の映像電圧を印加する液晶表示装置であって、前記対向電極の複数箇所の電位変動を検出し、前記共通電圧生成回路にフィードバックするフィードバック手段を有し、前記共通電圧生成回路は、前記フィードバック手段によりフィードバックされた電位変動に基づき、基準共通電圧に電位変動を相殺する逆補正電圧を重畳した共通電圧を前記対向電極に対して供給する。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし面積も抑制可能とする出力回路の提供。

【解決手段】出力回路は、差動入力段10と出力増幅段20と増幅加速回路70を備え、増幅加速回路70は、入力対が入力端子1と出力端子2に夫々接続された差動対171、172と、第5の電源端子E5と前記差動対の出力対間にそれぞれ接続された負荷素子対174、175を備え、差動対171、172の入力電位差によって、差動入力段10の第2のカレントミラー40の入力が接続する第4のノードN4への電流供給を制御する第1の電流源回路176と、差動入力段10の第1のカレントミラー30の出力が接続する第1のノードN1への電流供給を制御する第2の電流源回路178を含む。

(もっと読む)

液晶表示装置の駆動回路

【課題】入出力間オフセット電圧を削減しつつ消費電流を削減する。

【解決手段】第1導電型の第1差動回路は、第1入力信号と出力信号とを差動入力信号とする。第1導電型の第2差動回路は、第2入力信号と出力信号とを差動入力信号とする。第2導電型の第3差動回路は、第1入力信号と出力信号とを差動入力信号とする。第2導電型の第4差動回路は、第2入力信号と出力信号とを差動入力信号とする。出力段回路は、第1乃至第4差動回路の出力に基づいて出力信号を出力する。差動増幅器は、上記第1乃至第4差動回路、出力段回路を具備し、制御信号に基づいて、第1乃至第4差動回路を形成するトランジスタのチャネル長とチャネル幅との比を変更する。

(もっと読む)

階調電圧生成回路、画像表示装置及びプロジェクター

【課題】コストを低減し、後段の回路等に対するダメージを防ぐことが可能な階調電圧生成回路、画像表示装置及びプロジェクターを提供する。

【解決手段】インピーダンス変換部56と階調電圧生成部52とを結ぶ配線L1〜L9には、接地電圧との間に、基準電圧Vref1〜Vref9を安定させるためのコンデンサーC1〜C9が接続されている。また、両端の演算増幅器A1,A9と階調電圧生成部52とを結ぶ配線L1,L9には、演算増幅器A1,A9とコンデンサーC1,C9との間に、所定の抵抗値を有する抵抗器R1,R9が配置されている。つまり、演算増幅器A1,A9の出力端子と、階調電圧生成部52の第2の分圧部57とは、抵抗器R1,R9を介して接続されている。この抵抗器R1,R9は、起動時に、第2の分圧部57に供給される基準電圧Vref1,Vref9の立ち上がりを遅くする作用を有している。

(もっと読む)

液晶表示装置の駆動装置

【課題】オフセットの影響、回路規模の増大、フリッカ等を抑制し、画質の向上に好適なドライバの提供。

【解決手段】切換制御信号が第1の論理値のとき、第1、第3の電圧が第1、第3の差動段に、第2、第4の電圧が第2、第4の差動段に入力され、第1、第3の差動段の出力が第1、第3の出力段の入力に、第2、第4の差動段の出力が第2、第4の出力段の入力にそれぞれ接続され、ガンマ抵抗1両端には第1、第2の電圧が、ガンマ抵抗2両端には第3、第4の電圧が印加され、切換制御信号が第2の論理値のとき、第1、第3の電圧が第3、第1の差動段に、第2、第4の電圧が第4、第2の差動段に入力され、第3、第1の差動段の出力が第1、第3の出力段の入力に、第4、第2の差動段の出力が第2、第4の出力段の入力にそれぞれ接続され、ガンマ抵抗1両端には第1、第2の電圧が、ガンマ抵抗2両端には第3、第4の電圧が印加される。

(もっと読む)

半導体装置

【課題】単極性のTFTを用いて構成するデジタル型式の表示装置において、消費電流を低減することの出来る回路を提供する。

【解決手段】デジタル映像信号の保持を行うラッチ回路であって、TFT101の入力電極にデジタル映像信号が入力されると、TFT101の出力電極からは非反転出力信号が出力され、TFT102およびTFT103の出力電極からは反転出力信号が出力されるラッチ回路を提供する。出力を非反転、反転の2系統得られるため、後段のバッファを駆動する際に、電源間の直流パスが生ずる期間を短くすることが出来、消費電流の低減に寄与する。

(もっと読む)

半導体装置

【課題】液晶等の電気光学素子若しくは発光素子等を表示媒体として用いる表示装置及びその駆動方法を提供する。

【解決手段】劣化しやすいトランジスタのゲート電極に、オンしたトランジスタを介して信号を入力することで、劣化しやすいトランジスタのしきい値電圧のシフト及びオンしたトランジスタのしきい値電圧のシフトを抑制する。すなわち、高電位(VDD)がゲート電極に印加されているトランジスタを介して(若しくは抵抗成分を持つ素子を介して)、交流パルスを劣化しやすいトランジスタのゲート電極に加える構成を含んでいる。

(もっと読む)

表示装置

【課題】 電位変動の影響を受けた画素による表示品質の低下を抑制できる表示装置を提供する。

【解決手段】 複数の画素Pが複数のソースラインSLと複数のゲートラインGLの交差部の夫々に対応配置され、同じソースライングループGに属するソースラインSLの夫々がスイッチ素子SWを介して基幹ソースラインSOに接続し、ゲートラインGLの1つが選択されている1つの連続した選択期間内において、同じソースライングループGに属するソースラインSLを所定の選択順序で順次選択して、基幹ソースラインSOを介して駆動電圧を印加する電圧印加処理を実行する駆動処理を実行するように構成され、選択順序を変更するタイミングを規定したタイミングルールと、選択順序の変更方法を規定した順序ルールを含む変更ルールに基づいて、駆動処理におけるソースラインの選択順序を変更する。

(もっと読む)

半導体装置、表示装置、液晶表示装置、表示モジュール及び電子機器

【課題】非選択期間において、出力信号のノイズが小さく、且つトランジスタの特性劣化を抑制できる液晶表示装置の駆動回路を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、第3のトランジスタ及び第4のトランジスタを設け、第1のトランジスタにおいて、第1端子を第1の配線に接続し、第2端子を第2のトランジスタのゲート端子に接続し、ゲート端子を第5の配線に接続し、第2のトランジスタにおいて第1端子を第3の配線に接続し、第2端子を第6の配線に接続し、第3のトランジスタにおいて第1端子を第2の配線に接続し、第2端子を第2のトランジスタのゲート端子に接続し、ゲート端子を第4の配線に接続し、第4のトランジスタにおいて第1端子を第2の配線に接続し、第2端子を第6の配線に接続し、ゲート端子を第4の配線に接続する。

(もっと読む)

表示装置

【課題】手間やコストの増大を招くことなく、発光ダイオードの順方向電圧のバラツキに起因して発光ダイオードの光量にバラツキが生じるのを防止する。

【解決手段】表示装置は、表示パネル2と、表示パネル2を背面から照明するバックライト部3と、を備える。バックライト部3は、それぞれM個の発光ダイオードが直列接続された発光ダイオードストリングS11,S12が、2個互いに並列接続された発光ダイオードストリング群と、発光ダイオードストリング群に直列接続され、直流電圧を生成する電源部31と、発光ダイオードストリング群及び電源部31に直列接続され、発光ダイオードストリング群に電流を供給する駆動部32と、発光ダイオードストリングS11,S12に流れる各電流を調整する電流調整部33と、を含む。

(もっと読む)

表示装置

【課題】小型化が可能で、回路面積が小さく、低消費電力で、メモリ部の動作の信頼度が高く、低コストである表示装置を提供する。

【解決手段】容量を有するデータ保持回路3と、複数の画素を有する表示部4とが第1の支持基板1上に形成された表示装置において、画素には、それぞれ画素電極が設けられ、第1の支持基板1と対向する第2の支持基板2が設けられており、第2の支持基板2における第1の支持基板1側の面には、データ保持回路3に対向する領域に、導電体膜8が存在せず、第2の支持基板2における第1の支持基板1と反対側の面には、データ保持回路3に対向する領域に、導電体膜8が存在する。

(もっと読む)

コレステリック液晶を含む表示素子の駆動方法およびコレステリック液晶表示装置

【課題】温度が変化しても安定した表示が行えるコレステリック液晶の駆動方法およびコレステリック液晶表示装置の実現。

【解決手段】コレステリック液晶表示素子10と、表示素子を駆動するセグメントドライバおよびコモンドライバ28,29と、セグメントドライバおよびコモンドライバに供給する電源を生成する多電源生成回路23と、温度センサ30と、制御回路27と、を有し、制御回路は、リセット期間、スイッチング期間および維持期間を有するダイナミック駆動シーケンスを行なうように制御し、維持期間におけるコレステリック液晶への印加電圧を温度に応じて変化させるコレステリック液晶表示装置。

(もっと読む)

液晶表示装置

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能

な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフト

レジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は

、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において

常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また

、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供

給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制で

きる。

(もっと読む)

1 - 20 / 1,336

[ Back to top ]