Fターム[5E070CB13]の内容

通信用コイル・変成器 (13,001) | コイル−プリントコイル(基板に印刷するもの) (2,690) | インダクタンス、トランスの形成 (1,197) | パターンの積層(積層コイル) (702)

Fターム[5E070CB13]に分類される特許

201 - 220 / 702

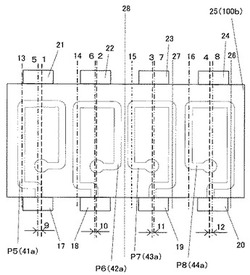

積層型誘電体フィルタ

【課題】 各インダクタ素子の経路長ずれを抑制し、減衰特性を等しくする。

【解決手段】 複数の誘電体層25(100b)が積層されて誘電体層間にインダクタ素子を構成する複数のインダクタパターンP5〜P8が形成されており、1つの側面にインダクタ素子の一方の端部が露出している積層体と、積層体の側面に積層方向に帯状に等間隔で形成された端子電極17〜20とを具備し、インダクタパターンP5〜P8は等間隔に並んで形成され、インダクタパターン中心線1〜4と端子電極中心線5〜8とのずれ量9〜12が誘電体層中心線28から遠いインダクタパターンP5〜P8におけるほど大きく、インダクタパターンP5〜P8は誘電体層中心線28を対称軸として線対称のパターンである積層型誘電体フィルタである。各インダクタ素子の経路長のずれを抑制することが可能となるので、各インダクタ素子の減衰特性のずれを抑制することが可能となる。

(もっと読む)

電子部品及びその製造方法

【課題】特性ばらつきの発生を抑制できる電子部品及びその製造方法を提供する。

【解決手段】積層体12aは、絶縁体層16a〜16mが積層されてなる。コイルLは、絶縁体層16e〜16i上に設けられているコイル導体18a〜18eにより構成されている。引き出し導体20aは、絶縁体層16d上に設けられ、コイルLに対して電気的に接続され、かつ、外部電極に接続されている。引き出し導体20bは、絶縁体層16j上に設けられ、コイルLに対して電気的に接続され、かつ、外部電極に接続されている。引き出し導体22aは、絶縁体層16d上に設けられ、かつ、z軸方向から平面視したときに、引き出し導体20bと一致した状態で重なっている。引き出し導体22bは、絶縁体層16j上に設けられ、かつ、z軸方向から平面視したときに、引き出し導体20aと一致した状態で重なっている。

(もっと読む)

電子部品の製造方法

【課題】焼成後の積層体の上面又は下面に凹凸が発生することを低減できる電子部品の製造方法を提供する。

【解決手段】絶縁体層19のそれぞれの主面上に、z軸方向から平面視したときに環状の領域において螺旋状のコイルLの一部となるコイル導体18を形成する。絶縁体層19上であって、コイル導体18が形成された領域以外の領域に、絶縁体層17を形成する。z軸方向から平面視したときに、絶縁体層15の主面上において環状の領域と重なる領域R1以外の領域R2に、絶縁体層16を形成する。絶縁体層15が絶縁体層16よりもz軸方向の正方向側及び負方向側に積層されるように、絶縁体層15及び絶縁体層16を積層して積層体12を得る。積層体12を焼成する。

(もっと読む)

電子部品及びその製造方法

【課題】コイルの断線の発生を低減できる電子部品及びその製造方法を提供する。

【解決手段】複数のコイル導体層18がビアホール導体b1〜b6により接続されてなるコイルを備えている電子部品の製造方法。複数の絶縁体層19を準備する。絶縁体層19にビアホール導体b1〜b6を形成する。絶縁体層19bの主面上に、z軸方向の正方向側に積層される絶縁体層19aに形成されたビアホール導体b1が接続される接続位置P1の周囲の少なくとも一部において、接続位置P1よりもz軸方向の正方向側に突出する壁部Wを有するコイル導体層18bを形成する。絶縁体層19b上であって、コイル導体層18bが形成された領域以外の領域に、x軸方向の正方向側に向かう方向に絶縁ペーストをスクリーン印刷により塗布していく。絶縁体層19を積層して積層体を得る。

(もっと読む)

電子部品及びDC/DCコンバータ

【課題】低温で焼結可能であり、2MHz以上の高周波数でも低損失であり、応力下でも広い温度範囲で特性変動が少ない低損失フェライトを用いた電子部品及びそれを備えたDC/DCコンバータを提供する。

【解決手段】磁心と、磁心に導線を巻線したコイルとを有する電子部品であって、磁心は47.1〜49.3mol%のFe2O3、20〜26mol%のZnO、6〜14mol%のCuO、及び残部NiOからなる主成分100質量%に対して、副成分としてSnO2換算で0.1〜2質量%のSnと、Mn3O4換算で0.05〜1.1質量%のMnとを含み、平均結晶粒径が0.5〜3μmである低損失フェライトで構成されたことを特徴とする電子部品。

(もっと読む)

電子部品及びその製造方法

【課題】製造工程を簡素化できる電子部品及びその製造方法を提供する。

【解決手段】積層体12は、磁性体からなる絶縁体層16、及び、非磁性体からなる絶縁体層18が積層されてなる。コイルLは、積層体12内において、複数のコイル導体20が複数のビアホール導体b1〜b13により接続されることにより構成されている螺旋状のコイルであって、z軸方向から平面視したときに、絶縁体層18と重なっている。全ての絶縁体層18は、z軸方向から平面視したときに、z軸方向においてコイルLが形成している軌道R及び軌道Rの外側に設けられていると共に、ビアホール導体b1〜b13と重なっていない。

(もっと読む)

複合電子部品

【課題】静電容量が小さく且つ放電特性、耐熱性及び耐候性に優れた静電気対策素子とコモンモードフィルタとを組み合わせて構成された小型で高性能な複合電子部品を提供する。

【解決手段】複合電子部品100は、第1及び第2の磁性基体11a、11bに挟まれたコモンモードフィルタ層12a及び静電気対策素子層12bを備え、静電気対策素子層12bは、下地絶縁層27の表面に形成されたギャップ電極28〜31と、ギャップ電極28〜31を覆う静電気吸収層33とを備えている。ギャップ28G〜31Gは、スパイラル導体17,18の最外周よりも外側に配置されている。磁性コア36は磁性粉及びカーボンを含有する樹脂からなり、ギャップ電極28〜31の上方を覆う保護層として機能する。静電気吸収層33は低電圧放電タイプの静電気保護材料として機能し、静電気などの過電圧が印加された際に静電気吸収層33を介して電極間で初期放電が確保される。

(もっと読む)

電子部品

【課題】低背化を図ることができる電子部品を提供する。

【解決手段】積層体12は、絶縁体層15,16、及び、絶縁体層15,16よりも低い透磁率を有している1層の絶縁体層17が積層されてなる。コイルLは、積層体12に内蔵されている複数のコイル導体18が電気的に接続されて構成され、かつ、z軸方向に平行なコイル軸を有する。絶縁体層17は、z軸方向の最も負方向側に設けられているコイル導体18iに対してz軸方向の負方向側から接触している。積層体12において、領域A3のz軸方向の厚みD3は、領域A2のz軸方向の厚みD2より小さい。

(もっと読む)

積層インダクタ

【課題】1ターンの長さで周回するコイル電極により構成されているコイルを内蔵する積層インダクタの構成を用いて、磁束の回らない領域の内側に引出ビアホールを形成することで、コイル電極の形成面積を大きくとり、その結果インダクタンス及び直流重畳特性の良い積層インダクタを提供する。

【解決手段】本発明に係る積層インダクタは、複数の絶縁体層からなる積層体と、1ターンの長さで周回しているコイル電極からなる螺旋状のコイルと、前記螺旋状のコイルの両端に接続されるとともに、前記積層体の底面に形成されている外部電極を備える。前記螺旋状のコイルと前記外部電極は、1ターンの長さで周回するコイル電極において、磁束の回らないスペースに形成された引出ビアホールによって接続されている。

(もっと読む)

電子部品

【課題】直流重畳特性をより向上させることができる電子部品を提供する。

【解決手段】積層体は、複数の絶縁体層16が積層されてなる。コイルLは、絶縁体層16上に設けられているコイル導体層18により構成されている。複数のコイル導体層18は、互いに接続されることにより、螺旋状のコイルLを構成し、かつ、z軸方向から平面視したときに、一つの環状の軌道を形成しているコイル導体層であって、線幅W1と該線幅W1よりも太い線幅W2とに一定周期Tで変化する形状をなしている。複数のコイル導体層18の外縁は、軌道の内周及び外周において一致した状態で重なり合っている。

(もっと読む)

積層型コモンモードフィルタ

【課題】磁束のロスを低減すると共に、信頼性を向上させることができる積層型コモンモードフィルタを提供する。

【解決手段】第一コイル導体31及び第二コイル導体34の辺部同士が交わる頂部において、内縁側の角部の周長を外縁側の角部よりも大きくする。従って、頂部同士の間のスペース幅を狭くして、辺部同士の間のスペース幅に近づけることが可能となり、これによって、磁束のロスを低減することができる。また、例えば、コイル導体の厚みを厚くして、厚みがコイル導体の導体幅よりも大きくなった場合は、積層時にシートを支えきれずに導体の倒れや潰れが発生する可能性があるが、内縁側の角部の周長を外縁側の角部よりも大きくして、頂部における導体の幅を大きくすることで、積層時にシートを確実に支え、導体の倒れや潰れを防止する。

(もっと読む)

コイル部品及びその製造方法

【課題】所望のフィルタ性能を確保しつつ、小型化且つ低背化され、低コストで製造可能なコイル部品を提供する。

【解決手段】コイル部品100は、磁性セラミック材料からなる磁性基板11と、磁性基板11の一方の主面に形成されたコイル導体を含む薄膜コイル層12と、薄膜コイル層12の主面にめっきにより形成された肉厚なバンプ電極13a〜13dと、バンプ電極13a〜13dの形成位置を除いた薄膜コイル層12の主面に形成された磁性樹脂層14とを備えている。バンプ電極13a〜13dの厚さは磁性樹脂層14の厚さと同等かそれ以上である。バンプ電極13a〜13dは、薄膜コイル層12内のコイル導体と平面視にて重なる部分を有している。

(もっと読む)

多次元微細構造の製造

データ記憶装置のデータ変換器に使用するための三次元(3D)微細構造コイルを含むがこれに限定されない、多次元微細構造を形成するための方法を提供する。いくつかの実施例に従って、本方法は概して、第1の誘電材料に埋込まれた第1の導電性経路を有するベース領域を設けるステップと、各々が、埋込まれた第1の導電性経路に接触する第1のシード層で部分的に充填された複数のビア領域を、第1の誘電材料にエッチングするステップと、複数のビア領域の各々に導電性支柱を形成するように第1のシード層を使用するステップとを含み、各導電性支柱は、ベース領域の上方の第1の距離まで延在する実質的に垂直の側壁を有する。  (もっと読む)

(もっと読む)

電子部品

【課題】大きなインダクタンス値を得ることができ、かつ、抵抗値のばらつきを低減できる電子部品を提供する。

【解決手段】コイルは、z軸方向から平面視したときに、互いに重なり合って環状の軌道Rを形成している。軌道Rは、絶縁体層16aの対角線C1,C2の交点Pを通過し、かつ、絶縁体層16aの短辺に平行な直線L1によって、軌道R1と軌道R2とに区分されている。軌道R1が直線L1に対して線対称に移動することにより得られる軌道を軌道R3とした場合に、軌道R2の一部分(軌道r2)は、軌道R3の一部分(r3)に重なっており、軌道R2の残余の部分(軌道r4)は、軌道R3の残余の部分(軌道r5)よりも交点Pの近くに位置している。ビアホール導体V1は、軌道r4と軌道r5とにより形成される領域Eに設けられている。

(もっと読む)

積層複合フィルタ

【課題】実装面積が小さく、実装コストを低減でき、インダクタンス特性を向上させ、残留インダクタンスを低減でき、コモンモードノイズに対し、除去能力を設計する。

【解決手段】コモンモードチョークコイル10を有するコイル部1aと2つの線対地コンデンサ13,14を有するコンデンサ部1bを備えた積層複合フィルタにおいて、コイル部は、電極パターン4a〜4c,5a〜5cが形成された複数のシート6a〜6dを積層し、電極パターンを接続することにより構成され、コンデンサ部は、コイル部とワンチップ化され、電極パターン11a〜11cが形成された複数のシート12a〜12cを積層して構成される。

(もっと読む)

インダクタ部品

【課題】信号の反射成分を抑制することのできるインダクタ部品を提供する。

【解決手段】信号系の回路に挿入されるインダクタ部品であって、インダクタを構成する導体である巻線30は、回路における導体よりも高い抵抗値を有する導体材料を含む。インダクタを構成する導体である巻線30が、回路における導体よりも高い抵抗値を有する導体材料を含んでいるため、インダクタには抵抗成分が分布定数的に配置されることとなり、信号の反射成分を抑制することが可能となる。また、導体幅や長さなどを調整しなくとも特性インピーダンスを調整することができ、あるいは最小限の導体幅や長さなどの調整で特性インピーダンスの調整を行うことができる。

(もっと読む)

コイル装置アレイ

【課題】 外的な要因によってクラックが生じても、その影響を低減して電気的特性および信頼性の劣化を防止する。

【解決手段】 積層体で構成されるとともに、複数のコイル装置を備えたコイル装置アレイにおいて、

複数のコイル装置のうち隣接されているコイル装置の間であって、隣接されているコイル装置のコイル素子の間に、スリットが設けられている。

【効果】

外部からの機械的、熱的な衝撃や応力がコイル装置アレイに加わった場合、積層体内のスリットを形成した付近に応力が集中し、スリットの近傍にクラックを発生しやすくすることができる。このため、個々のコイル装置の電気的特性および信頼性の劣化を防止できる。

(もっと読む)

電子部品

【課題】厚膜導電材料を使用して導体パターンを形成した場合であっても、設計自由度の低下を招くことなく、主導体部にうねりや断線が発生するのを回避することが可能な信頼性に優れた電子部品を実現する。

【解決手段】第7の層間絶縁層5gの表面にはコイル状に巻回された幅寸法W′の第6の主導体部7fが形成されると共に、該第7の層間絶縁層5gの一端部には第6の主導体部7fの幅寸法W′よりも大きな幅寸法Wを有する引出導体部9aが形成されている。引出導体部9aと第6の主導体部7fとは、内縁が曲げ半径Rを有する円弧状に形成された接続部10aにより、引出導体部9aから第6の主導体部7fに架けて徐々に細くなるように接続されている。第6の主導体部7fの端部には、該第6の主導体部7fよりも幅広に形成された長方形状の応力緩衝部11aが形成されている。

(もっと読む)

バラン実装デバイス

【課題】伝送線路バランのインピーダンスを整合することが可能なバラン実装デバイスを提供する。

【解決手段】一端が平衡信号出入力端30a,35aであり、他端が接地端30b,35bであり、電気的に独立して設けられた2つの平衡信号伝送路30,35と、一端が不平衡信号入出力端50aであり、他端が開放端50bである不平衡信号伝送路50とが、誘電体層24を介して対向してなる積層型バランを備えたバラン実装デバイスにおいて、一端が不平衡信号入出力端50aに導通され、他端が積層型バランに対して不平衡信号を入出力するための不平衡信号入出力端子部59に導通され、不平衡信号伝送路50の不平衡信号入出力端50aを有する側の平面スパイラル部50dの中心スペース部E2に配置されたインダクタ120を不平衡信号伝送路50と直列接続する。

(もっと読む)

磁性体セラミック、セラミック電子部品、及びセラミック電子部品の製造方法

【課題】磁気損失が小さく、安価なCuと同時焼成することが可能な高周波用の磁性体セラミック、該磁性体セラミックを使用した非可逆回路部品等のセラミック電子部品、及び該セラミック電子部品の製造方法を実現する。

【解決手段】主成分が、ビスマスを含まないガーネット型フェライト系材料で形成されると共に、Cu酸化物が0.25〜2.50重量%の範囲で含有され、かつ、酸素分圧が1.0×100〜1.0×10−3Paの雰囲気で焼成されてなり、強磁性共鳴半値幅ΔHが4000A/m以下の磁性体セラミックを得る。磁性体セラミックと前記導電部とが同時焼成されてなり、同時焼成後の降温過程中で500℃〜700℃になった時点で、F2O3−Fe3O4の平衡酸素分圧以上であってかつCu−Cu2Oの平衡酸素分圧以下の酸素分圧で熱処理する。

(もっと読む)

201 - 220 / 702

[ Back to top ]