Fターム[5E070CB13]の内容

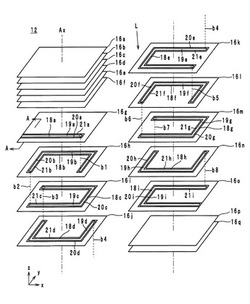

通信用コイル・変成器 (13,001) | コイル−プリントコイル(基板に印刷するもの) (2,690) | インダクタンス、トランスの形成 (1,197) | パターンの積層(積層コイル) (702)

Fターム[5E070CB13]に分類される特許

161 - 180 / 702

電子部品及びその製造方法

【課題】本発明の目的は、コイルのインピーダンスの低下を抑制できる電子部品及びその製造方法を提供することである。

【解決手段】積層体12は、複数の絶縁体層16が積層されて構成されている。コイルLは、絶縁体層16上に設けられているコイル導体18により構成されている。コイル導体18は、コイル導体18の延在方向に直交する断面において、z軸方向に直交する方向に並んでいる領域19,20を有している。領域19と、コイル導体18のz軸方向に隣接する絶縁体層16との間には、空隙が存在する。領域20と、コイル導体18のz軸方向に隣接する絶縁体層16との間には、空隙が存在しない。

(もっと読む)

電子部品及びその製造方法

【課題】本発明の目的は、渦電流の発生を抑制できる電子部品およびその製造方法を提供することである。

【解決手段】積層体12は、複数の絶縁体層16が積層されてなる。コイルLは、積層体12に内蔵され、かつ、z軸方向に沿って延在するコイル軸Axを有する。接続導体17は、絶縁体層16上に設けられ、かつ、コイルLの両端に対して電気的に接続されている。接続導体17は、絶縁体層16間から積層体12の外部に露出することにより外部電極として機能する。接続導体17には、z軸方向から平面視したときに、コイルLにより囲まれている領域の少なくとも一部と重なるように、導体が存在しない空白部B1〜B6が設けられている。積層体12の端面S1,S2には、導体が設けられていない。

(もっと読む)

電子部品及びその製造方法

【課題】本発明の目的は、コイルの直流抵抗を低減することができる電子部品及びその製造方法を提供することである。

【解決手段】積層体12は、絶縁体層16と絶縁体層16よりも高い空孔率を有する絶縁体層17とが積層されてなる。コイルLは、積層体12に内蔵され、コイル導体18,19を含んでいる。コイル導体18は、絶縁体層16上に設けられている。コイル導体19は、コイル導体18が設けられている絶縁体層16上に積層されている絶縁体層17上に設けられ、かつ、絶縁体層17に設けられている無数の空孔に入り込んだ導体を介してコイル導体18に対して接続されている。

(もっと読む)

複合部品

【課題】インダクタ部と静電気対策部とを備えながら、インダクタ部の性能の低下を低減する複合部品を得ることを目的としている。

【解決手段】本発明は、下部積層部25と、インダクタ部26と、上部積層部27とを備え、インダクタ部26を構成する第1、第2のコイル16、18の軸は積層方向に一致し、下部積層部25は、一対の電極間に通常は絶縁体として機能し所定以上の電圧が印加されると通電する下部静電気通過部12を有し、上部積層部27は、一対の電極間に通常は絶縁体として機能し所定以上の電圧が印加されると通電する上部静電気通過部23を有し、下部静電気通過部12と上部静電気通過部23は積層方向から透視した際に同じ位置に形成されたものである。

(もっと読む)

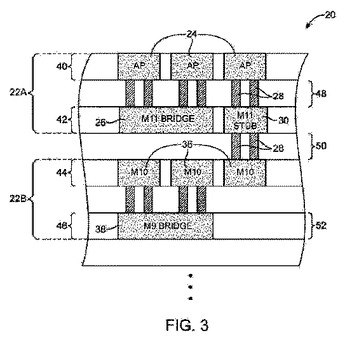

直列接続のインダクターを有する集積回路

集積回路インダクターは、直列に接続されている上部ループ形状のライン部分と下部ループ形状のライン部分とを有し得る。上部部分および下部部分は、45°曲がりを有し得、6角形または8角形のループを形成する。各ループ部分は、1つ以上のターンを有し得る。金属ルーティング層の介在する金属フリー領域が、容量性カップリングを低減させるために、2つの層の間に形成され得る。各ループ部分は、ビアによって並列にショートされた2つ以上の金属ラインのセットを有し得る。上部ループおよび下部ループは、容量性カップリングを低減させるために、横にオフセットされ、または入れ子にされ得る。  (もっと読む)

(もっと読む)

複合電子部品の製造方法

【課題】静電容量が小さく且つ放電特性、耐熱性及び耐候性に優れた静電気対策素子とコモンモードフィルタとを組み合わせて構成された小型で高性能な複合電子部品の製造方法を提供する。

【解決手段】複合電子部品の製造方法は、第1及び第2の磁性基体11a、11bの間に静電気対策素子層12b及びコモンモードフィルタ層12aを形成する工程を備え、静電気対策素子層12bを形成する工程は、下地絶縁層27を形成する工程と、下地絶縁層27の表面においてギャップを介して相互に対向位置された電極を形成する工程と、少なくとも電極間に静電気吸収層30を形成する工程を含む。静電気吸収層30は、絶縁性無機材料のマトリックス中に導電性無機材料が不連続に分散したコンポジットであって、電極が形成された下地絶縁層の表面に島状に点在した導電性無機材料の層と、導電性無機材料を覆う絶縁性無機材料の層との積層構造である。

(もっと読む)

電子部品

【課題】本発明の目的は、内蔵される回路素子を大きく形成することができると共に、ショートの発生を防止するための絶縁体膜が積層体から容易に剥離することを抑制できる電子部品を提供することである。

【解決手段】積層体12は、複数の絶縁体層が積層されてなり、z軸方向において互いに対向している上面S1及び下面S2、並びに、該上面S1と該下面S2とを接続している側面S3〜S6を有している。絶縁体膜20は、側面S3〜S6に設けられている。コイルLは、積層体12に内蔵され、かつ、該積層体12の側面から絶縁体膜20に対して突出している突出部19を有している。

(もっと読む)

電子部品及びその製造方法

【課題】本発明の目的は、内蔵される回路素子を大きく形成することができると共に、簡単な製造工程により製造できる電子部品及びその製造方法を提供することである。

【解決手段】積層体12は、複数の絶縁体層が積層されてなる。コイルLは、積層体12に内蔵され、かつ、絶縁体層間から積層体12の側面から外部に露出している露出部19を有している。金属膜20は、露出部19を覆うように積層体12の側面に設けられている。金属膜20の表面24は、酸化されることにより絶縁性を有している。

(もっと読む)

電子部品及びその製造方法

【課題】本発明の目的は、内蔵される回路素子を大きく形成することができると共に、簡単な製造工程により製造できる電子部品及びその製造方法を提供することである。

【解決手段】積層体12は、複数の絶縁体層が積層されてなる。コイルLは、積層体12に内蔵され、かつ、絶縁体層間から積層体12の側面から外部に露出している露出部19を有している。フェライト膜20は、露出部19を覆うように積層体12の側面に設けられている。

(もっと読む)

積層セラミック部品

本発明に係る積層セラミック部品は,接続端子(1a,1b)が設けられた基体(10)と,インダクタンス領域のため,内部に導体から構成されたインダクタンス(12)が配置されたフェライトセラミック(2)と,基体(10)の内部に配置されたバリスタセラミック(4)とを含む。バリスタセラミック(4)は,基体(10)の体積に対して最大でも40%を超えない体積を有する。 (もっと読む)

半導体装置

【課題】 2巻きの渦巻き状であって1箇所において立体的に交差する薄膜インダクタ素子を備え、該薄膜インダクタ素子の両端部側から見たときの特性がほぼ均等となるようにする。

【解決手段】 薄膜インダクタ素子13は、絶縁膜上に1箇所が欠けた環状に設けられた外側上層配線14と、絶縁膜上において外側上層配線14の内側に同一側の1箇所が欠けた環状に設けられた内側上層配線15と、絶縁膜下に外側上層配線14の一端部及び内側上層配線15の一端部に接続されて設けられた下層配線16とを有する。この場合、外側上層配線14の長さと内側上層配線15の長さは同じかほぼ同一で、その差が小さいので、薄膜インダクタ素子13の両端部側から見たときの特性をほぼ均等とすることができる。

(もっと読む)

デジタルCMOS工程において周波数合成器に用いられるソレノイドインダクタ

本発明のデジタルCMOS工程で周波数合成器に用いられるソレノイドインダクタは、所定の幅を有し、両側が垂直方向に積層され、ソレノイド構造を有する多数の配線金属と、両側に積層された多数の配線金属の相互間を連結する配線金属連結部とを備え、両側に積層された多数の配線金属のうち、所定数の下位層配線金属と、下位層配線金属の相互間を連結する配線金属連結部とがそれぞれ連結され重なる。本発明によると、デジタルCMOS工程で4〜5GHz以上の周波数帯域で動作する周波数合成器を具現するためにソレノイドインダクタを用いることで、RF CMOS工程でのみ具現可能な数GHz帯域の周波数合成器を具現することができる効果がある。  (もっと読む)

(もっと読む)

積層型誘電体フィルタ

【課題】 高湿環境下であっても、内部の容量素子の水分による特性変化を抑えられる積層型誘電体フィルタを提供する。

【解決手段】 誘電体層1a〜1jが積層され、異なる誘電体層間に形成された一対の内部電極51〜54,60で構成した容量素子C1〜C4を含む積層体1と、積層体1の側面に形成した入出力端子21a〜24a、接地端子30a,30bとを含む積層型誘電体フィルタ10であり、容量素子C1〜C4を構成する一方の内部電極51〜54が、入出力側貫通導体81eと、一方の内部電極51〜54とは異なる誘電体層間に形成した入出力側導体層41e〜44eとを介して入出力端子21a〜24aに接続され、容量素子C1〜C4を構成する他方の内部電極60が、接地側貫通導体81f,82fと、他方の内部電極60とは異なる誘電体層間に形成した接地側導体層70a,70bとを介して接地端子30a,30bに接続された積層型誘電体フィルタ10である。

(もっと読む)

電子部品

【課題】基板からの端子電極の剥離を防止することができる電子部品を提供する。

【解決手段】本発明の電子部品は、基板100と、基板100上に積層された配線層及び絶縁樹脂層の積層構造により形成された電子素子と、基板100上に積層された配線層M1、M2,M3の積層構造により形成された端子電極Tとを備え、基板面に対して鉛直に端子電極Tを切断した断面における、端子電極Tの上方縁端と上方縁端と対角方向にある下方縁端とを結ぶ仮想線上において、絶縁樹脂層I1,I2の一部が存在するように、端子電極Tが形成されている。

(もっと読む)

ノイズフィルタ部品,ノイズフィルタ構造及びノイズフィルタ部品の使用方法

【課題】高速な差動信号と低速なシングルエンド信号が同一ライン上に混在するような伝送規格において、差動信号及びシングルエンド信号を、その波形品質に影響を与えることなく通すことができるノイズフィルタ部品,ノイズフィルタ構造及びノイズフィルタ部品の使用方法を提供する。

【解決手段】ノイズフィルタ部品1−1はコモンモードチョークコイル部2とコイル3とコイル4と外部電極6−1〜6−4とを備える。コモンモードチョークコイル部2は、高周波帯の差動信号を通す部分であり、コイル21,22を有する。外部電極6−1,6−2はコイル21の両端部に接続され、外部電極6−3,6−4はコイル22の両端部に接続されている。コイル3,4は、差動信号よりも低い周波数帯のシングルエンド信号を通すためのコイルであり、コイル21,22に並列に接続されている。

(もっと読む)

スパイラルインダクタおよびこれを用いたトランス

【課題】周辺に拡がる磁束を削減し、機器周辺に干渉する電磁誘導雑音を軽減するとともに小型でインダクタンス値の大きいインダクタを安価に実現する。

【解決手段】シリコン基板の表面に形成されたスパイラルコイルと、

該スパイラルコイルの中央部に前記シリコン基板を貫通して形成された第1磁性体と、

前記スパイラルコイルの外周に環状に形成された第2磁性体を有している。

(もっと読む)

積層バランスフィルタ

【課題】小型化が容易であり、入出力間で所定のインピーダンス変換を行えるようにした積層バランスフィルタを構成する。

【解決手段】第1のキャパシタ電極121とグランド電極120とが対向することによって不平衡側のキャパシタが構成される。誘電体層271には不平衡側コイル131が形成されている。誘電体層271,241,242には平衡側コイル141,142,143が形成されている。平衡側コイル141、142,143はヘリカル状に形成されており、かつ、各コイルの巻き方向も同じ方向となるように形成されている。この3つの平衡側コイル141,142,143のうち中央のコイル142は不平衡側コイル131に近接配置されることにより、中央のコイル142は不平衡側コイル131と電磁界結合する。

(もっと読む)

ガラスセラミック配線基板およびコイル内蔵ガラスセラミック配線基板ならびにガラスセラミック配線基板の製造方法

【課題】 絶縁層を着色するとともに基板強度や絶縁信頼性の良いガラスセラミック配線基板を提供すること。

【解決手段】 ガラス相および第1結晶を含むガラスを有するガラスセラミックスからなり、遷移金属の酸化物または硫化物からなるスピネル構造の第2結晶を着色顔料として含む複数の絶縁層1と、フェライト結晶を有する、複数の絶縁層1の間に設けられた複数のフェライト層2と、表面および内部に形成された配線導体3とを備え、第1結晶と第2結晶とフェライト結晶とは同一の結晶構造であって、第1結晶と第2結晶との格子定数の差が第2結晶の格子定数の13.3%以内であるとともに、第2結晶とフェライト結晶との格子定数の差が第2結晶の格子定数の11.4%以内であることを特徴とするガラスセラミック配線基板である。基板強度や絶縁信頼性を保ちつつ、絶縁層を着色したガラスセラミック配線基板とすることができる。

(もっと読む)

コモンモードノイズフィルタ

【課題】本発明は、高周波帯域での使用が可能なコモンモードノイズフィルタを提供することを目的とするものである。

【解決手段】本発明のコモンモードノイズフィルタは、複数の絶縁層1を積層して形成された積層体2の内部に設けられた第1、第2のコイル3,4と、前記積層体2の下面2a、端面2bおよび上面2cに連続して設けられ、かつ前記第1のコイル3の両端部3aに接続された一対の第1の外部電極5a、5bと、前記積層体2の下面2a、端面2bおよび上面2cに連続して設けられ、かつ前記第2のコイル4の両端部4aに接続された一対の第2の外部電極6a、6bとを備え、前記一対の第1の外部電極5a、5bと前記第2のコイル4とを上面視にて重ならないようにし、さらに前記一対の第2の外部電極6a、6bと前記第1のコイル3とを上面視にて重ならないようにしたものである。

(もっと読む)

インダクタ部品

【課題】インピーダンスの変化を抑制して、信号の反射の発生が少ないインダクタ部品を提供すること。

【解決手段】インダクタ部品1は、コア10と、電極部20,21と、巻線30と、を備えている。巻線30は、絶縁被膜銅線等の導体線からなり、巻芯部12に3ターン以上巻回された巻回部32と、巻回部32の両端32a,32bに位置する引き出し部34と、を含んでいる。引き出し部34は、その端が電極部20,21に継線されることにより、電極部20,21に物理的且つ電気的に接続されている。巻回部32における各ターンの巻線間隔Dn(n=1〜4)は、巻回部32の一端32aから他端32bに向かって単調減少している。巻回部32における導体線の幅は、巻回部32の一端32aから他端32bに向かって単調減少している。

(もっと読む)

161 - 180 / 702

[ Back to top ]