Fターム[5E317GG14]の内容

プリント配線間の電気接続のための印刷要素 (17,195) | 目的、効果 (2,983) | 高密度化 (376)

Fターム[5E317GG14]に分類される特許

361 - 376 / 376

プリント回路基板

【課題】本発明は、表面に実装可能な電気部品(2)を有するプリント回路(1)における記録密度を増加させるために使用される配列に関する。

【解決手段】プリント回路基板(1)は、2つのフィルム(3x、3y)により形成され、これらのフィルム(3x、3y)は互いに押圧され、これらのフィルム(3x、3y)の間に誘電体(4)が形成されている。フィルム(3x、3y)における少なくとも1つの互いに対向する面(3a、3b)が、表面実装型電気部品(2)に接合するようになっている。本発明によれば、プリント回路(1)の中に、2つのフィルム(3x、3y)を接続させるための複数のビアホール(6b)が設けられており、各ビアホール(6b)は、フィルム(3x、3y)の互いに対向する面(3a、3b)の間で直接的に接続されている。  (もっと読む)

(もっと読む)

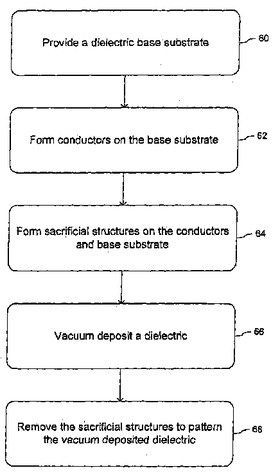

高信頼性多層回路基板およびその形成方法

マルチチップモジュールまたはハイブリッド回路用の多層回路基板は、誘電性のベース基板、ベース基板に形成された導体、および導体およびベース基板上に形成された真空堆積誘電体薄膜を含む。真空堆積誘電体薄膜はシャドウマスク法により形成された犠牲構造を用いてパターニングされる。この方法で形成された基板により、配線密度を著しく高めることができると共に基板全体の厚さを著しく減少させることができる。  (もっと読む)

(もっと読む)

電子モジュールの製造方法

この公表は、絶縁材料シート(1)から製造を開始する電子モジュールの製造方法を開示する。シート(1)には、この絶縁材料シート(1)を経てその反対側の表面(1a)上にある導電層まで延在する少なくとも1つの凹所(2)を形成する。凹所2内にコンポーネント(6)を設定する。このコンポーネントの接点面を導電層の方に向けてコンポーネント(6)を導電層に取り付ける。この後に、凹所2を閉成している導電層から導電パターン(14)を形成する。この導電パターンは、凹所内に設定したコンポーネントの少なくとも幾つかの接点領域又は接点突出部に電気的に接続される。  (もっと読む)

(もっと読む)

両面配線ガラス基板の製造方法

両面配線ガラス基板の耐熱性を向上させる。 両面配線ガラス基板(1)の表裏面を電気的に接続するための貫通孔(3)に金属銅からなる銅膜層(5)を充填する。銅膜層(5)は、まず貫通孔(3)壁面に無電解メッキ銅層(5a)を形成した後、電解メッキ銅層(5b)を形成することにより充填する。これにより、両面配線ガラス基板(1)の表裏面が確実に電気的に接続可能になるとともに、両面配線ガラス基板(1)全体として高い耐熱性を確保することが可能になる。 (もっと読む)

多層プリント配線板の接続構造

【課題】高密度実装に適合する多層プリント配線板の接続構造を提供する。

【解決手段】FPC2は、FPC2の露出導体部2Aにおいて突起20が形成されている複数の導体21と、導体21に配置される絶縁性の基材22と、導体部21において基材22と補強板24との間に介装される弾性部材23と、を有して積層されている。多層プリント配線板1は、露出導体部2Aが挿入される幅と奥行きを有する切り欠き溝10Aを形成している内層板10と、切り欠き溝10Aに貫通する複数のスルーホール端子11Aが形成されている第1外層板11と、第1外層板11に対向する第2外層板12と、を有して積層されている。FPC2の突起20が挿入口10B内からスルーホール端子11Aにかん合して圧接することにより、FPC2と多層プリント配線板1が電気的に接続される。

(もっと読む)

薄膜基板を処理するための方法

本発明は、フレキシブルプリント回路カードを形成するために、薄膜基板の中に延在するか、又は薄膜基板を貫通し、向かい合っていない表面に沿って電気的に接続される複数のマイクロバイアを有し、電気回路を形成するようにする、処理された薄膜基板(10)及びその方法を含む。ここでは第1のバイア(V10、V30、V50)と呼ばれる第1の数のバイアを形成するために、第1の数の実在ナノトラックが、良好な電気的特性を有する第1の材料(M1)で満たされ、一方、ここでは第2のバイア(V20、V40、V60)と呼ばれる第2の数のバイアを形成するために、第2の数の実在ナノトラックが、良好な電気的特性を有する第2の材料(M2)で満たされる。上記第1のバイア及び第2のバイア(V10〜V60)の第1の材料(M1)及び第2の材料(M2)が互いに異なる熱電気的特性を有するように選択される。薄膜基板の表面に被着され、薄膜基板(10)の両側(10a、10b)にコーティングされる材料が、第1の材料(M1)を割り当てられた第1のバイアと第2の材料(M2)を割り当てられた第2のバイアとを電気的に相互接続できるようにするために配設及び/又は構成され、電気的熱電対(100)又は他の回路構成を形成するために、直列接続に含まれる最初のバイア(V10)及びその直列接続に含まれる最後のバイア(V60)が直列に適当に組み合わせられる。  (もっと読む)

(もっと読む)

接続線の形成方法、電子デバイス用基板、電子デバイスおよび電子機器

【課題】各種電子デバイスの小型化(特に、小面積化)に貢献し得る接続線の形成方法、電子デバイス用基板、および、この電子デバイス用基板を備える電子デバイス、電子機器を提供すること。

【解決手段】接続線の形成方法は、基板7の少なくとも一方の面に、形成される接続線81に接続される配線パターン71を形成する工程と、基板7の縁部72に、基板7の両面721、722および端面723に亘って、導電層8を形成する工程(第1の工程)と、導電層8の一部を除去して、互いに導通しない複数の接続線81に分割する工程(第2の工程)とを有している。また、導電層8を形成する工程(第1の工程)において、導電層8の少なくとも一部は、基板7を切り出す前の原板に形成されるのが好ましい。

(もっと読む)

回路構成体及びその製造方法

【課題】回路構成体において、簡素かつ薄型の構造で半導体スイッチング素子を含む電力回路及びその制御回路を構築し、かつ、放熱性を高める。また、その回路構成体を効率良く製造する。

【解決手段】プリント回路基板20の一方の面に半導体スイッチング素子30が介在する電力回路を構成する導体パターンが形成され、他方の面に前記半導体スイッチング素子30を制御する制御回路を構成する導体パターンが形成され、かつ、基板20の貫通孔を用いて両導体パターンに半導体スイッチング素子30が実装された回路構成体。この回路構成体は、前記プリント回路基板20の一方の面に補強板10を積層しておき、この補強板10と反対の側から半導体スイッチング素子30を実装する方法により効率良く製造することができる。

(もっと読む)

プリント配線板

【課題】バイアホールの上に部品を実装することができ、スタックドビアも可能なビルドアッププリント配線板において、複数回めっきに伴いエッチング代が厚くなるのを阻止し、細線化と配線パターンの高精度化にも有効なプリント配線板を提供する。

【解決手段】銅はくをエッチングして形成したバンプによって層間接続がとれるため、従来のようにバイアホールの導通化のためのめっきが不要となり、エッチング代が薄くなることにより、細線化と配線パターンの高精度化を可能としたプリント配線板を提供することができる。

(もっと読む)

半導体装置

【課題】 はんだ接合部の応力集中を緩和しディバイスに発生する内部熱を効率的に放熱して信頼性の向上を図る。

【解決手段】 実装面2aに接続電極6と周辺補強用ダミー電極7と中央補強用ダミー電極8が形成されたディバイス2と、接続ランド10と周辺補強ランド11と中央補強ランド12とが形成されディバイス2をディバイス実装面3a上に実装する実装基板3とを備える。実装基板3には、中央補強ランド12に接続される放熱ビア14と、裏面3bに放熱パターン15が形成され、中央補強ランド12がディバイス2からの発生部を兼用して裏面3bからの放熱を行う。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】 コンデンサを高密度で内蔵し、不良品発生率が低いプリント配線板およびプリント配線板の製造方法を提供することにある。

【解決手段】 コア基板30に、広く凹部32を形成し、複数個のコンデンサ20を凹部32に収容する。凹部32内に、複数個のコンデンサ20を高密度で内蔵することができる。さらに、凹部32内の複数個のコンデンサ20の高さが揃うため、コンデンサ20上面の樹脂層を均一の厚みにでき、不良品発生率を下げることが可能となる。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】 ループインダクタンスを低減できるプリント配線板及びプリント配線板の製造方法を提供する。

【解決手段】 プリント配線板10内にチップコンデンサ20Aを配置するため、ICチップ90とチップコンデンサ20Aとの距離が短くなり、ループインダクタンスを低減することができる。また、厚いコア基板30内にチップコンデンサ20A、チップ抵抗20Bを収容するためプリント配線板を厚くすることがない。コア基板30内にチップ抵抗20Bを収容するため、プリント配線板の高集積化を実現できる。

(もっと読む)

多層プリント配線板及び多層プリント配線板の製造方法

【課題】 スルーホールの配設密度を高め得ると共に、厚みを薄くできる多層プリント配線板及び該多層プリント配線板の製造方法を提供する。

【解決手段】 コア基板30に形成されたスルーホール36は、第1電解めっき層24と、無電解めっき膜26と、第2電解めっき層28とからなる。スルーホール36をめっき充填により形成するため、コア基板30の強度が高まり、反りが発生し難くなる。このため、コア基板を薄く形成でき、多層プリント配線板の放熱性を高めることが可能となる。

(もっと読む)

配線基板

【課題】 不必要に長い配線の形成または配線基板全体の多層化を必要としない配線基板を提供する。

【解決手段】 複数の電極42を有する半導体装置22が実装される配線基板110であって、前記半導体装置22の前記複数の電極42と接続される複数の外部電極43と、複数の第1相互接続46を有する第1配線基板24と、前記第1配線基板24と対向するように配設され、第2相互接続44を有する第2配線基板26とを有する。前記第2相互接続26は、前記複数の外部電極43が形成された領域によって2次元的な範囲が規定される実装領域内において、前記複数の外部電極43のうちの少なくとも1つの外部電極と電気的に接続され、かつ、前記実装領域外において、前記複数の第1相互接続46のうちの少なくとも1つの第1相互接続と電気的に接続されている。

(もっと読む)

配線基板およびその製造方法

【課題】セラミック系の配線基板において、配線回路層の微細配線化、低抵抗化を達成でき、かつ配線回路層の絶縁基板への接着強度が高い配線基板とそれを歩留り良く作製することのできる配線基板の製造方法を提供する。

【解決手段】セラミック系絶縁基板2の少なくとも表面に、Cu、Ag、Al、Au、Ni、Pt及びPdから選ばれる少なくとも1種からなる金属含有量が99重量%以上の金属箔などからなる高純度金属導体からなる配線回路層3を絶縁基板2表面と同一平面となるように埋設してなるとともに、配線回路層3の配線方向に直交する断面が逆台形形状からなり、その逆台形形状における下底6と横辺7とがなす形成角αを45〜80°とし、特に、表面配線回路層3aの絶縁基板2への埋設側の平均表面粗さを200nm以上、絶縁基板2の40〜400℃における平均熱膨張係数を6ppm/℃以上とする。

(もっと読む)

多層配線基板及びその製造方法

【課題】 コア基板を貫通して形成する導通部を高密度に形成することができ、放熱性、電気的特性に優れた多層配線基板を提供する。

【解決手段】 コア基板の両面または片面に配線パターン34、36が形成され、コア基板を貫通させて形成された導体部に前記配線パターンが電気的に接続された多層配線基板において、前記コア基板が、めっきにより形成されたビア柱26と導体コア部28とからなる導体部と、該ビア柱26と導体コア部28を電気的に絶縁する絶縁体部20とから成る。コア基板に配線パターンを形成した後、導体基板10を除去することによって多層配線基板が得られる。

(もっと読む)

361 - 376 / 376

[ Back to top ]