Fターム[5E346AA13]の内容

多層プリント配線板の製造 (97,916) | 多層の形状、構造 (21,562) | 層の形状、構造が特定されたもの (8,277) | 誘電体層 (326)

Fターム[5E346AA13]に分類される特許

1 - 20 / 326

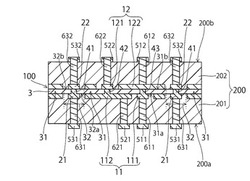

積層構造体及びコンデンサ内蔵基板の製造方法

【課題】コンデンサ内蔵基板に形成される配線パターンの設計自由度の低下を抑えることが出来、且つ特性不良が発生し難い積層構造体を提供する。又、その様な積層構造体を備えたコンデンサ内蔵基板の製造方法を提供する。

【解決手段】積層構造体において、第1電極層11は、誘電体層3のうちコンデンサを構成する第1部分31にて、該第1部分31の表面に形成されている。第2電極層12は、第1部分31の裏面に形成されている。第1導電層21は、誘電体層3のうち第1部分31とは異なる第2部分32にて、該第2部分32の表面に形成されると共に、第1電極層11から離間して配置されている。第2導電層22は、第2部分32の裏面に形成されると共に、第2電極層12から離間して配置されている。第1導電部41は、第2部分32をその表面から裏面に貫通すると共に、第1導電層21と第2導電層22とを互いに電気的に接続している。

(もっと読む)

電源制御回路モジュール

【課題】電源制御の特性を低下させることなく、より小型な電源制御回路モジュールを提供する。

【解決手段】積層体20の表面には、スイッチングレギュレータ用素子31A,31B,31C,31Dおよびリニアレギュレータ用素子32が間隔をおいて実装されている。積層体20の誘電体層202,203の界面には、電極非形成部300によって分離された内部グランド電極2211,2212,2213,2214,2215が形成されている。内部グランド電極2211,2212,2214,2215は、それぞれスイッチングレギュレータ用素子31A,31B,31C,31Dに接続されている。内部グランド電極2213は、リニアレギュレータ用素子32に接続されている。内部グランド電極2211,2212,2213,2214,2215は、それぞれ異なる外部グランド端子に接続されている。

(もっと読む)

シート積層体およびセラミック素子作製方法

【課題】層面内における横方向の縮みが最小化されておりかつ公知の方法に比べて作製が容易なシート積層体を含むモノリシックセラミック素子を提供すること。

【解決手段】本願発明のシート積層体は、機能性セラミックからなる機能層に対するグリーンシートと、多層構造にてこの機能層に直に隣接する誘電材料製のテンション層に対するグリーンシートと、メタライゼーション面とを有しており、このメタライゼーション面の間に機能層が配置されている。テンション層に対するグリーンシートは、機能性セラミックの焼成温度以下の相転移温度を有しており、この相転移温度にて再結晶される相に移行し、この相は、機能性セラミックの焼成温度を上回るまで固体状態に止まる。テンション層には、機能層の焼成温度において機能性セラミックと実質的に反応または拡散しない任意のセラミック相が含まれる。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

電子部品及びその製造方法

【課題】拘束層材料と素子層材料の電子特性との相対的な関係を選択することにより、側電極の深さを全体的な電気の影響を最小限に抑える。

【解決手段】電子部品およびその製造方法は、まず、第二電子特性を有する拘束層を第一電子特性を有する素子層に形成する。前記電子部品の特性は、前記第一電子特性によって主に影響される。その後、両方の拘束層及び素子層を焼結温度で焼結する。第一電子特性と第二電子特性との関係を選択することにより、電子部品の特性が安定になる。

(もっと読む)

多層配線基板およびその製造方法、並びに半導体装置

【課題】薄膜キャパシタの導電層と誘電層との界面での剥離を抑えることが可能な多層配線基板およびその製造方法、並びにこの多層配線基板を備えた半導体装置を提供する。

【解決手段】上部電極および下部電極の間に誘電層を有する薄膜キャパシタを備えた機能領域と、前記機能領域以外の周辺領域とを有し、前記周辺領域の少なくとも一部に、前記誘電層および導電層が積層された係留部が設けられ、前記導電層の前記誘電層に接する面のラフネスが、前記上部電極または前記下部電極の前記誘電層に接する面のラフネスよりも大きい多層配線基板。チップおよび前記多層配線基板を備えた半導体装置。

(もっと読む)

パッケージ構造とその製造方法

【課題】放熱性が良好で、かつ小型で薄型のパッケージ構造およびその製造方法を提供する。

【解決手段】基板110の開口116に、電子デバイス120が配置され、接着剤層130上のパターン化金属層140が基板110の下表面113上にラミネートされるとともに、電子デバイス120の底表面124を露出させる。露出された底表面124上に散熱コラム150が形成され、第1ラミネート構造160が基板110の上表面111および電子デバイス120の頂表面122を被覆し、第2ラミネート構造170が散熱コラム150ならびにパターン化金属層140を被覆する。

(もっと読む)

電子部品内蔵型多層基板

【課題】層間密着性に優れ、高温高湿の環境下においても誘電特性の変動が少なく、伝送損失の小さい電子部品内蔵型多層基板を提供すること。

【解決手段】第一の誘電体層4の少なくとも片面に回路パターン3,5により受動素子3a,5aを形成してなる回路板の両面に、第一の誘電体層4よりも低い比誘電率を有する第二の誘電体層2,6を積層してなる積層板を含んでなり、第一の誘電体層4は脂環式構造含有ポリマー及び無機充填剤を含む架橋性樹脂成形体(I)を硬化してなるものである、電子部品内蔵型多層基板。

(もっと読む)

多層導波管、及びその製造方法

【課題】複数の導波管が重ね合わされ、各導波管の内部が誘電体で充填された構成において、高集積化及び軽量化を図ることができるとともに、信頼性を向上させることができる多層導波管、及びその製造方法を提供する。

【解決手段】基礎導波管形成部101と積層導波管形成部102とは、絶縁性の第1の接着剤50により互いに接着されている。基礎導波管形成部101は、互いに間隔をおいて対向配置された板状の第1及び第2の主導体1a,1bと、それらの間に充填された第1の誘電体2とを有している。積層導波管形成部102は、第3の主導体21と、第3の主導体層21の主面に層状に形成された第2の誘電体22とを有している。第2の誘電体22の主面における第2の貫通導体23aの接着剤50に接する側には、第2の誘電体22の主面から突出するように、ランド24が設けられている。

(もっと読む)

車両用多層配線基板、およびこの基板を用いた車両用電動コンプレッサ

【課題】コンデンサを搭載することなくノイズ低減することができる車両用多層配線基板を提供することを目的とする。

【解決手段】車両のボディ4に接地する低電圧用金属グランドパターン24を形成した低電圧グランド層21と、車両のボディ4と絶縁する高電圧用金属グランドパターン25を形成した高電圧グランド層22とを有し、基板材20を挟んだ一方の面が低電圧グランド層21であり、他方の面が高電圧グランド層22である車両用多層配線基板である。

(もっと読む)

電子部品の製造方法

【課題】外部電極層上にめっき層を均一な厚さで形成することができ、製品歩留まりを向上させることができる電子部品の製造方法を提供すること。

【解決手段】焼成前のセラミック材料を用いて板状に形成された多数個取り用の未焼成セラミック積層体159を準備する。未焼成セラミック積層体159において、個々のセラミックコンデンサ101に分割するためのブレイク溝163,164を形成することにより、製品領域を平面方向に沿って縦横に区分する。ブレイク溝163,164が交差する部分に面取り用ブレイク溝165を形成する。面取り用ブレイク溝165によって画定される面取り用分割線L2で囲まれた略矩形状の領域は、分割工程後に捨て材となる非製品領域R2であり、非製品領域R2とコンデンサ形成領域R1とで外部電極層が電気的に接続された状態で面取り用ブレイク溝165が形成される。

(もっと読む)

EBG構造及び基板

【課題】低周波数帯域のバンドギャップ特性を得ることが可能であり、小型化可能であるEBG構造、及びそれを備える基板を提供する。

【解決手段】本発明の一実施形態に示されるEBG構造は、導体層101と、導体層101とキャパシタンスを形成する導体層102と、導体層102にビア104aを介して接続される導体層103を有し、導体層103は導体板113a、113b、113c、113dから構成され、導体板113a、113b、113c、113dとビア104aとは導体線105a、105b、105c、105dを介してそれぞれ接続されているので、低周波数帯域のバンドギャップ特性を得ることができる。

(もっと読む)

積層型電子部品およびその製造方法

【課題】積層型電子部品において共振器のQ値を高め電気的特性を向上させる。

【解決手段】第一配線層及び第二配線層を含む2層以上の配線層と、第一配線層と第二配線層の間に介在された絶縁層と、絶縁層を貫通して第一配線層に備えた第一導体と第二配線層に備えた第二導体とを電気的に接続する貫通導体とを備えた積層型電子部品であって、貫通導体はその両端に、第一導体又は第二導体に向かうにつれ径が大きくなった拡径部を有する。

(もっと読む)

プリント基板の製造方法

【課題】先行技術は、加工時間の増加によりスループットが低くなることがあり、さらには、ビアおよび配線生成工程を多数利用する必要が出てきて、それら工程が複合的アライメント誤りを生じ得るので、特に目下のアライメント予算内では役に立たないであることがある。

【解決手段】基板に金属パネルをレーザ投影パターニングすることと、金属パネル上に誘電体層をラミネートすることと、基板の複数のビアを形成すべく基板をレーザ照射することと、基板のシードコートをレーザ活性化することと、基板のパターニングされていない部分からシードコートを洗浄することと、基板に、パターニングされたビルドアップ層を形成することと、複数の金属突起を形成すべく金属めっきをエッチングで除去することによりプリント回路を形成する。

(もっと読む)

プリント配線板及びその製造方法

【課題】ビルドアップの流れの中でコンデンサ部を形成することができるプリント配線板を提供する。

【解決手段】プリント配線板10では、上部電極接続部52は、上部電極接続部第1部52aがコンデンサ部40と接触することなくコンデンサ部40を上下方向に貫通し、コンデンサ部40の上方に設けられた上部電極接続部第3部52cを経て上部電極接続部第2部52bから上部電極42に繋がっている。また、下部電極接続部51は、コンデンサ部40の上部電極42とは接触しないが下部電極41とは接触するようにコンデンサ部40を上下方向に貫通している。このため、ビルドアップしていく流れの中で、2枚の金属箔で高誘電体層を挟んだ構造を有し後にコンデンサ部40となる高誘電体キャパシタシートでもって全面を覆ったあとでも、上部電極接続部52や下部電極接続部51を形成することができる。

(もっと読む)

積層回路基板

【課題】 寸法を小型に保ちながら、特性を劣化させることなく、設計自由度の高い積層回路基板を提供する。

【解決手段】誘電体層35の表面には、導体ペーストを印刷してなる加圧部材40が形成されている。積層方向から見て、この加圧部材40はコンデンサ電極38bと重なっている。この加圧部材40によって、積層回路基板30の製造時に、容量C1の容量値を大きくできる。

(もっと読む)

積層型高周波モジュール

【課題】アナログ回路部とデジタル回路部とを有しながらも、特性を劣化させることなく小型化が可能な積層型高周波モジュールを実現する。

【解決手段】積層体100は、複数の誘電体層101−118を積層してなる。誘電体層101−103は下層領域であり、デジタル回路が配設される。誘電体層104−115は中間層領域であり、デジタル回路とアナログ回路とが、積層体10を平面視して重ならないように配設される。誘電体層116−118は上層領域であり、デジタル回路が配設される。上層領域の上部にあたる積層体100の天面には、デジタルICが実装されている。下層領域と中間層領域との間には内層グランド電極401が略全面に配設され、中間層領域と上層領域との間には内層グランド電極402が略全面に配設される。中間層領域では、デジタル配線と内層グランド電極が積層方向に交互に形成される。

(もっと読む)

セラミック多層基板の製造方法、及びセラミック多層基板

【課題】複数の素子を含むセラミック多層基板の製造コストを低減できるセラミック多層基板の製造方法、及びセラミック多層基板を得ること。

【解決手段】セラミック多層基板の製造方法は、第1の面積を有するセラミック層が第1の層数で積層されるとともに回路パターンが形成された未焼成の下地積層体に、前記第1の面積より小さい第2の面積を有するセラミック層が前記第1の層数より少ない第2の層数で積層されるとともに第1の素子が形成された未焼成の第1の素子積層体と、前記第1の面積より小さい第3の面積を有するセラミック層が前記第1の層数より少ない第3の層数で積層されるとともに第2の素子が形成された未焼成の第2の素子積層体とを圧着する圧着工程と、前記下地積層体と圧着された前記第1の素子積層体及び前記第2の素子積層体とを焼成して一体化する焼成工程とを備えている。

(もっと読む)

セラミックデバイスの製造方法およびセラミックデバイス

【課題】反りが抑制されたセラミックデバイスを提供する。

【解決手段】複数のセラミックスグリーンシートの積層体を焼成することによりセラミックデバイスを製造する方法が、積層体の表面および裏面となるセラミックスグリーンシートに、アルミナを主成分とし、焼成時において積層体の焼成収縮挙動に対する拘束能を有するペーストを塗布する工程と、ペーストが塗布された積層体を焼成することによって、ペーストの焼成収縮挙動の拘束下で積層体をあらかじめ定められた収縮率で焼成収縮させてセラミックデバイスを得る工程と、を備える。

(もっと読む)

電磁結合構造、多層伝送線路板、電磁結合構造の製造方法、及び多層伝送線路板の製造方法

【課題】高密度に集積できる電磁結合構造、多層伝送線路板、及びそれらの製造方法を提供すること。

【解決手段】マイクロ波帯の周波数帯域で使用される電磁結合構造であって、内側誘電体層23が、複数のグランド層となる内側導体層12、15の間に挟まれて積層された積層体と、積層体を間に挟んで対向する一対の外側誘電体層21、25と、一対の外側誘電体層21、25を間に挟んで対向する一対の外側導体層11、16と、を備える。積層体には、内側誘電体層23及び複数のグランド層となる内側導体層12、15を貫通する孔Sが設けられており、孔Sの内壁に形成された管状の金属膜3を介して、複数のグランド層となる内側導体層12、15が電気的に接続されることにより、一対の外側導体層11、16が電磁結合されることを特徴とする。

(もっと読む)

1 - 20 / 326

[ Back to top ]