Fターム[5E346FF45]の内容

多層プリント配線板の製造 (97,916) | 導体層間接続の方法 (9,115) | 部品の実装によるもの (1,788)

Fターム[5E346FF45]に分類される特許

61 - 80 / 1,788

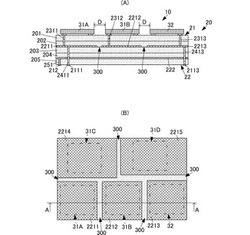

電源制御回路モジュール

【課題】電源制御の特性を低下させることなく、より小型な電源制御回路モジュールを提供する。

【解決手段】積層体20の表面には、スイッチングレギュレータ用素子31A,31B,31C,31Dおよびリニアレギュレータ用素子32が間隔をおいて実装されている。積層体20の誘電体層202,203の界面には、電極非形成部300によって分離された内部グランド電極2211,2212,2213,2214,2215が形成されている。内部グランド電極2211,2212,2214,2215は、それぞれスイッチングレギュレータ用素子31A,31B,31C,31Dに接続されている。内部グランド電極2213は、リニアレギュレータ用素子32に接続されている。内部グランド電極2211,2212,2213,2214,2215は、それぞれ異なる外部グランド端子に接続されている。

(もっと読む)

プリント基板

【課題】 複数のメタライズ層に形成されている導電トラックで構成されているコイルによって発生する、垂直巻線軸に沿う磁界の一様性を高めることができるプリント基板を提供する。

【解決手段】 このプリント基板においては、垂直方向に連続している第1のメタライズ層と第2のメタライズ層とに形成されている導電トラック(90、92、102、104、114、116、130、132、140、142、150、152)の、メタライズ層に平行な1つの平面上への重ね合わせによって、互いに直交しており、かつメタライズ層に平行である軸XおよびYを対称軸とする2軸対称性を有するパターンが形成され、重ね合わされる第1のメタライズ層および第2のメタライズ層の各々の単一または複数の導電トラックは、それだけでは、軸Xおよび/またはYを対称軸とする軸対称性を有していない。

(もっと読む)

モジュールの製造方法

【課題】層間接続導体を形成する複数の接続端子が支持体に挿入されてなるる端子集合体を形成し、この端子集合体を配線基板に実装することで、層間接続導体を備えるモジュールを低コストかつ短い製造時間で製造できる技術を提供する。

【解決手段】層間接続導体を形成する柱状の接続端子11および電子部品102を配線基板101上に実装し、樹脂封止してなるモジュール100を製造する場合に、配線基板101の一方主面に、電子部品102を実装するとともに、複数の孔が形成された支持体12に接続端子11を挿入して成る端子集合体10を実装し(第1実装工程)、実装された電子部品102ならびに端子集合体10を樹脂層により封止する(第1封止工程)。こうすることにより、層間接続導体を有するモジュール100を低コストかつ短い時間で製造できる。

(もっと読む)

配線基板及びその製造方法、及び半導体装置

【課題】接続端子の狭ピッチ化を図ることのできる配線基板及びその製造方法、及び半導体装置を提供する。

【解決手段】配線基板11の表面となる第1の主面と、前記第1の主面とは反対側に位置する第2の主面とを備えた第1の絶縁層14と、前記第1の絶縁層を前記第1の主面側から前記第2の主面側に貫通して設けられた開口部14Aと、前記開口部内から前記開口部の壁面を経由して前記第2の主面上に延出して設けられ、一体に形成された導体層と、前記導体層を被覆して前記第2の主面に設けられた第2の絶縁層21と、前記第2の絶縁層に設けられたビア24と、を有し、前記開口部内に設けられた前記導体層の、前記第1の主面に露出する部分が、接続端子15となり、前記導体層の、前記開口部の壁面を経由して前記第2の主面上に延出して設けられた部分が、配線パターン16となり、前記ビアが、前記第2の主面上に延出した前記配線パターンに接続されている。

(もっと読む)

部品内蔵配線基板及びその製造方法

【課題】コア基板の収容部内に内蔵部品を収容する際、複雑な加工を行うことなく内蔵部品の正確な位置決めが可能な部品内蔵配線基板を提供する。

【解決手段】部品内蔵配線基板10は、コア基板11と、コア基板11を貫通する収容部21と、収容部21に収容された内蔵部品50と、コア基板11の上下に積層形成した配線積層部12、13とを備えている。収容部21は、平面視で方向が異なる第1及び第2の内壁面を含むコア基板11の内壁面20によって画定され、内蔵部品50は、第1及び第2の内壁面のそれぞれと部分的に接した状態で収容部21に収容され、内壁面20と内蔵部品50との間隙部において内蔵部品50が第1及び第2の内壁面と接していない領域に樹脂充填材Fが充填されている

(もっと読む)

部品内蔵基板およびその製造方法

【課題】デバイス側の設計の自由度を増大させると共に、さらなる高アスペクト比および高精細化を可能とし、特に剥離に対する耐性を増すことができる部品内蔵基板を提供する。

【解決手段】部品内蔵基板100は、概して、第2の基材4、スペーサ2、第3の基材5、第1の基材3が、この順で積層一体化された構造となっている。更に、スペーサ2および第3の基材5の層における中央部分は、これらに代わり、部品としてのIC積層体が内蔵されている。IC積層体は、第1の内蔵IC11と、第2の内蔵IC12と、それらを接合するIC接合剤13とで構成されている。ここで、第1の内蔵IC11は、電極111と、その電極111上に微小バンプ112とを含んでいる。また、第2の内蔵IC12は、ウエハ状態のICに形成された電極と、そのウエハの両面に形成された回路とを含んでいる。電極111部分の貫通孔には、層間接着剤43が充填される。

(もっと読む)

部品内蔵基板およびその製造方法

【課題】ハンダ等の再溶融がなくなり、工程を簡略化可能な部品内蔵基板およびその製造方法を提供する。

【解決手段】第1積層基板11の一方の面11aに第1電子部品T1を載置する第1電極13と、第1積層基板に凹部14を設け、第1積層基板内部の配線回路が凹部内に露呈され、第2電子部品T2の一端T2aと接続する第2電極16とを備える第1配線基板17と、第2積層基板21の一方の面に凹部24を設け、第2積層基板内部の配線回路が凹部内に露呈され、第2電子部品T2の他端T2bと接続する第3電極26とを備える第2配線基板27と、を備えており、第1配線基板と第2配線基板との一方の面はそれぞれの凹部が互いに対向する内面に向いて開口するように配されており、各々の電子部品と各々の電極とは、導電性ペーストPからなる層間導通部により接続される。

(もっと読む)

部品内蔵基板およびその製造方法

【課題】電子部品を内蔵するための開口部を小さくできる部品内蔵基板を提供する。

【解決手段】第1絶縁層3cに第1導電層4c1と層間導通部1c2が形成された第1の基板3Aと、層間導通部1c2と接続される電子部品2と、第2絶縁層3bに第2導電層4b1が形成され、電子部品2を内蔵する位置に開口部6を有する第2の基板2Aと備えた部品内蔵基板10。第2導電層4b1は、平面視枠状の枠状部7b1を有する。開口部6は、枠状部7b1の内側領域8b1全域の第2絶縁層3bを厚さ方向に貫通して形成されている。

(もっと読む)

部品内蔵配線基板及びその製造方法

【課題】内蔵部品をビア導体を介して電気的に接続する際の接続信頼性を高めることが可能な部品内蔵配線基板を提供する。

【解決手段】本発明の部品内蔵配線基板10は、コア基板11に内蔵された板状の部品70と、絶縁層と導体層とが交互に積層されたビルドアップ層12(13)を備えている。部品70は、その両端部に側面部及び主面部を有する端子電極が形成され、主面部の側の絶縁層20(21)には、端子電極の側面部及び主面部と接続されるビア導体60(61)が形成されている。ビア導体60は、下方の端子電極に近接するほどビア径が小さくなるテーパ状に形成され、端子電極の表面部との接続箇所におけるビア径が端子電極の主面部の長さよりも大きい。これにより、ビア導体60と部品70の端子電極との接続面積を拡大し、かつ位置ずれに対する許容度を高めることで、接続信頼性が向上する。

(もっと読む)

複合多層基板およびそれを用いたモジュール

【課題】 基板の補強材にガラスクロスを用いた場合、マイグレーションの発生に伴う電気的特性の悪化を招き、また、キャビティ形成時にガラスクロスの切断加工が必要で製造コストのアップを招く。

【解決手段】 複合多層基板20は、金属製材料からなる平板状のコア部材21と、コア部材21の表面と裏面を覆う表面側樹脂層22および裏面側樹脂層23と、表面側樹脂層22および裏面側樹脂層23のいずれか一方又は双方に形成された電極(第1及び第2の電極)と、コア部材21の表裏を貫通して形成された無底穴24または有底穴と、無底穴24または有底穴に実装する電子部品25とを備え、電子部品25に対する電気的接続を第1の電極を介して行うようにし、コア部材に対する電気的接続を第2の電極を介して行うようにしたことを特徴とする。

(もっと読む)

集合配線基板

【課題】

1枚の集合配線基板から同時に製造できる電子部品の数量減少を防ぎ、もって作業効率低下やコスト増といった問題を解決することができるとともに、平坦な配線基板に半導体素子が搭載され、他の回路基板に良好に実装することが可能な電子装置を安定して供給することが可能な集合配線基板を提供すること。

【解決手段】

半導体素子15が搭載される搭載部8を上面中央部に有する複数の配線基板10と、前記搭載部8を囲繞する大きさの複数の貫通口24を有するフレーム20とを備え、前記配線基板10の上面周端部と前記フレーム20の前記貫通口24周辺部とを、前記搭載部8を前記貫通口24から露出させるように接合して成ることを特徴とする集合配線基板30。

(もっと読む)

セラミック回路基板およびそれを用いた電子装置

【課題】放熱性の向上されたセラミック回路基板および電子装置を提供すること。

【解決手段】セラミック回路基板は、多層基板と、多層基板の上面または下面にろう材2によって接合された表層金属回路板3と、多層基板の内部に設けられた内層金属回路板4および金属柱5とを含んでいる。多層基板は、複数のセラミック基板1と複数のセラミック基板1の間に設けられた金属板11とを含んでいる。金属板11は、回路貫通孔11aを有している。複数のセラミック基板1および金属板11は、互いにろう材によって接合されている。内層金属回路板4は、回路貫通孔11a内に設けられている。金属柱5は、複数のセラミック基板1に形成された貫通孔1a内に配置されており、内層金属回路板4にろう材によって接合された第1の端部と表層金属回路板3にろう材によって接合された第2の端部とを有している。

(もっと読む)

回路基板

【課題】能動素子及び受動素子が基板の内部に実装された埋め込み回路基板において、夫々の素子の連結状態をテストするための基板構造及びそのテスト方法を提供する。

【解決手段】回路基板及び前記回路基板の内部に実装された素子のテスト方法が開始される。本発明の一実施形態による回路基板は、回路基板の内部に実装されて、一つ以上の接続端子を含む能動素子、一端が前記能動素子の接続端子のうち一つと電気的に連結されて、他端が前記回路基板の表面の信号パッドと電気的に連結される受動素子、及び前記受動素子の前記一端と電気的に連結されるテストパッドを含む。本発明によれば、能動素子及び受動素子が基板の内部に実装された場合にも夫々の素子の連結状態を効果的にテストすることができて、回路基板の不良の有無を容易に判別することができる。

(もっと読む)

配線基板の製造方法

【課題】接続信頼性に優れる配線基板の製造方法を提供する。

【解決手段】表面及び裏面を有し、表面に半導体チップSが実装される配線基板1の製造方法であって、導体層21,22,31,32,131,132及び樹脂絶縁層33,34,133,134をそれぞれ1層以上積層し、表面側及び裏面側の表層にそれぞれ少なくとも1以上の接続端子T1,T11を有するビルドアップ層3,13を形成する工程と、表面側のビルドアップ層34,134上にフィルム状の第1のソルダーレジストを積層して第1のソルダーレジスト層4を形成し、裏面側のビルドアップ層上に第1のソルダーレジスト層4よりも厚みの厚いフィルム状の第2のソルダーレジストを積層して第2のソルダーレジスト層14を形成する工程と、を有する。

(もっと読む)

部品内蔵配線板

【課題】絶縁板中に半導体チップがフリップ接続で埋設、実装された部品内蔵配線板において、フリップ接続の信頼性向上、配線板としての機能性の保全、および低コスト化。

【解決手段】積層状の第1、第2の絶縁層と、第1の絶縁層上に設けられた最外層の第1の配線パターンと、第2の絶縁層上に設けられた他方の最外層の第2の配線パターンと、第2の絶縁層に埋設された、端子パッドを有する半導体チップと、第1の絶縁層と第2の絶縁層とに挟まれた、半導体チップ用の実装用ランドを含む第3の配線パターンと、端子パッドと実装用ランドとの間に挟設された導電性バンプと、半導体チップと第1の絶縁層および第3の配線パターンとの間に設けられた樹脂とを具備し、第1の配線パターンの第1の絶縁層側とは反対側および第2の配線パターンの第2の絶縁層側とは反対側が粗化されていない一方、第3の配線パターンの第2の絶縁層側の表面が粗化されている。

(もっと読む)

積層焼結セラミック配線基板、及び当該配線基板を含む半導体パッケージ

【課題】微細な配線層を有するにもかかわらず、低いオープン不良率を有し、且つ高い高温高湿信頼性を有する、積層セラミック配線基板を提供する。

【解決手段】面内導体の少なくとも一部がファインライン化され、ファインライン化された面内導体の断面形状を台形とし、且つ当該台形状の断面の高さa、下底の長さc及び上底の長さd、並びに基板の主面に平行な面内において隣り合う面内導体の台形状の断面の下底の間隔bが特定の関係を満たすように構成する。

(もっと読む)

半導体実装部材及び半導体実装部材の製造方法

【課題】 多配線への対応及び電源強化を図りながら歩留まりが下がらない半導体実装部材を提供する。

【解決手段】 半導体実装部材100を第2基板110と第1基板10との2つのプリント配線板で構成するため、多配線への対応及び電源強化の目的で、1枚のビルドアップ基板の層数を増やしサイズを大きくするのと比較し、歩留まりが低下しない。第1基板10と第2基板110との間に支持体188が介在するので、第1基板10と第2基板110との間にアンダーフィルを充填させる必要が無い。

(もっと読む)

素子内蔵配線基板、及びその製造方法

【課題】チップ状の電気素子及び膜素子を含む素子内蔵配線基板であって、これらの素子の接続距離を短縮化して高周波特性を改善するとともに、小型化及び高集積化された素子内蔵配線基板を提供する。

【解決方法】相対向して配置される一対の第1の配線層及び第2の配線層、並びにこれらの配線層間に配設された第1の絶縁層を有する両面配線基板と、両面配線基板の、第1の配線層と対向するようにして設けられた第3の配線層と、第1の配線層及び第3の配線層間に配設された第2の絶縁層と、第2の絶縁層内に配設されるとともに、第1の配線層に実装されたチップ状の電気素子と、第1の絶縁層上又は第1の絶縁層内において、第1の配線層と電気的に接続されるとともに、電気素子と相対向するようにして配設され、電気素子より外方に露出したトリミング領域を有する膜素子と、を具えるようにして、素子内蔵配線基板を構成する。

(もっと読む)

配線基板およびその実装構造体

【課題】本発明は、電気的信頼性を改善した配線基板およびその実装構造体を提供することによって上記要求を解決する。

【解決手段】本発明の一形態にかかる配線基板3は、第1ネック構造13aを介して互いに接続した、酸化ケイ素を含む複数の第1無機絶縁粒子14aと、該第1無機絶縁粒子14a同士の間に配された、シロキサン結合を骨格とする樹脂を含む樹脂部材15とを有する絶縁層を備える。また、本発明の一形態にかかる実装構造体1は、上記配線基板3と、該配線基板3に実装された電子部品2とを備える。

(もっと読む)

素子内蔵配線基板、及びその製造方法

【課題】チップ状の電気素子及び膜素子を含む素子内蔵配線基板であって、これらの素子の接続距離を短縮化して高周波特性を改善するとともに、小型化及び高集積化された素子内蔵配線基板を提供する。

【解決方法】相対向して配置される一対の第1の配線層及び第2の配線層、並びにこれらの配線層間に配設された第1の絶縁層を有する両面配線基板と、両面基板の、第1の配線層と対向するようにして設けられた第3の配線層と、第1の配線層及び第3の配線層間に配設された第2の絶縁層と、第2の絶縁層内に配設されるとともに、第1の配線層に実装されてなるチップ状の電気素子と、第1の絶縁層内又は第2の絶縁層内において、第1の配線層と電気的に接続されるとともに、電気素子と相対向するようにして配設され、電気素子より外方に露出したトリミング領域を有する膜素子と、を具える。

(もっと読む)

61 - 80 / 1,788

[ Back to top ]