Fターム[5E346FF45]の内容

多層プリント配線板の製造 (97,916) | 導体層間接続の方法 (9,115) | 部品の実装によるもの (1,788)

Fターム[5E346FF45]に分類される特許

121 - 140 / 1,788

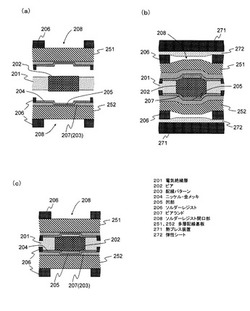

多層配線基板、部品内蔵基板、および多層配線基板の製造方法

【課題】配線基板と電気絶縁層を積層して一体化した多層配線基板において、電気絶縁層に形成されたビアと、配線基板に形成されたビアランド間の接続信頼性を向上させる。

【解決手段】貫通するビアホールに導電性ペーストが充填されて形成されたビア202を有する電気絶縁層201の表裏の、ビアに対応する位置に、ビアの、電気絶縁層の面方向の断面積より大きいビアランド207が形成された多層配線基板251、252が積層して一体化され、少なくとも一方の多層配線基板には、電気絶縁層に埋め込まれた電子部品が実装されている。ビアとビアランドとの間には、一部隙間205が形成されており、ビアと接触するビアランドの接触面積は、ビアの断面積の20%以上75%以下である。

(もっと読む)

積層板、回路基板、および半導体パッケージ

【課題】反りが低減され、薄型回路基板として適した積層板を提供すること。

【解決手段】第一ガラス繊維基材層101を含有する第一プリプレグ201と、有機繊維基材層を含みガラス繊維基材層を含まない1層以上の第二プリプレグ202と、第二ガラス繊維基材層102を含有する第三プリプレグ203と、をこの順に積層して得られる積層板100である。

(もっと読む)

微細配線パッケージ

【課題】電子部品の端子面を均一な高さに設定することにより、各端子に接続する導通孔による端子と配線との電気的接続を容易し、各部の位置ずれ等を生じにくい微細配線パッケージを得る。

【解決手段】一方の面に搭載した、各々複数の端子を有する高さの異なる複数の電子部品(12、14、16)と、電子部品の端子の表面を所定の平面上に揃えるように、これらの電子部品を、電極端子形成面が露出し且つ電子部品の側面の一部を覆うように、封止する封止樹脂(22)と、電子部品及び封止樹脂の表面上に形成した、電子部品の端子に電気的に接続する導体層(44)と、電子部品の電極端子形成面及び封止樹脂上に形成された配線層を覆う絶縁樹脂層(24)と、封止樹脂と絶縁樹脂層との間に形成した補強板(46)とを含む。

(もっと読む)

電子部品モジュール、その製造方法、およびDC−DCコンバータ

【課題】チップ側面にスルーホールを設ける場合において、樹脂等の絶縁体が充填されたとしてもマザーシートをチップ毎に分割することができる電子部品モジュールを提供する。

【解決手段】スルーホール内に充填された絶縁体31をレーザでカットして切り込み52を形成する。切り込み52は、積層体の上面からV字型に形成されている。したがって、V字型のブレイク用溝55とともに切れ込み52を外側に、矩形状のブレイク用溝51およびV字型のブレイク用溝57を内側にして曲げることで各チップにブレイクすることができる。チップ毎にブレイクされた電子部品モジュールは、この切れ込み52が形成されていることで、スルーホールの側壁に端面電極41が露出し、さらにこの露出した端面電極41が絶縁体31で覆われた状態となる。

(もっと読む)

多層基板の製造方法

【課題】熱可塑性樹脂フィルム層おける層間接続の信頼性の低下を抑制する。

【解決手段】熱可塑性樹脂フィルムにて中間層フィルム110と一対の接着層フィルム120、130を形成し、これらフィルムの熱可塑性樹脂フィルムよりも流動性が低い低流動性樹脂フィルムを用いて、一対のパターン層フィルム21、31を形成し、中間層フィルムの第1の層間接続用導電ペースト113の両面に一対の接着層フィルムの第2の層間接続用導電ペースト124、134が対向するようにして一対の接着層フィルムを中間層フィルムの両面に重ね合わ、中間層フィルムと対向しない側の一対の接着層フィルムの面における第2の層間接続用導電ペーストに一対のパターン層フィルムの導体パターン211b,311bが対向するようにして、一対のパターン層フィルムを一対の接着層フィルム上に重ね合わせて積層体を構成し、その後に、積層体に対して加熱プレスを行う。

(もっと読む)

電子部品内蔵基板及びその製造方法

【課題】

部品内蔵多層プリント基板の製造方法であって、半田を用いた内蔵部品実装が安定的に行われることと、部品内蔵基板が再加熱された際の故障を低減できる部品内蔵多層プリント基板の製造方法を得る。

【解決手段】電子部品を内蔵する電子部品内蔵基板において、電子部品を実装する内層基板導体表面に形成された接続端子表面が平滑である。また、接続用端子の表面に粗化処理をほどこさないことを特徴とする。

(もっと読む)

半導体素子搭載用パッケージ基板の製造方法

【課題】埋め込み回路を形成することにより微細で密着力のある外層回路が形成可能であり、しかも任意の箇所に立体回路を形成することによりバンプやピラー、ダミー端子等の種々の導体回路の構成を形成可能な半導体素子搭載用パッケージ基板の製造方法を提供する。

【解決手段】キャリア金属箔とベース金属箔とを積層した多層金属箔を準備し、基材と積層してコア基板を形成する工程と、キャリア金属箔上に第1のパターンめっきを行う工程と、第1のパターンめっき上に絶縁層と導体回路と層間接続と形成して積層体を形成する工程と、積層体をキャリア金属箔とともにコア基板から分離する工程と、分離した積層体のキャリア金属箔上にエッチングレジストを形成してエッチングを行うことにより、埋め込み回路または立体回路を形成する工程と、を有する半導体素子搭載用パッケージ基板の製造方法。

(もっと読む)

電子装置の製造方法及び電子装置

【課題】モールド樹脂の硬化時に、樹脂基板とベアチップとの相対位置が変動することにより、ベアチップの電極パッドと貫通電極とを再配線で接続する際の歩留まりが低下してしまうことのない電子装置の製造方法及び電子装置を提供する。

【解決手段】機能素子が形成されたチップ15を支持体に仮固定するとともに、絶縁部材17を前記支持体に仮固定する。支持体に仮固定したチップ15及び絶縁部材17を、樹脂層16で被覆する。チップ15、絶縁部材17、及び樹脂層16を、支持体から引き離す。絶縁部材17が露出するまで樹脂層16を研磨することにより、チップ15、絶縁部材17、及び樹脂層16からなる再構築ウエハ10を得る。再構築ウエハ10の絶縁部材17に貫通孔を形成し、貫通孔内に貫通電極18を形成するとともに、再構築ウエハ10の上に、チップ15と貫通電極18とを接続する配線21を含む再配線層20を形成する。

(もっと読む)

電子部品モジュール、及び電子部品モジュールの製造方法

【課題】部品の集積化を図りつつ、配線層と内蔵する電子部品との接合部における比抵抗が高くなることを抑制できる電子部品モジュール、及び電子部品モジュールの製造方法を提供すること。

【解決手段】部品内蔵基板10は、絶縁層11上に形成される厚銅パターン12と、絶縁層11の内部に配置されるとともに、銀ナノフィラーNf同士を焼結した金属焼結体からなる接合材16により厚銅パターン12と電気的に接合された電子部品15と、を備えている。

(もっと読む)

部品内蔵印刷配線板及びその製造方法

【課題】チップ部品を確実に保持した、板厚の薄い部品内蔵印刷配線板を得る。

【解決手段】ガラス材入り有機樹脂コア基板の空孔に、平面視が矩形形状であるチップ部品が設置された部品内蔵印刷配線板であって、前記空孔の四隅が、前記チップ部品の4つの角から間隙を開けて形成され、前記空孔の四辺部が前記チップ部品の四辺と平行に密着し、前記空孔から削り取られたガラス材と樹脂の粒子の塊が前記空孔と前記チップ部品との間に集積して前記チップ部品の四辺を前記空孔に強固に保持させ、前記コア基板と前記チップ部品の両面がビルドアップ層で覆われ、前記ビルドアップ層の表面から前記チップ部品の電極端子に達して電気接続する部品電極接続バイアホールが金属めっきで形成された部品内蔵印刷配線板を製造する。

(もっと読む)

複合配線基板

【課題】設計自由度が大きく、かつ多機能、高機能の複合配線基板を提供すること。

【解決手段】上面中央部に電子部品E1を搭載する第1の配線基板1と、この第1の配線基板1の上面に電子部品E1を囲繞する開口部2aを有して接合された第2の配線基板2と、この第2の配線基板2の上面に開口部2aを塞ぐように接合された第3の配線基板3とを備えて成る複合配線基板10であって、開口部2aの内側における第1の配線基板1と第3の配線基板3との間に、第2の配線基板2と異なる層構成または異なる材料から成る第4の配線基板4が接合されている複合配線基板10である。

(もっと読む)

電子部品内蔵基板及びその製造方法

【課題】電子部品の損傷を防止することができ、電子部品と配線との接続部位における電気抵抗を軽減して導電特性を改善することが可能であり、さらにはIC端子と樹脂絶縁層との密着性をも高め得る、電子部品内蔵基板及びその製造方法を提供する。

【解決手段】基板20の上に、電子部品1等を載置し、その上に絶縁層31を設けた後、電子部品1の端子2上の絶縁層31にビアホールVを穿設する。電子部品1の端子2は、例えば、第1金属層201、第2金属層202、及び第3金属層203の積層構造を有している。ビアホールVの形成時には、電気抵抗が比較的高い第3金属層203の一部を除去し、その部位にビア導体を含む配線層を接続する。また、第3金属層203は、絶縁層31との密着性に優れるものを用いることが好ましい。

(もっと読む)

半導体装置内蔵基板モジュール及びその実装構造、並びに、半導体装置内蔵基板モジュールの製造方法

【課題】半導体チップを内蔵した基板モジュールにおいて、当該半導体チップの上面側と下面側に設けられた配線層や電極を導通する構成を設けた場合であっても、基板モジュールの平面サイズを小型化することができるとともに、良好な回路特性を実現することができる半導体装置内蔵基板モジュール及びその実装構造並びにその製造方法を提供する。

【解決手段】半導体装置内蔵基板モジュール10は、コア基板11に設けられた開口部11hに半導体装置20が埋め込まれ、コア基板11の上面側及び下面側に積層配線が設けられている。半導体装置20は、シリコン基板21の上面に形成された集積回路と、シリコン基板21の上面側及び下面側に設けられた配線層25a、25b、外部接続用の柱状電極26a、26b、第1、第2の封止層27a、27bと、シリコン基板21の上面側と下面側を導通し、配線層25a、25bに接続された貫通電極22cと、を有している。

(もっと読む)

配線基板及び半導体装置の製造方法

【課題】アンダーフィル樹脂と半導体素子搭載面となる絶縁層やソルダーレジスト層との間の濡れ性を調整し、アンダーフィル樹脂を充填する時にアンダーフィル樹脂にボイド等発生しないような配線基板を得る。

【解決手段】支持体(20)の表面に粗化処理を施して、粗化面に配線層(25)を形成し、支持体の粗化面と配線層上に誘電体層(23、25)を積層し、このように構成した中間体から支持体を除去し、配線基板を得る。

(もっと読む)

多層プリント配線板、及びその製造方法

【課題】高周波の使用時においてもインピーダンス不整合を回避し、良好な電気的接続を維持し、高周波用の電子機器に使用することが可能な多層プリント配線板を提供する。

【解決方法】互いに離隔するとともに順次に積層されてなる複数の配線層と、前記複数の配線層間それぞれに形成されてなる複数の絶縁層と、前記複数の絶縁層それぞれを貫通し、前記複数の配線層それぞれの間を電気的に接続するように形成されてなる複数の層間接続体と、前記複数の絶縁層の少なくとも一つの内部に埋設され、前記複数の配線層の少なくとも一つと電気的に接続されてなる第1の電子部品と、前記複数の絶縁層の側面によって画定され、積層方向に沿った少なくとも1つの面上において、前記複数の配線層の、前記面に露出した少なくとも1つの端部と電気的に接続するように形成されてなる表面配線層と、を具えるようにして、多層プリント配線板を構成する。

(もっと読む)

電子部品搭載多層配線基板及びその製造方法

【課題】電子部品と配線基板本体との間をワイヤボンディングで電気的に接続した電子部品搭載多層配線基板においても、電子部品の内蔵を可能とし且つ基板の薄肉化を達成する。

【解決手段】電子部品(34)と、電子部品を収容する第1の開口部(16、26)を有するコア材層(10)と、該コア材層の一方の面に積層され且つ前記第1の開口部より大きい第2の開口部(20)を有する樹脂層(18)と、前記コア材層の他方の面に積層され且つ前記電子部品を支持する支持層(30)と、前記第1の開口部の周囲で且つ第2の開口部の内側の前記コア材層の前記一方の面上に配置された複数の接続用導体部(14b)と、前記電子部品と該接続用導体部との間を電気的に接続するボンディングワイヤ(38)と、前記電子部品及び前記ボンディングワイヤを封止するべく前記第1及び第2の開口部内に充填された封止樹脂(40)と、により構成されることを特徴とする。

(もっと読む)

部品内蔵基板及びその製造方法

【課題】適切な放熱対策及びノイズ対策を講じることが可能であると共に、小型化、高密度化を図ることが可能な部品内蔵基板及びその製造方法を提供することを目的とする。

【解決手段】部品内蔵基板1は、パッシベーション膜74が形成されてなる電子部品71と、電子部品71を内蔵する絶縁層25と、パッシベーション膜74から外側に向けて厚み方向に形成されたビア導体26,27と、を備え、ビア導体26は、パッド73に当接すると共に、絶縁層25の外側に設けられている導体22,16,12,28,32,36,42と電気的に接続されており、ビア導体27は、パッシベーション膜74に当接すると共に、絶縁層25の外側に設けられている導体23,17,13と電気的に接続されており、放熱対策及びノイズ対策を講じることのできるように構成されている。

(もっと読む)

回路基板、その製造方法および半導体装置

【課題】平坦かつ高剛性の部品内蔵型回路基板を提供する。

【手段】樹脂シート22b下面に密着し、半導体装置を搭載する搭載領域60直下に開口22d−1を有する第1の銅箔22dと、開口22d−1内に形成され、樹脂シート22bを貫通するビア28と、ビア28下端に接続され、樹脂シート22b下面に配置された電子部品24と、樹脂シート22b下面に密着しかつ電子部品24を包含するモールド樹脂成形体25と、モールド樹脂成形体25が嵌挿される貫通孔21aが設けられた剛性を有するコア板21と、貫通孔21aにモールド樹脂成形体25が嵌挿された前記コア板21を、樹脂シート22b下面に貼着する接着材26と、を備えたコア部材20を有する回路基板120。

(もっと読む)

回路基板の製造方法及び電子装置の製造方法

【課題】電極パッドのピッチ間隔を狭めることのできる回路基板の製造方法及び電子装置の製造方法を提供する。

【解決手段】支持基板30の表面に形成され且つ電子部品の端子を接続させる第1の電極18が埋め込まれた第1の層11を形成する工程と、第1の電極18の表面を露出させるように、第1の層11を研磨する工程と、第1の電極18の表面を露出させた後、第1の層11の表面に、第1の電極18に接続される第1の配線12を形成する工程と、第1の配線12を形成した後に、支持基板30を除去することにより、第1の電極18の裏面を露出させる工程と、を備える回路基板の製造方法。

(もっと読む)

セラミック多層基板の製造方法

【課題】その製造工程の歩留まりを向上することができるセラミック多層基板を提供する。

【解決手段】複数のグリーンシート(第3のグリーンシート14、第1のグリーンシート15、第2のグリーンシート16、第4のグリーンシート17)を焼成して形成されたセラミック基板部2と、セラミック基板部の内部に配置されたチップ型電子部品3と、を有するセラミック多層基板1の製造方法において、第1のグリーンシート15上にチップ電子部品3を配置し、更に、チップ電子部品3上に第2のグイリーンシート16を配置されているチップ型電子部品−グリーンシート積層体12を準備する積層配置工程を有し、第1のグリーンシート15の焼成時の収縮率と、第2のグリーンシート16の焼成時の収縮率とが異なること、を特徴とするセラミック多層基板の製造方法とした。

(もっと読む)

121 - 140 / 1,788

[ Back to top ]