Fターム[5F004AA04]の内容

半導体のドライエッチング (64,834) | 目的 (7,312) | 選択性の向上 (1,192) | エッチングマスクの改良 (327)

Fターム[5F004AA04]に分類される特許

121 - 140 / 327

表面処理用マスクの製造方法、表面処理方法、光学デバイス、及び粒子含有フィルムの製造方法

【課題】粒子が重なり合うことなく単層配列で存在し、被処理物が大面積であっても品質にバラツキが生じ難く、且つ高速に凹凸加工を施すことができ、量産性及び低コスト化に優れた表面処理用マスク及びその製造方法、表面処理方法並びに当該表面処理方法により処理された基板を持つ光学デバイスを提供すること。また、粒子が重なり合うことなく単層配列して存在した粒子含有フィルム及びその製造方法を提供すること。

【解決手段】フィルムマスクを被処理物表面に配置した後、エッチング処理を施して、被処理物の表面に凹凸を形成するエッチングする表面処理方法に利用される、表面処理用マスクとしてのフィルムマスクを、基材上に結着剤及びゲル化剤を含む第1塗布層と粒子を含む第2塗布層とをこの順で略同時に塗布形成し、前記第1塗布層をゲル化させた後、前記第1塗布層及び前記第2塗布層を乾燥させて、前記フィルムマスクを形成する。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】重ね合わせ露光を行うことなくリソグラフィ・プロセスを用いて、露光装置の解像限界を超えるような微細パターンを形成する。

【解決手段】パターン形成方法は、ウエハW上にネガレジスト3及びより高感度のポジレジスト4を塗布することと、ウエハWのポジレジスト4及びネガレジスト3をライン・アンド・スペースパターンの像で露光することと、ポジレジスト4及びネガレジスト3をウエハWの表面の法線に平行な方向に現像することとを有する。

(もっと読む)

半導体装置の製造方法

【課題】ハードマスクを用いて選択形成したトレンチに、ハードマスクを残した状態でエピタキシャル層を埋め込む際に、結晶欠陥の発生を防ぐとともに、超接合構造を効率良く形成でき、良好な良品率が得られる半導体装置の製造方法を提供すること。

【解決手段】トレンチ4を形成するためのマスクとなるマスク絶縁膜3が少なくとも前記トレンチ形成用開口部6d周辺で、他の部分より薄い膜厚部分を有し、前記トレンチ4にp型エピタキシャル半導体層5を埋め込む前に、前記マスク絶縁膜3の膜厚の薄い部分をエッチングして除去した後に、前記トレンチ4にp型エピタキシャル半導体層5を埋め込む。

(もっと読む)

磁性材料の加工方法及び磁気ヘッドの製造方法

【課題】主磁極を従来よりも微細にすることができる磁性材料の加工方法を提供する。

【解決手段】基板1の上方に、磁性材料を有する磁性体層31を形成し、磁性体層31の上に、塩化された状態での沸点が磁性材料の塩化物の沸点に比べて高い金属を含むマスク35を形成し、塩素系ガスとの化学反応を含むドライエッチング法によりマスク35から露出している領域の磁性体層31をエッチングする工程により、磁気ヘッドの磁極を形成する工程を含む。

(もっと読む)

電極形成方法および半導体素子

【課題】電極パタンを精度よく形成する。

【解決手段】半導体基板の一方面(コンタクト層10)上に、SiO2膜12−1、SiN膜14−1、SiO2膜12−2、およびSiN膜14−2を順に積層した4層の絶縁膜を形成する工程と、それら4層の絶縁膜にコンタクト層10の表面まで貫通するコンタクトホールを形成する工程と、SiO2膜12に対するエッチングレートがSiN膜14に対するエッチングレートより高い薬液(たとえばフッ酸)を用いて、コンタクトホールに露出したSiO2膜12−2の側面をコンタクトホールに露出したSiN膜14−2の側面より所定長だけ後退させる工程と、コンタクトホールに露出したコンタクト層10上に、SiN膜14−2に当接しない厚さを有する電極層20−1を蒸着により形成する工程と、上記薬液を用いて、SiN膜14−2をSiO2膜12−2とともに除去する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法、並びにプラズマエッチング装置

【課題】化合物半導体をエッチングにより加工して高アスペクト比の微細構造を高精度に形成し得る半導体装置の製造方法を提供する。

【解決手段】この製造方法は、インジウムおよびリンを必須の構成元素とする化合物半導体からなる被加工物10上にエッチングマスク11pを形成する工程と、エッチングマスク11pの形成後、プラズマエッチング装置のチャンバ内に配置された被加工物10の上に、ヨウ化水素ガスおよび塩素ガスの2成分からなる混合ガスを導入しこの混合ガスをプラズマ化する工程と、当該プラズマ化された混合ガスを被加工物10に入射させて被加工物10を選択的にエッチングする工程とを含む。ヨウ化水素ガスおよび塩素ガスの2成分の総流量に対するヨウ化水素ガスの流量の配合比が70%以上である。

(もっと読む)

半導体素子のパターンの形成方法

【課題】微細なパターンを形成するための半導体素子のパターンの形成方法を提供する。

【解決手段】エッチング対象膜上にフォトレジストパターンが形成された半導体基板が提供される段階と、前記フォトレジストパターンを含む前記半導体基板上に補助膜が形成される段階と、前記フォトレジストパターンの表面に形成された前記補助膜が変性されて第1補助パターンが形成される段階と、前記第1補助パターン及び前記補助膜を含む前記半導体基板上にフォトレジスト膜が形成される段階と、前記フォトレジスト膜の下部に形成された前記補助膜が変性されて第2補助パターンが形成され、前記補助膜が前記フォトレジストパターンの間のみに残留される段階と、前記フォトレジスト膜、前記第1及び第2補助パターンを除去して前記フォトレジストパターン及び前記補助膜を含むエッチングマスクパターンを形成する段階と、を含む。

(もっと読む)

適応型の自己整合型ダブルパターニングのためのシーケンス内計測ベースのプロセス調整

適応型自己整合型デュアルパターニングのための装置及びその方法である。この方法は、エッチングプロセス及び堆積プロセスを実行するために構成された処理プラットホーム及び真空内クリティカルディメンジョン(CD)測定のために構成された計測ユニットに基板を提供するステップを含む。真空内CD測定は、プロセスシーケンス処理プラットホームのフィードフォワード適応制御のために、又はチャンバプロセスパラメータのフィードバック及びフィードフォワード適応制御のために使用される。一態様では、多層マスキングスタックの第1層は、テンプレートマスクを形成するためにエッチングされ、テンプレートマスクの真空内CD測定が行われ、テンプレートマスクのCD測定に依存する幅でテンプレートマスクに隣接してスペーサが形成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】、デュアルダマシン法により低誘電率膜に埋め込まれた配線層を形成する場合において、オープン不良の発生を伴うことなく、設計通りの配線層を形成し得る半導体装置の製造方法を提供する。

【解決手段】ビアホール形成領域の低誘電率膜42、第1のハードマスク44及び第2のハードマスク46を除去することにより、低誘電率膜42にビアホール52を形成する工程と、配線トレンチ形成領域の第2のハードマスク46を除去する工程と、第2のハードマスク46をマスクとして第1のハードマスク44をエッチングすることにより、配線トレンチ形成領域の第1のハードマスク44を除去する工程とを有し、配線トレンチ形成領域の第1のハードマスク44を除去する工程では、ビアホール52底のバリア膜40をもエッチングすることにより、ビアホール52底のバリア膜40を部分的に除去する。

(もっと読む)

フォトレジスト用化合物、フォトレジスト液、ならびにこれを用いるエッチング方法およびポジ型耐エッチングレジスト材料

【課題】フォトリソグラフィを利用した微細加工を行うために使用される新規なフォトレジスト用化合物、それを用いたフォトレジスト液、およびその液を使用するエッチング方法の提供。

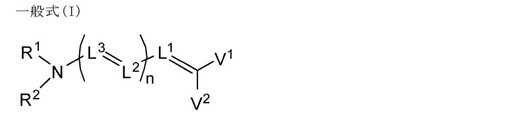

【解決手段】一般式(I)で表される化合物またはその塩であるフォトレジスト用化合物。

[R1およびR2はHまたは置換基、L1〜L3は置換基を有していてもよいメチン基を表し、V1およびV2は少なくとも一方はハメットの置換基定数σpが0.2〜0.9の範囲の置換基、またはV1およびV2が窒素を含有するへテロ環を形成してもよく、nは0または1を表す。]

(もっと読む)

半導体装置の製造方法

【課題】膜パターンが倒れないように半導体装置を製造する方法を提供する。

【解決手段】半導体装置の製造方法は、基板上にSiO2膜の膜パターンを形成する工程と、SiO2膜の膜パターンを両側面から挟むように複数のSi膜の膜パターンを形成する工程と、SiO2膜の膜パターンの上面と、複数のSi膜の膜パターンの上面と露出した側面とを被覆するようにレジスト膜を形成する工程と、SiO2膜の膜パターンの上面が露出するまでレジスト膜の一部を除去する工程と、レジスト膜が除去された後に、露出したSiO2膜の膜パターンをウェット処理により除去する工程と、SiO2膜の膜パターンが除去された後に、レジスト膜の残部をドライ処理により除去する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】研磨粒子によるパターン形成不良を抑制して、高い歩留まりでデュアルダマシン配線を形成可能な半導体装置の製造方法を得ることを目的とする。

【解決手段】本発明における半導体装置の製造方法は、半導体基板1の上面上に絶縁膜6、配線溝パターン8を形成したハードマスク7を形成する。次に、配線溝パターン8を埋め込むように第1のレジスト膜9を形成し、ハードマスク7上の第1のレジスト膜9を除去して平坦化する。次に、第1のレジスト膜9の表面を除去し、第1のレジスト膜9の表面を洗浄する。次に、接続孔パターン14を形成した第2のレジスト膜13を形成し、第1のレジスト膜9および絶縁膜6の表層に接続孔パターン14を転写する。次に、ハードマスク7の配線溝パターン8をマスクとして、絶縁膜6をエッチングして配線溝8および接続孔14を形成する。次に、絶縁膜6に形成された配線溝8および接続孔14に金属を埋め込む。

(もっと読む)

基板の粗面化方法、光起電力装置およびその製造方法

【課題】基板の材質に依らずに基板表面の均一な粗面化が可能な基板の粗面化方法、光起電力装置の製造方法および光起電力装置を得る。

【解決手段】基板の一面側の表面にマスク膜を形成する第1工程と、表面に凹凸形状を有するモールドを用いて型押しを行うことにより前記モールドの凹凸形状を前記マスク膜に転写する第2工程と、前記マスク膜を前記基板の面内方向に略垂直な方向からドライエッチングにより除去する第3工程と、前記マスク膜の除去後に、前記基板の表面に対して前記基板の面内方向に略垂直な方向からドライエッチングを行う第4工程と、を含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】微細ピッチのパターンを実現可能であってパターニング精度の安定性を向上できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上の一部の領域に第1のホトレジストパターンを形成する第1の工程と、2種以上の原料ガスを交互に基板へ供給して、少なくとも第1のホトレジストパターンの表面に薄膜を堆積する第2の工程と、第1のホトレジストパターンが形成されていない領域の一部に第2のホトレジストパターンを形成する第3の工程と、

を有する。

(もっと読む)

プラズマ処理方法及びコンピュータ読み取り可能な記憶媒体

【課題】簡便かつ効果的なレジスト改質法によりレジストパターンのエッチング耐性を強化して、薄膜加工の精度・安定性を向上させる。

【解決手段】チャンバ10内で上部電極(シャワーヘッド)60より吐出された処理ガスが両電極12,60間で高周波放電により解離・電離してプラズマPRが生成される。ここで、可変直流電源80より直流電圧VDCを負極性の高圧で上部電極60に印加する。そうすると、γ放電によって電極板62より放出された2次電子e-は、上部イオンシースSHUの電界でイオンとは逆方向に加速されてプラズマPRを通り抜け、さらに下部イオンシースSHLを横断して、サセプタ12上の半導体ウエハW表面のレジストパターン100に所定の高エネルギーで打ち込まれる。

(もっと読む)

エッチングマスク形成方法、エッチング方法、および半導体デバイスの製造方法

【課題】プロセス数の低減が可能であり、プロセスの単純化が容易なエッチングマスク形成方法を提供する。

【解決手段】エッチングの対象となる対象層10上に、対象層10をエッチングするためのエッチングマスクを形成するマスク膜12を形成し、マスク膜12に転写されるべき第1のパターンを有する第1のマスク層16a,20をマスク膜12上に形成し、マスク膜12に転写されるべき第2のパターンを有する第2のマスク層22a,24を第1のマスク層上に形成し、第2のマスク層の第2のパターンを第1のマスク層に転写して、第1のパターンおよび第2のパターンを有する第3のマスク層を形成する第3のマスク層形成工程と、第3のマスク層を用いてマスク膜をエッチングして、対象層のエッチングに使用されるエッチングマスクを形成するエッチングマスク形成工程と、を含むエッチングマスク形成方法が提供される。

(もっと読む)

シリコン構造体の製造方法

【課題】高アスペクト比のホールやトレンチの多段構造を高い加工精度で容易に形成することができるシリコン構造体の製造方法を提供する。

【解決手段】シリコンからなる基材1に凹部4の一部である初期凹部4aを形成する初期凹部形成工程と、初期凹部4aの内側面42aに保護膜5aを形成する保護膜形成工程と、内側面42aの保護膜5aを残存させた状態で、初期凹部4a及び初期凹部4aに隣接する周回領域4Rの基材1を深さD1,D2方向に異方性エッチングするエッチング工程と、残存させた保護膜5aを除去して凹部4の全体を形成し、凹部4の内側に深さD1,D2方向の段差41gを形成する保護膜除去工程と、を有することを特徴とする。

(もっと読む)

金属配線の製造方法、TFTの製造方法、及びそれを用いて製造されたTFT

【課題】生産性が向上し、かつ寸法精度が良い金属配線の製造方法、TFTの製造方法、及びそれを用いて製造されたTFTを提供すること。

【解決手段】本発明にかかる金属配線の製造方法では、まず、主成分金属に、主成分金属より酸化物の生成エネルギーが低い添加金属が添加された第2の金属膜30を成膜する。そして、第2の金属膜30を酸化させて金属酸化物を形成し、第2の金属膜30の表面に酸化層32を形成する。次に、酸化層32上にフォトレジスト31を形成して、第1のドライエッチング条件により、酸化層32をエッチングする。そして、第1のドライエッチング条件の場合と比較して、主成分金属の金属酸化物に対する選択比が高い第2のドライエッチング条件により、下層の第2の金属膜30をエッチングする。

(もっと読む)

半導体デバイスの製造方法、製造装置、コンピュータプログラム、及びコンピュータ可読記憶媒体

【課題】寸法を制御すべき部位の寸法調整を可能とする半導体デバイスの製造方法、この方法に好適な半導体デバイスの製造装置を提供する。

【解決手段】開示される半導体デバイスの製造方法は、寸法を制御すべき部位の寸法を測定する寸法測定工程S8;寸法測定工程S8において得られた測定値が基準値よりも大きいか否かを判定する判定工程S9、S11;および判定工程S9、S11において測定値が基準値よりも大きいと判定された場合に部位を縮小する第1の工程と、判定工程において測定値が基準値よりも小さいと判定された場合に部位を増大する第2の工程とのいずれかを行う寸法調整工程;を含む。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】半導体素子の微細パターン形成方法を提供する。

【解決手段】被エッチング膜を備える基板上のセルブロック340内に第1方向に延びる第1部分542と、第1部分542と一体に形成されて第1方向とは異なる第2方向に延びる第2部分544と、をそれぞれ備える複数のモールドマスクパターン540を相互平行に配列されるように形成して、モールドマスクパターンブロック540Aを形成するステップと、基板上に複数のモールドマスクパターン540それぞれの両側壁及び上面を覆う第1マスク層を形成するステップと、第1マスク層のうち相互隣接する2個のモールドマスクパターン540間で、モールドマスクパターン540の側壁を覆っている第1マスク層の第1領域は残り、第1マスク層を一部除去して第1マスクパターンを形成するステップと、を含む半導体素子の微細パターン形成方法。

(もっと読む)

121 - 140 / 327

[ Back to top ]