Fターム[5F004AA04]の内容

半導体のドライエッチング (64,834) | 目的 (7,312) | 選択性の向上 (1,192) | エッチングマスクの改良 (327)

Fターム[5F004AA04]に分類される特許

41 - 60 / 327

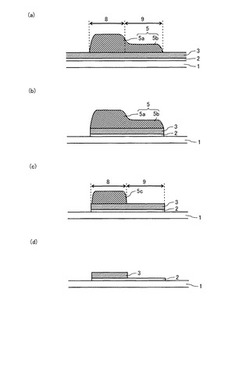

多層薄膜パターン及び表示装置の製造方法

【課題】間便に所望の形状のパターンを得ることのできる多層薄膜パターン及び表示装置の製造方法を提供すること。

【解決手段】基板上に層間絶縁膜1を形成する工程と、層間絶縁膜1上に導電性を有する第1の薄膜2を形成する工程と、第1の薄膜2上に第2の薄膜3を形成する工程と、第2の薄膜3上に、複数階調露光によって膜厚差を有するレジストパターン5を形成する工程と、膜厚差を有するレジストパターン5を介して、第2の薄膜3及び第1の薄膜2をエッチングして、レジストパターンの存在しない領域の層間絶縁膜1を露出させる工程と、膜厚差を有するレジストパターン5をアッシングして、レジストパターンの薄膜部5bを除去する工程と、薄膜部5bが除去されたレジストパターン5cを介して、第2の薄膜3をエッチングする工程と、を順次実施する。

(もっと読む)

側壁イメージ転写からパターンを作る改善された方法

【課題】実施の容易な、側壁イメージ転写により部分的に定義されるパターンを生成する方法を提供する。

【解決手段】基板1には、第1の材料2の層と、第1のエッチングマスク4と、カバリング層3と、第2のエッチングマスクとが設けられている。カバリング層3は、覆われた主領域と、覆われていない副領域とを有する。カバリング層3の副領域は、第2のエッチングマスクを介して部分的にエッチングされ、突出パターンが形成される。第3のエッチングマスクを定義する突出パターンの周囲に、横スペーサが形成される。第2のエッチングマスクは除去される。カバリング層3は、第3のエッチングマスクを用いてエッチングされ、カバリング層3における突出パターンが形成され、第1のエッチングマスク4および第1の材料2が露出される。第1の材料2の層は、エッチングされ、第1の材料2から作られるパターンが形成される。

(もっと読む)

半導体素子の作製方法

【課題】半導体の構成原子の脱離による欠陥(V族原子空格子)の誘起または表面モフォロジーの劣化を生じさせずに、同一面内でエッチング深さが異なる形状を容易に加工することができる半導体素子の作製方法を提供する。

【解決手段】開口部幅の異なる複数の開口部を有するマスクを半導体層1801の表面上に形成し、開口部幅が同じ開口部毎に、前記マスク端での酸素プラズマ濃度が所定の濃度となるようにプラズマ条件(拡散距離または圧力)とマスク形状(開口部幅)を設定してエッチング(メタン/酸素プラズマ照射)を行い、同一面内でエッチング深さが異なる形状を加工する。

(もっと読む)

半導体素子の作製方法

【課題】エッチング面積を変えずにマスク面積を小さくする、同一面内でエッチング深さが異なる形状を容易に加工することができる半導体素子の作製方法を提供すること。

【解決手段】エッチングされる領域のマスク端からの距離は、マスク幅が1μm以上でほぼ一定の値を示す。このことは、マスク上のマスク端から1μmまでの領域に存在する水素プラズマが開口部に拡散してエッチングに寄与することを示す。このとき、マスク上のマスク端から1μm以上の領域に存在する水素プラズマはエッチングに寄与することなくマスク上から脱離するものと考えられる。そのため、本発明の選択エッチングにおいてはマスクの幅は1μm以上あればエッチング領域のマスク端からの距離を十分に得られる。また、半導体素子の高密度集積における素子間隔が10μm程度であることを考慮すると、マスク幅は1μm以上10μm以下で有効である。

(もっと読む)

複数のマスキングステップを用いて微小寸法を低減する方法

【課題】エッチングレイヤ中にフィーチャを形成する方法を提供する。

【解決手段】エッチングレイヤ上に第1マスクが形成され、第1マスクは幅を持つ複数のスペースを規定する。第1マスク上に側壁レイヤが形成され、側壁レイヤは、第1マスクによって規定されるスペースの幅を低減する。側壁レイヤを通してエッチングレイヤにフィーチャがエッチングされ、フィーチャは、第1マスクによって規定されるスペースの幅よりも小さい幅を有する。マスクおよび側壁レイヤが除去される。エッチングレイヤ上に追加マスクが形成され、追加マスクは幅を持つ複数のスペースを規定する。追加マスク上に側壁レイヤが形成され、側壁レイヤは、追加マスクによって規定されるスペースの幅を低減する。側壁レイヤを通してエッチングレイヤにフィーチャがエッチングされ、フィーチャは、追加マスクによって規定されるスペースの幅よりも小さい幅を有する。マスクおよび側壁レイヤが除去される。

(もっと読む)

半導体装置の製造方法

【課題】 接続孔のホールサイズについて制御性良い半導体装置の製造方法を提供する。

【解決手段】 実施形態の半導体装置の製造方法では、半導体基板上に上層絶縁膜が形成され、前記上層絶縁膜上にSiを含む非晶質膜が形成される。前記非晶質膜上に第1のレジスト膜が形成され、前記第1のレジスト膜に第1のレジストパターンが形成される。前記第1のレジスト膜をマスクとして、前記非晶質膜が加工され、前記上層絶縁膜が露出される。前記第1のレジストパターンが除去され、前記非晶質膜および露出した前記上層絶縁膜上に遷移金属膜が形成される。前記非晶質膜および前記遷移金属膜の熱反応により、前記非晶質膜よりも体積が大きいシリサイド膜が形成される。前記遷移金属膜が除去され、前記シリサイド膜をマスクとして、前記上層絶縁膜を加工し、前記上層絶縁膜に第1の溝が形成される。

(もっと読む)

ガスクラスターイオンビームによる固体表面の加工方法

【課題】凹凸構造の角部分の形状変形を防いで固体表面の加工を行う。

【解決手段】上部にクラスター保護層が被覆形成された凸部とクラスター保護層が被覆形成されない凹部とでなる凹凸構造を固体表面に形成するクラスター保護層形成工程と、クラスター保護層形成工程において凹凸構造が形成された固体表面に対してガスクラスターイオンビームを照射する照射工程と、クラスター保護層を除去する除去工程とを有するガスクラスターイオンビームによる固体表面の加工方法とする。ガスクラスターイオンビームのドーズ量をn、クラスター保護層のエッチング効率を1クラスターあたりのエッチング体積Yとした場合に(但しa及びbは定数)、クラスター保護層の厚さTは、

を満たす。

(もっと読む)

プラズマ処理方法

【課題】200〜500nmの厚さの磁性膜を高速エッチングし、良好な微細加工が可能なドライエッチング方法を提供することである。

【解決手段】本発明は厚さが200nmから500nmの磁性膜をドライエッチングするプラズマ処理方法において、レジスト膜と、前記レジスト膜の下層膜である非有機系の膜と、前記非有機系の膜の下層膜であるCr膜と、前記Cr膜の下層膜であるAl2O3膜とを含む積層膜を前記磁性膜の上に成膜した試料をドライエッチングすることを特徴とするプラズマ処理方法である。

(もっと読む)

プラズマエッチング処理装置、プラズマエッチング処理方法、および半導体素子製造方法

【課題】より正確に所望の形状にエッチングすることができるプラズマエッチング処理装置を提供する。

【解決手段】プラズマエッチング処理装置11は、その内部において被処理基板にプラズマ処理を行う処理容器12と、処理容器12内にプラズマ処理用のガスを供給するガス供給部13と、処理容器12内に配置され、その上に被処理基板Wを支持する支持台14と、プラズマ励起用のマイクロ波を発生させるマイクロ波発生器15と、マイクロ波発生器15により発生させたマイクロ波を用いて、処理容器12内にプラズマを発生させるプラズマ発生手段と、処理容器12内の圧力を調整する圧力調整手段と、支持台14に交流のバイアス電力を供給するバイアス電力供給手段と、バイアス電力供給手段における交流のバイアス電力を、停止および供給を交互に繰り返しながら行うよう制御する制御手段とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】可能な限り従来の設備及び加工プロセスを継承してコストの上昇を抑制するも、Ta含有の導電材料を難除去性の残留付着物を発生せしめることなく所望に加工し、容易且つ確実に信頼性の高い半導体装置を実現する。

【解決手段】半導体基板上に、Ta含有層、TiN層、及び多結晶シリコン膜等のドライエッチング可能な層を順次積層し、TiN層をエッチングストッパーとして多結晶シリコン膜をドライエッチングして所定形状に残し、TiN層及びTa含有層をSPM、APM等を用いてウェットエッチングして多結晶シリコン膜下で所定形状に残す。

(もっと読む)

エッチング方法

【解決手段】透明基板上に形成された1又は2以上の層で構成された膜であり、該膜の最表層がクロム系材料からなる膜を塩素系ドライエッチングによってエッチングする方法であって、加水分解性シラン化合物の加水分解・縮合物、架橋促進剤化合物及び有機溶剤を含む酸化ケイ素系材料膜形成用組成物を用いて成膜した膜厚1〜10nmの酸化ケイ素系材料膜をエッチングマスクとして上記最表層を塩素系ドライエッチングする方法。

【効果】本発明のエッチングマスク膜は、塩素系ドライエッチングに対して高いエッチング耐性をもち、このエッチングマスク膜を用いてフォトマスクブランクを加工することにより、塩素系ドライエッチングであっても、薄いエッチングマスク膜で高精度の加工が可能である。

(もっと読む)

キャパシタ構造体およびその製造方法

【課題】シリコン基板に設けられた穴の内部に導電体と誘電体を配置することにより、キャパシタを構成してなるキャパシタ構造体において、穴をより深くしたり、穴の平面形状を複雑な形状とすることなく、導電体間の対向面積を増加させて容量値の増大が実現できるようにする。

【解決手段】穴20は、シリコン基板10の一方の主面に開口する有底穴であり、穴20の内部にはシリコン基板10よりなる突起21が設けられ、穴20の底面は、突起21による凹凸面とされており、穴20の内部では、穴20の底面および側面に、これらの面側から第1の導電体31、誘電体40、第2の導電体32が順次積層されているとともに、第1の導電体31および誘電体40は、突起21による凹凸面の形状を承継した層形状とされている。

(もっと読む)

ドライエッチング装置、ドライエッチング方法及びフォトマスク製造方法

【課題】任意の領域のみをエッチング処理ができるドライエッチング装置、ドライエッチング方法およびフォトマスク製造方法を提供する。

【解決手段】カソード22上に載置された被エッチング材料10に対して、被エッチング材料10に対向するアノード23からプラズマを発生させてエッチングするドライエッチング装置において、被エッチング材料10とアノード23との間に配置され、プラズマを通過させる開口の大きさを変更可能なシャッター30を設け、シャッター30は、被エッチング材料に対して離間接近する方向に対して直交する方向に移動可能に配置された複数のプレート30aと、各プレート30aを移動可能支持する支持体29と、プレート30を移動させる第1移動手段301を備える構成にした。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造欠陥の少ない、様々な大きさの要素を有する装置の製造方法を提供する。

【解決手段】基板上に、基板上の下側誘電体層(530)、下側誘電体層上の金属層(520)、金属層上の上側誘電体層(510)、上側誘電体層上の平坦化層(140)、平坦化層上のフォトレジスト材料(130)の層を有する構造が形成される。マスク・パターンに従ってフォトレジスト材料が現像される。マスク・パターンに従って平坦化層および上側誘電体層がエッチングされる。平坦化層および上側誘電体層のエッチングの後にフォトレジスト材料および平坦化層が除去される。上側誘電体層のエッチングに続いて金属層の各露出した部分に選択的金属成長を適用して選択的金属成長からなる反転されたマスク・パターンが得られる。反転されたマスク・パターンに従って少なくとも金属層および下側誘電体層がエッチングされる。

(もっと読む)

光電変換素子用シリコン基板及び光電変換素子の製造方法。

【課題】光電変換層への太陽光の入射効率の良好であり、光電変換効率の高い光電変換素子を製造可能な光電変換素子用シリコン基板を歩留まり良く製造する。

【解決手段】一導電型結晶シリコン基板10の一主面10sに、ドライエッチングに対して耐性を有し、且つ、平均粒径が0.05μm〜0.3μmである第1粒子と、第1粒子よりも耐性が低く、且つ、平均粒径が0.05μm〜0.3μmである第2粒子と、第1粒子よりも耐性が低い結着剤とを含む液状組成物を塗布成膜してマスク材を配する工程と、マスク材が配された主面10sにドライエッチングにより太陽光の反射を抑制する凹凸構造10tを形成する工程と、凹凸構造10tに、水素ガスによるドライエッチング処理と、希フッ酸中に浸漬させる処理を順次実施する洗浄工程とを実施する。

(もっと読む)

無機化合物膜のエッチング方法および半導体光素子の製造方法

【課題】反転NIL技術を使用した無機化合物膜のエッチング方法および半導体光素子の製造方法において、エッチングマスクのラインエッジラフネスを向上させる。

【解決手段】この方法は、基板生産物30上に形成された絶縁膜25上に樹脂層27を形成したのち、所定パターンを有するモールドを樹脂層27に押し付ける工程と、Siを含む樹脂層28によって樹脂層27を覆ったのち、CF4ガス及び酸素ガスを用いたRIEによって樹脂層28をエッチングして樹脂層27を露出させるエッチバック工程と、樹脂層27を選択的にエッチングして絶縁膜25を露出させる工程と、樹脂層28をマスクとして絶縁膜25をエッチングすることにより、所定パターンを絶縁膜25に形成する工程とを含む。RIEは、自己バイアスを印加しながら行うことにより、エッチングにより生じるSi生成物を除去しながら行われる。

(もっと読む)

半導体装置の製造方法

【課題】マスクの新規な作製技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、第1の膜を形成する工程と、第1の膜上方に、第1マスク膜を形成する工程と、第1マスク膜をパターニングする工程と、パターニングされた第1マスク膜の側部にプラズマ処理を行って、側部を変質層に変換する工程と、プラズマ処理の後、第1マスク膜の上部及び側部を覆う第2マスク膜を形成する工程と、第2マスク膜をエッチングして、側部に形成された第2マスク膜を残存させつつ、第1マスク膜上部に形成された第2マスク膜を除去する工程と、第2マスク膜のエッチングの後、変質層を除去する工程と、変質層を除去した後、残った部分の第1マスク膜、及び第2マスク膜をマスクとして、第1の膜をエッチングする工程とを有する。

(もっと読む)

微細パターンの形成方法

【課題】側壁部の形成の基礎となるパターンをレジストにより形成する場合であっても、側壁部の傾きを抑制できる微細パターンの形成方法を提供する。

【解決手段】基板上に形成されたエッチング対象層の上に有機膜を形成する有機膜形成ステップと、有機膜上にレジスト膜を形成し、このレジスト膜をパターニングするパターニングステップと、パターニングされたレジスト膜から露出する有機膜と、パターニングされたレジスト膜とを覆うように酸化シリコン膜を常温にて堆積する堆積ステップと、基板を加熱して酸化シリコン膜に引っ張り応力を生じさせる加熱ステップと、処理ステップの後に、パターニングされたレジスト膜の側壁に酸化シリコン膜が残るように当該酸化シリコン膜をエッチングする第1のエッチングステップと、パターニングされたレジスト膜を除去する除去ステップとを含む、微細パターンの形成方法が開示される。

(もっと読む)

半導体装置の製造方法

【課題】加工膜と非加工膜をRIE法で選択的に加工するときに、非加工膜の加工量を低減させる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1,7,8の上に非加工膜14を形成する工程と、非加工膜14および下地層1,7,8に溝4を形成する工程と、溝内を埋め込むように加工膜5を形成する工程と、非加工膜14を露出させるように加工膜5を平坦化する工程とを備える。更に、加工膜5および非加工膜14の上に保護膜16を形成する工程と、RIE法を用いて、保護膜16をエッチングすると共に、加工膜5を選択的にエッチングして溝内の加工膜5を落とし込む工程とを備える。

(もっと読む)

41 - 60 / 327

[ Back to top ]