Fターム[5F004DB13]の内容

半導体のドライエッチング (64,834) | 被エッチング物 (6,778) | 金属化合物 (585) | 金属酸化物 (298)

Fターム[5F004DB13]の下位に属するFターム

Al2O3 (75)

Fターム[5F004DB13]に分類される特許

101 - 120 / 223

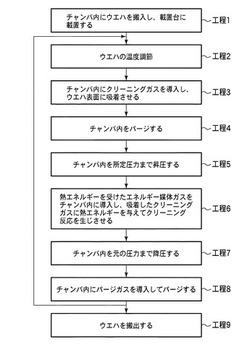

ドライクリーニング方法および基板処理装置

【課題】基板に熱による悪影響を与えず、基板を効率良く加熱して基板表面のドライクリーニングを行うことができ、装置上の問題も生じないドライクリーニング方法を提供すること。

【解決手段】減圧排気可能な処理室内に設けられた載置台に基板を載置し、基板表面をドライクリーニングするドライクリーニング方法は、処理室内にクリーニングガスを導入し、クリーニングガスを基板上に吸着させる工程と、クリーニングガスを基板上に吸着させた後、処理室内に、熱エネルギーが与えられたエネルギー媒体ガスを導入し、該エネルギー媒体ガスから基板上の前記クリーニングガスに熱エネルギーを供給して、前記基板表面でクリーニング反応を進行させる工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜に設けたホールパターンに形成された導電体膜の断線を防止できる構造を備えた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、第1の導電体膜上に絶縁膜を形成し、絶縁膜を露出する開口部を有するマスク膜を用いた異方性エッチングにより、開口部に露出した絶縁膜の上部に凹部を形成すると共に、マスク膜の側壁部下部に反応生成物を付着させる。次に、等方性エッチングにより、マスク膜の側壁部を水平方向に後退させると共に、異方性エッチングにより、凹部の底部に露出した絶縁膜を垂直方向に掘り下げながら、マスク膜の側壁部下部に付着した反応生成物を除去する。次に、異方性エッチングにより、凹部の周囲に存在する絶縁膜を鉛直方向に掘り下げて段差部を形成すると共に、凹部の底部を貫通させて第1の導電体膜を露出させる。その後、第1の導電体膜の上に第2の導電体膜を形成する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】処理室の内面等に付着したHfO2、HfSiO,ZrO2等の高誘電体膜をエッチングガスによりクリーニングできる半導体装置の製造方法を提供する。

【解決手段】基板30を処理室4内に搬入する工程と、前記処理室4内で基板30上に高誘電体膜を成膜する工程と、成膜後の基板を前記処理室4より搬出する工程と、前記処理室4内に塩素を含むガスと酸素を含むガスとを導入するかもしくは塩素および酸素を含むガスを導入して前記処理室4内をクリーニングする工程と、前記処理室4内に酸素を含むガスを導入して前記クリーニング後に前記処理室4に残留する物質を除去する工程と、を有する。

(もっと読む)

ZnO系基板及びZnO系基板の処理方法

【課題】結晶成長に適した品質の良い表面を有するZnO系基板及びZnO系基板の処理方法を提供する。

【解決手段】

ZnO系基板の結晶成長側の主面表面のカルボキシル基又は炭酸基の存在を略0にするように構成している。また、カルボキシル基又は炭酸基の存在を略0にするために、結晶成長開始前にZnO系基板表面を酸素ラジカル、酸素プラズマ、オゾンのいずれかに接触させるようにしている。したがって、ZnO系基板表面の清浄化を高め、基板上に品質の良いZnO系薄膜を作製することができる。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ特性の良好なスタック型の強誘電体キャパシタを有する半導体装置の製造方法を提供すること。

【解決手段】チャンバー53内においてマスク25を使用して上部電極膜24、強誘電体膜19、下部電極膜18までをエッチングしてキャパシタ40を形成した後に、下部電極膜19のエッチング時に比べて副生成物量の付着量が少なくなるようにクリーニングされたチャンバー53内でキャパシタ側壁をオーバーエッチングし、これにより、キャパシタ40の底面に対するキャパシタ側壁の角度を、オーバーエッチング前に比べてオーバーエッチング後に大きくする工程を含んでいる。

(もっと読む)

半導体製造方法および半導体製造装置

【課題】プラズマの不均一を改善することにより、プラズマダメージを抑え、得られる半導体素子の性能や製品歩留りの劣化を抑えることが可能な半導体製造方法と半導体製造装置を提供する。

【解決手段】反応室11内に設けられた下部電極13にウェハwを載置し、反応室11内にプロセスガスを導入し、ウェハwの被処理面と離間するように磁場を印加し、下部電極13と、下部電極13と対向配置された上部電極12間に高周波電圧を印加してプラズマを発生させ、プラズマが安定化した後、磁場を除去し、ウェハwをプラズマ処理することを特徴とする。

(もっと読む)

基板処理方法および半導体装置の製造方法、コンピュータ可読記録媒体

【課題】Cu膜の露出表面から自然酸化膜を除去する基板処理を、低温で、かつ高いスループットで実行する。

【解決手段】基板処理方法は、Cu膜を担持した被処理基板を、所定温度を維持するように制御された基板保持台上に載置し、前記被処理基板の温度を昇温させる工程と、前記被処理基板表面に、有機化合物を含む処理ガスを供給し、前記Cu膜表面の酸化物を除去する工程と、前記被処理基板を、前記基板保持台から取り出す工程と、を含み、前記処理ガスを供給する工程は、前記被処理基板の温度が昇温している間に開始されることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】所望の形状を有するゲート電極を形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の実施の形態に係る半導体装置の製造方法は、半導体基板上に形成された半導体膜を加工してゲート電極を形成する工程と、HBr、Cl2、CF4、SF6若しくはNF3のうち少なくとも1つおよびO2を含み、O2の流量が全体の流量の合計の80%よりも大きいガス、または、HBr、Cl2、CF4、SF6若しくはNF3のうち少なくとも1つ、O2およびN2を含み、O2およびN2の流量の合計が全体の合計の80%よりも大きいガスのプラズマ放電により、前記ゲート電極の側面に保護膜を形成する工程と、前記保護膜を形成した後、前記半導体基板上の前記半導体膜の残渣を除去する工程と、を含む。

(もっと読む)

半導体素子の製造方法

【課題】製造コストを低減することが可能な半導体素子の製造方法を提供する。

【解決手段】この発明に従った半導体素子の製造方法は、以下の工程:GaN系半導体層形成工程(S10)、GaN系半導体層上にAl膜を形成する工程(S20)、エッチング速度が、Al膜を構成する材料より小さい材料からなるマスク層を形成する工程(S30、S40)、マスク層をマスクとして用いて、Al膜およびGaN系半導体層を部分的に除去することにより、リッジ部を形成する工程(S50)、Al膜の端面の側壁の位置をマスク層の側壁の位置より後退させる工程(S60)、エッチング速度が、Al膜を構成する材料より小さい材料からなる保護膜を、リッジ部の側面およびマスク層の上部表面上に形成する工程(S70)、Al膜を除去することにより、マスク層および当該マスク層の上部表面上に形成された保護膜の部分を除去する工程(S80)、を備える。

(もっと読む)

強誘電体メモリ装置の製造方法

【課題】水素バリア膜の下層との間においてエッチングの十分な選択比が得られると共に、コンタクトホールの形成工程を簡略化した強誘電体メモリ装置の製造方法を提供すること。

【解決手段】半導体基板上に強誘電体キャパシタ3を形成する工程と、強誘電体キャパシタ3を被覆する水素バリア膜12を形成する工程と、水素バリア膜12を被覆する層間絶縁膜13を形成する工程と、C4F8ガススとO2ガスとを少なくとも含む混合ガスを用いたエッチングにより層間絶縁膜13及び水素バリア膜12を貫通する貫通孔21を形成する工程とを備え、C4F8ガスの流量がO2ガスの流量に対して0.77倍以上3.8倍以下である。

(もっと読む)

High−k膜のドライエッチング方法

【課題】

本発明の目的は、High−k膜である金属酸化物を、下地ポリシリコン膜との高い選択性(比)を保ちつつ、パターンの疎部と密部によるエッチング速度差、及び形状差の小さいエッチング特性を有するHigh−k膜のドライエッチング方法を提供することである。

【解決手段】

プラズマを用いHigh−k膜をドライエッチングする方法で、希ガスと混合したBCl3ガスに、炭素元素比率の高いフルオロカーボンガスを微少添加する構成とした。

(もっと読む)

キャパシタの検査方法及び半導体装置の製造方法

【課題】キャパシタにおける誘電体層の特性検査を容易にかつ正確に行うことができるようにしたキャパシタの検査方法と、このキャパシタの検査方法を用いた半導体装置の製造方法とを提供する。

【解決手段】基体上に第1電極膜51a、強誘電体材料膜52a、第2電極膜53aを形成する工程と、第2電極膜53a上にハードマスク60を形成する工程と、ハードマスク60をマスクにして第2電極膜53aと強誘電体材料膜52aとを順次パターニングし、上部電極53と強誘電体層52との積層構造と第1電極膜51aとからなるキャパシタ構造50を形成する工程と、第1電極膜51aと上部電極53との間に電圧を印加し、キャパシタ構造50における強誘電体層52の特性検査を行う工程と、を含むキャパシタの検査方法である。

(もっと読む)

MEMS製造において使用されるエッチングプロセス

希ガスフッ化物、たとえば、二フッ化キセノン(XeF2)を含むエッチャントによって犠牲層をエッチングするステップを含む、電気機械デバイスを作製する方法。エッチングプロセスの効率は、種々の方法で増加する可能性があり、また、エッチングプロセスのコストは減少する可能性がある。未使用エッチャントが、エッチングプロセス中に、単離され、再循環されてもよい。エッチング副生成物は、エッチングプロセス中にエッチングシステムから収集され除去されてもよい。エッチャントの成分は、単離され、一般的な付加的エッチャントに対して使用されてもよい。エッチャントまたはエッチングされる層のいずれかまたは両方が、特定のエッチングプロセスについて最適化されてもよい。  (もっと読む)

(もっと読む)

半導体素子加工方法

【課題】high−k/メタルゲートと呼ばれる構造の素子の微細化に適した加工方法を提供する。

【解決手段】Si基板11上にHfあるいはZrを含む例えばHfSiON絶縁膜12を形成して、その上にTiあるいはTaなどを含む導体膜13と、Wなどを主成分とする導体膜14、キャップSiN層15、BARC16、レジスト17が形成された電極構造をもつ半導体素子を、1Pa以下の圧力領域でエッチングガスに少なくともFを含むガスにて絶縁膜12上の各層13〜17が水平方向にほぼ同じ速度でエッチングされるように、ドライエッチング加工する。

(もっと読む)

半導体装置の製造方法、半導体基板の処理装置、及び記憶媒体

【課題】層間絶縁膜や下層配線に熱ストレスがかかり難くすることが可能な半導体装置の製造方法を提供すること。

【解決手段】酸化銅10が表面に形成された半導体ウエハWをチャンバ内に設置し、チャンバに向けて水素ガスと二酸化炭素ガスとを供給し、半導体ウエハWの表面から酸化銅10を除去する。

(もっと読む)

ドライクリーニング方法、基板処理装置、半導体装置の製造方法及び記憶媒体

【課題】被処理基板中の構造体に熱ストレスが加わり難いドライクリーニング方法を提供すること。

【解決手段】 酸化銅、及び有機汚染物質の少なくともいずれか一方が基板表面に形成、もしくは付着した被処理基板をチャンバ内に設置する工程(ステップ1)と、チャンバ内の雰囲気を有機化合物ガス雰囲気として被処理基板の基板表面にガスクラスターイオンビームを照射し、基板表面に形成、もしくは付着した酸化銅、及び有機汚染物質の少なくともいずれか一方を除去する工程(ステップ2)とを具備する。

(もっと読む)

銅の再付着防止方法、半導体装置の製造方法、基板処理装置及び記憶媒体

【課題】 被処理基板への銅の再付着を防止できる銅の再付着防止方法を提供すること。

【解決手段】 銅含有物質を含む膜が形成された被処理基板をチャンバ内に設置する工程(ステップ1)と、チャンバ内に設置された被処理基板から銅含有物質を、有機化合物を用いたドライクリーニングを用いて除去する工程(ステップ2)と、銅含有物質が除去された被処理基板を前記チャンバから搬出する工程(ステップ3)と、銅含有物質が除去された被処理基板がチャンバ内に無い状態で、このチャンバ内に飛散した銅含有飛散物を被覆する被覆膜をチャンバ内に堆積する工程(ステップ4)と、を具備する。

(もっと読む)

レーザ照射装置、レーザ照射方法、結晶材料、および、機能素子

【課題】巨大結晶を安定して作製する、レーザ照射装置、レーザ照射方法を提供する。

【解決手段】本発明のレーザ照射装置30は、第1レーザ照射手段10と、第2レーザ照射手段20と、被照射物80に対して、第1照射領域2および第2照射領域22からなる一組の照射領域を相対的に移動させる移動手段18とを備え、第2照射領域2は、第1照射領域2と重複する部分を含む重複部22bと、一組の照射領域の相対移動方向における重複部22bよりも先頭側において、第1照射領域2と重複しない未重複部22aとを有している。

(もっと読む)

ヘテロ接合電界効果型トランジスタおよびその製造方法

【課題】空気の層に基づくパッシベーションの膜の不整合性による不連続性の問題を解決し、高耐圧特性に優れたトランジスタの提供を課題とする。

【解決手段】III−V族窒化物からなる半導体層と、その上に、ソース/ドレイン電極と、両サイドを前記ソース/ドレイン電極に挟まれ、かつゲート電極を備えるIII−V族窒化物からなる半導体よりも高い誘電率を有する誘電体膜とが形成されており、前記ゲート電極が、前記誘電体膜の一部を窒化したものであり、さらにセカンドメタルで被覆されていることを特徴とするヘテロ接合電界効果型トランジスタ。

(もっと読む)

高k材料ゲート構造の高温エッチング方法

【課題】高k材料を高温でエッチングする方法を提供する。

【解決手段】一実施形態において、基板上の高k材料をエッチングする方法は、高k材料層をその上に有する基板をエッチングチャンバ内に設置し、少なくともハロゲン含有ガスを含むエッチングガス混合物からプラズマをエッチングチャンバ内に発生させ、プラズマの存在下で高k材料層をエッチングしながらエッチングチャンバの内部表面の温度を約100℃を越えて維持し、プラズマの存在下で高k材料層をエッチングしながら基板温度を約100℃〜約250℃に維持することを含んでいてもよい。

(もっと読む)

101 - 120 / 223

[ Back to top ]