Fターム[5F004EA22]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | 反射防止膜 (216)

Fターム[5F004EA22]に分類される特許

1 - 20 / 216

半導体装置の製造方法

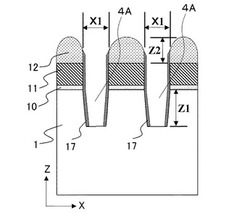

【課題】半導体基板をエッチングする際、ハードマスクの肩落ちによるエッチング深さの基板面内での粗密差を低減する。

【解決手段】半導体基板1上に、絶縁層(10,11)とアッシング除去可能な材料層を形成する工程と、材料層をパターニングする工程と、パターニングされた材料層をマスクに、絶縁層を貫通し、少なくとも半導体基板の一部をエッチングする第1のエッチング工程と、材料層がなくなる前にエッチングを一旦停止し、残存する材料層(12)をアッシング除去する工程と、絶縁層をマスクに半導体基板を所定の深さにエッチングする第2のエッチング工程とを含む。

(もっと読む)

均一性を制御したエッチング

【課題】パターンを形成するエッチングに際してより均一なエッチングを可能にする方法を提供する。

【解決手段】ウエハ上に半導体素子を形成する方法が提供されている。エッチング層が、ウエハの上に形成される104。フォトレジストマスクが、エッチング層の上に形成される108。フォトレジストマスクは、ウエハの外縁付近のみ除去されて、ウエハの外縁付近のエッチング層が露出される112。炭素および水素を含有する種を備えた蒸着ガスが供給される116。蒸着ガスから、プラズマが形成される120。ポリマ層が、ウエハの外縁付近の露出エッチング層に蒸着される124。この時、ポリマは、蒸着ガス由来のプラズマから形成される。フォトレジストマスクと、ウエハの外縁付近の露出エッチング層に蒸着されたポリマとが消費されつつ、フォトレジストマスクを介してエッチング層がエッチングされる128。

(もっと読む)

半導体装置の製造方法

【課題】反射防止膜を確実に除去して半導体装置の欠陥発生を低減する。

【解決手段】第1の層間絶縁膜の上に、絶縁膜と、反射防止膜と、レジスト膜とを順番に形成する。レジスト膜を用いて反射防止膜と絶縁膜をエッチングし、絶縁膜からハードマスクを作成する。この後、ラジカル照射によってレジスト膜と反射防止膜を除去する。ラジカル照射は、基板温度を100℃、150℃、250℃と順番に上昇させながら行う。基板温度が低い初期段階では、反射防止膜の膜材料の飛散防止と、反射防止膜の表面に残留する他の物質の除去が行われる。この後、基板温度を高くすることで、反射防止膜が確実に除去される。

(もっと読む)

アモルファスカーボン膜の成膜方法、それを用いた半導体装置の製造方法、およびコンピュータ読取可能な記憶媒体

【課題】耐プラズマ性が高く、低温成膜が可能なアモルファスカーボン膜の成膜方法、およびそのようなアモルファスカーボン膜の成膜方法を適用した、半導体装置の製造方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器内に炭素と水素と酸素とを含む処理ガスを供給し、処理容器内の基板を加熱して処理ガスを分解して、基板上にアモルファスカーボン膜を堆積する。この方法を半導体製造装置のエッチングマスクの形成に適用して半導体装置を得る。

(もっと読む)

エッチングマスクスタックを用いたマルチマスクプロセス

【課題】基板の上のエッチング層内にエッチング特徴を形成するための方法が提供される。

【解決手段】エッチングマスクスタックが、エッチング層の上に形成される。第1のマスクが、エッチングマスクスタックの上に形成される。第1のマスクによって定められる間隔の幅を低減させる側壁層が、第1のマスクの上に形成される。側壁層を通して、第1組の特徴が、エッチングマスクスタック内へとエッチングされる。マスクおよび側壁層は、除去される。追加の特徴のステップが実施される。該ステップは、追加のマスクをエッチングマスクスタックの上に形成することと、側壁層を追加のマスクの上に形成することと、第2組の特徴を少なくとも部分的にエッチングマスクスタック内へとエッチングすることと、を含む。エッチングマスクスタック内の第1組の特徴および第2組の特徴を通して、複数の特徴がエッチング層内にエッチングされる。

(もっと読む)

処理液選定方法、及びマスクブランクの製造方法、並びにマスクの製造方法

【課題】マスクの微小黒欠陥の発生要因となる潜在化したマスクブランク欠陥の発生を抑制できる、最適な処理液を選定する方法を提供する。

【解決手段】ドライエッチングが可能な材料からなる転写パターンとなる薄膜を有するマスクブランクを複数枚準備する工程1と、エッチング阻害物質の濃度が異なる複数種の処理液を準備する工程2と、前記処理液を用いて表面処理する工程3と、前記表面処理をしたマスクブランクに対して、ドライエッチングして除去した後、該エッチング後の前記基板表面の表面形態情報を取得する工程4と、前記エッチング阻害物質の濃度と、前記基板表面の表面形態情報との対応関係を作成した対応関係の中から所望の仕様又は品質を満足する表面形態情報を選択して、対応するエッチング阻害物質の濃度を特定する工程5と、該特定した濃度を有する処理液をマスクブランクの表面処理に使用する処理液として選定工程6から成る。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における配線形状を改善すること。

【解決手段】半導体装置の製造方法は、溝領域を規定する第1パターンを有する第1マスクを、サイドウォール形状の転写により、半導体装置の層間膜に設けられた金属膜上に形成する工程と、前記第1パターンに重なる少なくとも一つの開口を有する第2マスクを、平面図で見た場合に、前記2マスクが前記第1マスクに重なり、前記開口が前記溝領域に重なるように、形成し、第2パターンを形成する工程と、前記第1及び第2マスクを介して、前記層間膜をエッチングし、前記第1パターンを前記層間膜に転写させる工程と、前記第2マスクを介して前記層間膜をエッチングし、前記第2パターンを前記層間膜に転写させる工程とを具備する。前記第1パターンは、前記第2パターンとは異なる深さで前記層間膜に形成される。

(もっと読む)

フォトマスクブランク、フォトマスク、反射型マスクブランクおよび反射型マスク並びにこれらの製造方法

【課題】極めて微細なパターンを形成できるフォトマスクブランク及びそのフォトマスクブランクに微細パターンを形成したフォトマスクを提供する。

【解決手段】透明基板上に、少なくとも2層からなる薄膜を有するフォトマスクブランクであって、前記薄膜は、タンタル、窒素、およびキセノンを含む材料からなる第1の層と、該第1の層の上面に積層されるタンタル、酸素、およびアルゴンを含む材料からなる第2の層とを有することを特徴とする。

(もっと読む)

プラズマエッチング方法および記憶媒体

【課題】無機膜をマスクとして有機膜をエッチングする場合に、ボーイング等のエッチング形状不良を生じさせずにエッチングすることができるプラズマエッチング方法を提供すること。

【解決手段】処理容器内に、その表面がシリコン含有物からなる上部電極と、被処理基板が載置される下部電極とが配置され、上部電極と下部電極との間にプラズマを形成して被処理基板に対してプラズマエッチングを行うプラズマエッチング装置を用い、無機膜をマスクとして被処理基板の有機膜をプラズマエッチングするにあたり、有機膜を途中までプラズマエッチングし、その後、プラズマを形成しつつ上部電極に負の直流電圧を印加して、エッチング部位の側壁に上部電極のシリコン含有物を含む保護膜を形成し、その後、プラズマエッチングを継続する。

(もっと読む)

パターン形成方法及び半導体装置の製造方法

【課題】基板の温度が100℃以下の低温環境下において、基板上の被処理膜をエッチングする際のマスクを所定のパターンに適切に形成する。

【解決手段】ウェハWの被処理膜400上に反射防止膜401とレジストパターン402が形成される(図10(a))。レジストパターン402がトリミングされると共に、反射防止膜401がエッチングされる(図10(b))。ウェハWの温度を100℃以下に維持した状態でプラズマ処理を行い、レジストパターン402及び反射防止膜パターン403上に、100MPa以下の膜ストレスを有するシリコン窒化膜404が成膜される(図10(c))。シリコン窒化膜404がエッチングされ、レジストパターン402及び反射防止膜パターン403が除去されて、被処理膜400上にシリコン窒化膜パターン405が形成される(図10(d))。

(もっと読む)

エッチングプロセスのための安定化したフォトレジスト構成

【課題】エッチレイヤに特徴を形成する方法を提供する。

【解決手段】第1のマスクが前記エッチレイヤ上に形成され、前記第1のマスクは、幅を有する複数のスペースを定義する。第1のマスクは横方向にエッチングされ、エッチングされた第1のマスクは、前記第1のマスクの前記スペースの前記幅より大きい幅を有する複数のスペースを定義する。前記エッチングされた第1のマスク上に側壁レイヤが形成され、前記側壁レイヤは、前記エッチングされた第1のマスクによって定義される前記スペースの前記幅よりも小さい幅を有する複数のスペースを定義する。前記エッチレイヤ中に前記側壁レイヤを通して特徴がエッチングされ、前記特徴は前記エッチングされた第1のマスクによって定義される前記スペースの前記幅よりも小さい幅を有する。前記マスク及び前記側壁レイヤは取り除かれる。

(もっと読む)

炭素含有薄膜のスリミング方法及び酸化装置

【課題】レジスト等の炭素含有薄膜のパターンの凸部のスリミング処理時のスリミング量(削り取り量)のばらつきを抑制してスリミング処理毎の再現性を向上させることが可能な炭素含有薄膜のスリミング方法である。

【解決手段】パターン化された炭素含有薄膜104が形成された被処理体Wを酸化装置2の処理容器4内へ搬入する搬入工程と、処理容器内へ水分を供給しつつ酸化ガスにより炭素含有薄膜104の表面を酸化処理して除去することによりパターンの凸部104Bの幅を小さくするスリミング工程とを有する。

(もっと読む)

反射型マスクの製造方法、および反射型マスクの製造装置

【課題】本発明の実施形態は、生産性を向上させることができる反射型マスクの製造方法、および反射型マスクの製造装置を提供する。

【解決手段】実施形態によれば、基板の主面に反射層を形成する工程と、前記反射層の上に吸収層を形成する工程と、前記吸収層にパターン領域を形成する工程と、前記吸収層と前記反射層とに前記パターン領域を囲む遮光領域を形成する工程と、を備え、前記遮光領域を形成する工程において、前記反射層を塩素と酸素とを含むガスを用いてエッチング処理する反射型マスクの製造方法が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】可能な限り従来の設備及び加工プロセスを継承してコストの上昇を抑制するも、Ta含有の導電材料を難除去性の残留付着物を発生せしめることなく所望に加工し、容易且つ確実に信頼性の高い半導体装置を実現する。

【解決手段】半導体基板上に、Ta含有層、TiN層、及び多結晶シリコン膜等のドライエッチング可能な層を順次積層し、TiN層をエッチングストッパーとして多結晶シリコン膜をドライエッチングして所定形状に残し、TiN層及びTa含有層をSPM、APM等を用いてウェットエッチングして多結晶シリコン膜下で所定形状に残す。

(もっと読む)

半導体装置の製造方法

【課題】微細で良好な形状のコンタクトホールを有する半導体装置の製造方法を提供する。

【解決手段】絶縁膜36上にフォトレジスト膜42を形成する工程と、フォトレジスト膜42に開口部44を形成する工程と、開口部44が形成されたフォトレジスト膜42をマスクとして絶縁膜36をエッチングすることによりコンタクトホール48を形成する工程とを有し、コンタクトホール48を形成する工程は、開口部44が形成されたフォトレジスト膜42上に保護膜46を堆積しながら絶縁膜36をプラズマエッチングする第1の工程と、フォトレジスト膜42上に堆積された保護膜46を一旦除去する第2の工程と、保護膜46が一旦除去されたフォトレジスト膜42上に他の保護膜を新たに堆積しながら絶縁膜36を更にプラズマエッチングする第3の工程とを含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】マスクの新規な作製技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、第1の膜を形成する工程と、第1の膜上方に、第1マスク膜を形成する工程と、第1マスク膜をパターニングする工程と、パターニングされた第1マスク膜の側部にプラズマ処理を行って、側部を変質層に変換する工程と、プラズマ処理の後、第1マスク膜の上部及び側部を覆う第2マスク膜を形成する工程と、第2マスク膜をエッチングして、側部に形成された第2マスク膜を残存させつつ、第1マスク膜上部に形成された第2マスク膜を除去する工程と、第2マスク膜のエッチングの後、変質層を除去する工程と、変質層を除去した後、残った部分の第1マスク膜、及び第2マスク膜をマスクとして、第1の膜をエッチングする工程とを有する。

(もっと読む)

微細パターンの形成方法

【課題】側壁部の形成の基礎となるパターンをレジストにより形成する場合であっても、側壁部の傾きを抑制できる微細パターンの形成方法を提供する。

【解決手段】基板上に形成されたエッチング対象層の上に有機膜を形成する有機膜形成ステップと、有機膜上にレジスト膜を形成し、このレジスト膜をパターニングするパターニングステップと、パターニングされたレジスト膜から露出する有機膜と、パターニングされたレジスト膜とを覆うように酸化シリコン膜を常温にて堆積する堆積ステップと、基板を加熱して酸化シリコン膜に引っ張り応力を生じさせる加熱ステップと、処理ステップの後に、パターニングされたレジスト膜の側壁に酸化シリコン膜が残るように当該酸化シリコン膜をエッチングする第1のエッチングステップと、パターニングされたレジスト膜を除去する除去ステップとを含む、微細パターンの形成方法が開示される。

(もっと読む)

集積回路用途の被覆およびハードマスク組成物、これらの製造方法および使用

【課題】層状材料、電子構成要素および半導体構成要素の製造を改善する組成物、これらの製造方法オヨビ使用を提供する。

【解決手段】少なくとも1種の無機化合物、および少なくとも1種の緻密化剤を含有し、前記緻密化剤は、少なくとも1種の無機化合物の密度と比較して、被覆材料の密度を増大させる被覆材料が、ここに記載されている。少なくとも1種の無機化合物を準備するステップと、少なくとも1種の緻密化剤を準備するステップと、少なくとも1種の無機化合物を少なくとも1種の緻密化剤と一緒にして被覆材料を形成するステップとを含み、前記緻密化剤は、少なくとも1種の無機化合物の密度と比較して、被覆材料の密度を増大させる被覆材料を製造する方法。

(もっと読む)

プラズマ処理装置

【課題】エッチングレートあるいは所望の加工形状をウエハ面内で均一に得ることのできるプラズマ処理装置を提供する。

【解決手段】真空処理容器内に処理ガスを供給するガス供給装置113と、前記真空処理容器内に試料を載置して保持する載置電極115と、前記載置電極に高周波バイアス電圧を供給する高周波バイアス電源117と、前記真空処理容器内を排気する排気装置と、前記真空処理容器内に磁界を形成する電磁コイル107,108,109と、前記真空処理容器に高周波エネルギーを供給して、前記磁界との相互作用によりプラズマを生成するプラズマ生成装置101とを備え、前記高周波バイアス電源は2MHz以上の高周波であり、前記載置電極上の前記真空処理容器のプラズマ生成領域に対向する面に形成されたアース領域の高さ以下の領域の磁束密度は20mT以下である。

(もっと読む)

フィーチャ微小寸法の低減

【課題】レイヤ中にフィーチャを形成する方法を提供する。

【解決手段】レイヤ上にフォトレジストレイヤが形成される。フォトレジストレイヤがパターン付けされることによって、フォトレジスト側壁を持つフォトレジストフィーチャが形成され、フォトレジストフィーチャは第1微小寸法を有する。フォトレジストフィーチャの側壁上にコンフォーマルレイヤが堆積されることによって、フォトレジストフィーチャの前記微小寸法が低減される。レイヤ内でフィーチャがエッチングされ、レイヤフィーチャは、第1微小寸法より小さい第2微小寸法を有する。

(もっと読む)

1 - 20 / 216

[ Back to top ]