Fターム[5F004EB02]の内容

半導体のドライエッチング (64,834) | エッチング対象部の機能 (2,366) | 電極、配線 (594)

Fターム[5F004EB02]に分類される特許

81 - 100 / 594

有機半導体デバイスの製造方法および薄膜トランジスタの製造方法

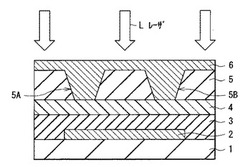

【課題】有機半導体層の上で導電層を迅速かつ容易にパターニングすると共に安定な性能を得ることが可能な薄膜トランジスタの製造方法を提供する。

【解決手段】有機半導体層4の上に、開口部5A,5Bを有する絶縁性保護層5を形成したのち、その絶縁性保護層5(開口部5A,5Bを含む)を覆うように、電極層6を形成する。こののち、絶縁性保護層5の形成領域(開口部5A,5Bを除く)における電極層6にレーザLを照射し、その電極層6をレーザアブレーションにより選択的に除去してソース電極およびドレイン電極を形成する。

(もっと読む)

プラズマ処理装置及び処理方法

【課題】製造されるデバイスにおける閾値のバラツキを抑制する。

【解決手段】内部が減圧排気される処理室内に処理ガスを供給し、さらに該処理室内に高周波エネルギを供給してプラズマを生成し前記処理室内の試料載置電極上に配置された試料にプラズマ処理を施すプラズマ処理装置において、該試料載置電極は、温度調節された冷媒を通流させるための冷媒溝を備えた基材部202と、該基材部の試料を載置する面に同心状に複数配置されたヒータ用抵抗体203、および静電吸着用電極222,223を備え、前記前記同心状に配置された複数のヒータ用抵抗体のうち中央部に配置した抵抗体に加熱電力を給電する線路の対地インピーダンスを周縁部に配置した抵抗体に加熱電力を給電する線路の対地インピーダンスよりも高く設定する。

(もっと読む)

半導体装置の製造方法

【課題】DRAM素子のような半導体装置において、半導体基板の溝部におけるゲート電極の埋設状態が良好となり、配線抵抗が低減され、素子特性に優れた半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の表面にゲート電極溝13を形成する工程と、ゲート電極溝13の内面に第1のバリア膜16aを形成する工程と、第1のバリア膜16aをエッチバックして、ゲート電極溝13の底面に第1のバリア膜16aの一部を残存させながら除去する工程と、ゲート電極溝13の内面と残存した第1のバリア膜16aの表面に第2のバリア膜16bを形成する工程と、第2のバリア膜16aの表面にタングステン膜を形成する工程と、このタングステン膜及び第2のバリア膜16bをエッチバックしてゲート電極溝13内にそれぞれ一部を残存させながら各膜を一括除去する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写によるマスクパターンの倒れ、マスクパターンの接触を抑制する。

【解決手段】シリコン基板1上に、第1のTEOS酸化膜2、シリコン窒化膜3、第1のアモルファスシリコン膜4、第2のTEOS酸化膜5を積層形成する。レジストによるパターニングでTEOS酸化膜5を第1幅D1の中間パターン5aに加工し、スリミング処理をして第2幅D2の芯材パターン5bを形成する。第2のアモルファスシリコン膜6を形成してスペーサ処理をすることで側壁膜6aを形成し、芯材パターン5bを除去して孤立したマスクパターン6bを得る。下地に同じアモルファスシリコン膜4を用いるので、マスクパターン6bの倒れや接触の発生を抑制できる。

(もっと読む)

パターン形成方法およびパターン形成体

【課題】複数の段差を備えた微細な3次元構造パターンの形成に好適なパターン形成方法を提供することを目的とする。

【解決手段】本発明によれば、ハードマスク層は基板に対してエッチング選択比が高い材料であるため、形成する3次元構造パターンに対応するハードマスク層の段差は、所望する3次元構造パターンよりも、深さを小さくすることが出来る。また、ハードマスク層に段差を形成するにあたり、ハードマスク層を基板表面を覆うように残存させることにより、複数段のパターン形成において、基板の帯電(チャージアップ)を抑制することが出来る。

(もっと読む)

ドライエッチング方法

【課題】コストの上昇を招くことなく、より安定した状態でInPの層がドライエッチング法によりエッチングできるようにする。

【解決手段】塩素ガスを用いたドライエッチング法によりマスクパターン106をマスクとして基板101を選択的にエッチングすることで、基板101にビアホール(開口パターン)107を形成する。例えば、温度条件を200℃程度とし、塩素ガスを用いた反応性イオンエッチング法によりエッチングすればよい。

(もっと読む)

プラズマエッチング装置およびプラズマエッチング方法

【課題】プラズマエッチングにおいて、ステップ間で連続放電を行った場合の、スループット低下,再現性低下,プラズマ放電不安定の問題を解決する。

【解決手段】ガス供給源101からガス供給源111に切換える場合に、事前にバルブ114を開き、MFC112の流量を次ステップで使用する流量に設定して、ガス供給源111を排気手段5に流しておいて、バルブ113を開くと同時にバルブ114を閉じることでガス供給源101からガス供給源111に切換えるガス切換方法において、バルブ113,バルブ114およびMFC112で囲まれた部分のガス配管115の容積V1を、ガス貯め10や処理ガスライン8を含むシャワープレートからバルブ113までの間の容積Voに比べて十分小さくする。これによって、圧力のアンダーシュートがなくなり放電不安定が発生しなくなる。

(もっと読む)

パターン形成方法および含浸装置

【課題】本発明は、アスペクト比の大きな微細パターンを安定して形成できるパターン形成方法と、その方法に使用される含浸装置を提供することを目的とする。

【解決手段】被加工部材3上に所定のパターンが形成されたエッチングマスク9を形成する工程と、前記エッチングマスク9に所定の物質12を含浸させる工程と、前記所定の物質12を含浸した前記エッチングマスク9を用い、前記被加工部材3をパターニングする工程と、を備えたことを特徴とするパターン形成方法が提供される。

(もっと読む)

エッチング方法、エッチング装置及びリング部材

【課題】処理ガスをプラズマ化して基板上の被エッチング膜をドライエッチングするにあたり、基板に対して均一性高くエッチング処理を行うことができる技術を提供すること。

【解決手段】処理容器内に基板を搬入して載置台に載置する工程と、少なくとも表面部の主成分が基板の被エッチング膜の主成分と同じ材質であるリング部材を基板を囲むように配置した状態で、基板に対向するガス供給部から処理ガスをシャワー状に吐出すると共に処理ガスをプラズマ化して被エッチング膜をエッチングする工程と、前記処理容器内を排気路を介して真空引きする工程と、を含むようにエッチングを行う。それによって基板の周端部付近におけるプラズマの活性種の分布の偏りを抑える。

(もっと読む)

半導体装置の製造方法

【課題】配線構造を形成する際に、ウェハ面内の配線溝の深さのばらつきを抑え、均一加工を実現する。

【解決手段】高炭素濃度絶縁膜114と、炭素を含まないまたは炭素濃度が低い低炭素濃度絶縁膜116との積層構造にドライエッチングで配線溝を形成する際、CHF系ガスを添加した第1のエッチングガスを用いた第1のエッチング条件で低炭素濃度絶縁膜116に配線溝を形成し、当該配線溝底部に高炭素濃度絶縁膜114を露出させる。第1のエッチング条件の第1のエッチングガス中のCHF系ガスの分圧は、第1のエッチングガスに当該CHF系ガスを添加していない場合の各膜へのエッチングレートを基準として、当該CHF系ガスを添加することにより、高炭素濃度絶縁膜114に対するエッチングレートが低下するとともに、低炭素濃度絶縁膜116に対するエッチングレートを変化させない範囲に設定されている。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタのキャパシタ誘電体膜がダメージを受けるのを抑制する半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の上方に第1の絶縁膜を形成する工程と、第1の絶縁膜の上に、第1の導電膜20、強誘電体膜21、及び第2の導電膜を形成する工程と、第2の導電膜の上にハードマスク23aを形成する工程と、ハードマス23aをマスクにし、第2の導電膜をエッチングして上部電極22aにする工程と、強誘電体膜21をパターニングしてキャパシタ誘電体膜にする工程と、第1の導電膜20をエッチングして下部電極にする工程とを有し、第2の導電膜をエッチングする工程において、上部電極22aの横に強誘電体膜21が露出したときに、エッチング雰囲気が、酸素ガスを含み且つハロゲンを含まない雰囲気となっている。

(もっと読む)

半導体装置の製造方法

【目的】Cu配線寿命の劣化と絶縁膜の絶縁性劣化を共に低減する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、チャンバ内面にシリコン(Si)膜を表面層とする多層膜を形成する工程(S102)と、前記多層膜が内面に形成されたチャンバ内に、表面に銅(Cu)配線と絶縁膜とが形成された基板を配置して、希ガスプラズマ処理を行なう工程(S106)と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】パターン不良を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】被加工膜上に、ラインアンドスペース部と前記ラインアンドスペース部の外側に形成された第一のパターンとを有する第二のパターンを形成し、側壁パターンを前記第二のパターンの側壁に形成し、前記第一のパターンの側壁のうち、前記ラインアンドスペース部と反対側の側壁に形成された側壁パターンを除去し、前記第一のパターンの側壁のうち、前記ラインアンドスペース部と対向する側の側壁に形成された側壁パターンに基づき、回路パターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】スペーサーを形成すべき凸部の相互間隔、溝の幅、又は孔の径が小さい場合に、基板保護膜を用いる必要がなく、かつノッチを生じさせずにスペーサーを形成する。

【解決手段】スペーサーを形成する時の異方性エッチングにおいて、「1−(異方性エッチングおける第2スペーサー形成膜5の垂直方向のエッチングレートに対する水平方向のエッチングレートの比)」を異方性度と定義し、「(第1スペーサー形成膜4の膜厚T1−第2スペーサー形成膜5の膜厚T2)/(第1スペーサー形成膜4の膜厚T1)」を第1スペーサー形成膜4の第2スペーサー形成膜5に対する膜厚増分率と定義した時に、第2スペーサー形成膜5の垂直方向のエッチングレートを第1スペーサー形成膜4の垂直方向のエッチングレートより小さく、かつ第1スペーサー形成膜4の垂直方向のエッチングレートに異方性度と膜厚増分率のうち小さい方を乗じた値より大きいエッチング条件にする。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を有するMISFETを備えた半導体装置の信頼性向上を図る。

【解決手段】nチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとLaとOとを主成分として含有するHf含有絶縁膜4aを形成し、pチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとAlとOとを主成分として含有するHf含有絶縁膜4bを形成する。それから、金属膜7とシリコン膜8を形成し、これらをドライエッチングでパターニングしてゲート電極GE1,GE2を形成する。その後、ゲート電極GE1,GE2で覆われない部分のHf含有絶縁膜4a,4bをウェットエッチングで除去するが、この際、フッ酸を含有しない酸性溶液でのウェット処理とアルカリ性溶液でのウェット処理とを行ってから、フッ酸を含有する酸性溶液でのウェット処理を行う。

(もっと読む)

配線の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

半導体装置の製造方法

【課題】ダマシン法により絶縁膜に埋め込まれた配線を形成する半導体装置の製造方法に関し、絶縁膜にビアホールや配線トレンチ等の開口部を形成する際のエッチング処理を安定化しうる半導体装置の製造方法を提供する。

【解決手段】Cuを含む配線層と、絶縁膜と、有機膜と、第1の開口部を有するレジスト膜とを有する複数の半導体基板について、レジスト膜をマスクとして、第1の開口部内の有機膜をエッチングする工程と、第1の開口部内の絶縁膜をエッチングし、絶縁膜に、配線層を露出する第2の開口部を形成する工程と、第2の開口部内に露出した配線層の表面を水素プラズマ処理する工程とを、同じエッチング装置の処理室で連続して処理する際に、一の半導体基板について水素プラズマ処理を行う工程を行った後、一の半導体基板の次に処理する他の半導体基板について有機膜をエッチングする工程を行う前に、処理室内に付着したCu堆積物を除去する。

(もっと読む)

パターン形成方法、パターン形成体

【課題】複数の段差を備えた微細な3次元構造パターンの形成に好適なパターン形成方法及びパターン形成体を提供する。

【解決手段】基板上に第1層目のハードマスク層を形成し、基板上の第1層目のハードマスク層を備えた面に、順に、第2層目から第N層目までのハードマスク層を形成し、第N層目のハードマスク層のパターニング処理し、順に、第(N−1)層目から第1層目までのハードマスク層のパターニング処理し、パターニングされた第1層目から第N層目までのハードマスク層をエッチングマスクとして基板に第1段目の異方性エッチングしてパターニング処理することを特徴とするパターン形成方法。

(もっと読む)

ドライエッチング方法

【課題】低誘電率を有する多孔性の絶縁膜における比誘電率の増大を抑制可能なドライエッチング方法を提供する。

【解決手段】

比誘電率が2.2以下である多孔性、且つ低誘電率の絶縁膜Iを誘導結合プラズマによってエッチングするに際し、一般式CaFbXcにて表されるフルオロカーボン系のガス、又はC4F8をエッチングガスとして用いるとともに、該エッチングガスの圧力を0.5Pa〜5.0Paに維持する。加えて、高周波アンテナ30に100W〜600Wの範囲で13.56MHzの高周波電力を印可してエッチングガスを用いたプラズマを誘起する。上記絶縁膜Iを有する基板Sをこのプラズマに曝しつつ、該基板Sに対し50W〜300Wの範囲で13.56MHzの高周波電力を印可することにより、プラズマ中のイオン成分によるエッチング反応が支配的となる条件で絶縁膜Iをエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】微細なパターンを精度良く形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、被加工体1上にCを含む材料からなる芯材2を選択的に形成する工程と、芯材2の上面および側面を覆うように、酸素を含まない材料からなる保護膜3を形成する工程と、保護膜3を介して芯材2と被加工体1を覆うように酸化膜4を形成する工程と、芯材2の側方に少なくとも酸化膜4からなる側壁5を加工形成する工程と、少なくとも芯材2を除去した後、側壁5をマスクとして用いて被加工体1をエッチングし、側壁5のパターンを転写する工程と、を含む。

(もっと読む)

81 - 100 / 594

[ Back to top ]