Fターム[5F004EB02]の内容

半導体のドライエッチング (64,834) | エッチング対象部の機能 (2,366) | 電極、配線 (594)

Fターム[5F004EB02]に分類される特許

161 - 180 / 594

透明導電膜のパターニング方法

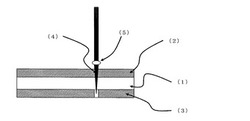

【課題】タッチパネルやPDP、LCDやELディスプレイ材料、太陽電池の透明電極や裏面電極、ハイブリッド型太陽電池の透明中間層、化合物半導体高速デバイスに用いる低誘電率膜、表面弾性波素子、赤外線カットなどを目的として、基材の両面に透明電極が形成された透明導電膜のパターニングの方法を提供する。

【解決手段】基材1の両面に透明電極層2,3が形成された透明導電膜のパターニングにおいて、YAGまたはYVO4レーザー4の基本波または第2高調波を用いることで、片面のみの精度の高いパターニングが可能となる。

(もっと読む)

半導体製造方法および半導体製造装置

【課題】ウェハ面内のパタン寸法の均一性を向上させ、半導体装置の特性のばらつきを抑えることが可能な半導体製造方法と半導体製造装置を提供する。

【解決手段】ウェハ上にマスクパタンを複数の露光ショットにより露光する際に、予め測定されたエッチング後の各露光ショット内のパタン寸法分布に基づき、各露光ショット内の補正露光量を求め、各露光ショットにおいて、それぞれの補正露光量で露光し、露光されたウェハをエッチングすることにより、ウェハにパタンを形成する。

(もっと読む)

微細放電表面改質方法および微細放電表面改質装置

【課題】微小放電プラズマの生成領域を制御して処理対象の所望部位のみに親水性を高める処理を施すため、必要最低限の局部領域に対して表面改質を行なうことができる微細放電表面改質方法および装置を提供する。

【解決手段】二次元平面上に所定の間隔に配置された線状の高電圧電極と、二次元平面と実質的に平行な他の二次元平面上に所定の間隔に配置された線状の接地電極と、を二次元投影平面視野において互いに交差するように配置し、高電圧電極と接地電極との間に被処理基板を配置し、かつ接地電極を被処理基板と接触導通させ、かつ高電圧電極と被処理基板とを対向して配置し、高電圧電極と接地電極との間に高電圧を印加するとともに、高電圧印加領域に放電ガスを供給し、微細な非平衡放電プラズマを生成し、高電圧電極および接地電極に対する給電動作を制御することにより、二次元投影平面視野において高電圧電極と接地電極とが交差する領域に微小放電プラズマを発生させ、被処理基板の表面の所望部位を改質する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート長を決めるドライエッチングにおいてプラズマ発光をモニターすることによる終点検出方法を用いることにより半導体装置のゲート長を安定して製造する。

【解決手段】ソース拡散層、ドレイン拡散層及び柱状半導体層が基板上に垂直方向に階層的に配置され、柱状半導体層の側壁にゲートが配置される半導体装置の製造方法であって、柱状半導体層を埋め込むように第1の絶縁膜又は導電膜を成膜し、第1の絶縁膜又は導電膜を柱状半導体層上部に形成されたストッパーにより終点検出を行い平坦化し、第2の絶縁膜又は導電膜を成膜し、第2の絶縁膜又は導電膜のエッチングすると共にエッチング時のエッチングレートを算出し、第2の絶縁膜又は導電膜をエッチバックする際の第2の絶縁膜又は導電膜のエッチングレートを用いて第1の絶縁膜又は導電膜のエッチングの終点検出を行うことにより、第1の絶縁膜又は導電膜のエッチング量を制御する。

(もっと読む)

プラズマ処理方法

【課題】フリージング法を用いたダブルパターニング技術により形成されたフォトレジストマスクのトリミング工程において、得られる回路パターン寸法のウエハ面内の均一性を改善する。

【解決手段】半導体基板201上の積層化された薄膜202〜205と、積層化された薄膜上にフリージング法を用いたダブルパターンニング技術により形成されたフォトレジストマスクパターン206,208とを有する被処理材を、よりマスク寸法の小さいマスクパターンを形成するトリミング工程において、フリージング材料207に被覆されたフォトレジストマスクパターン206とフリージング材料に被覆されていないフォトレジストマスクパターン208を酸素ガス(O2)を含む混合ガスを用いてマスクパターン206と208フのトリミングレートを同じにし、得られる回路パターン寸法のウエハ面内の均一性を改善する。

(もっと読む)

銅層処理

本開示は銅処理のためのデバイス、方法およびシステムを含み、具体的には、硫黄プラズマを用いた銅層処理を含む。1つ以上の実施形態は、銅を硫黄を含むプラズマガスと反応させて銅硫黄化合物を形成し、水で銅硫黄化合物の少なくとも一部を除去する方法を含むことができる。 (もっと読む)

コンタクトホール側壁の抵抗値測定方法

【課題】コンタクトホール側壁に付着した有機膜の抵抗値を簡単且つ的確に測定する。

【解決手段】基板20上に形成された下部電極であるポリSi膜22aと、このポリSi膜22a上にBPSG膜23を介して形成された中間電極であるポリSi膜24aと、このポリSi膜24a上にBPSG膜25を介して選択的に形成されたホトレジスト膜からなるホールパターン26aと、このホールパターン26aをマスクにしてプラズマエッチングにより形成され、ポリSi膜24a,22aを貫通するコンタクトホール27と、このコンタクトホール27の形成時に、コンタクトホール側壁に付着する有機膜28と、を有する半導体装置を用意する。そして、ポリSi膜22a,24a上に有機膜・レジスト膜26bが被着された状態で、ポリSi膜22a,24a上から、プローブ針31により複数回コンタクトを実施し、有機膜28の抵抗値を測定する。

(もっと読む)

バリア層除去方法及び装置

本発明は、無応力電気化学銅研磨(SFP)の処理、SFP処理の間に形成された酸化タンタル又は酸化チタンの除去、及び、XeF2ガス相エッチングバリア層Ta/TaN又はTi/TiN処理、からなる半導体処理の方法及び装置に関する。第1に、板状の銅フィルムの少なくとも一部がSFPにて研磨される。第2に、SFP処理の間に形成されたバリア金属酸化物がエッチング液によりエッチングされる。最後に、バリア層Ta/TaN又はTi/TiNがXeF2ガス相エッチングにより除去される。そのため装置は3つのサブ系からなり、それらは無応力銅電解研磨系、バリア層酸化物フィルム除去系、及び、バリア層Ta/TaN又はTi/TiNガス相エッチング系である。  (もっと読む)

(もっと読む)

半導体加工方法

【課題】高誘電率絶縁膜上に金属膜及び多結晶Siを堆積した構造の半導体を垂直にかつ微細に加工する。

【解決手段】半導体基板上に形成されたHfあるいはZrを含む絶縁膜102、該絶縁膜上に並置して形成された互いに仕事関数が異なる第1および第2の金属膜103,104、該第1および第2の金属膜上に堆積して形成した多結晶シリコン膜105を有し、該多結晶シリコン膜上に形成したレジスト108を用いて、プラズマ雰囲気中で前記多結晶シリコン膜並びに前記第1および第2の金属膜をエッチング加工する半導体加工方法において、前記前記複数種の金属膜上の多結晶シリコン膜のうちエッチング終了が早い方である第2の金属膜上の多結晶シリコン膜のエッチング終了後は、前記処理ガスとして、HBrおよび酸素を含むガスを用いる。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を増加させることができる半導体素子のパターン形成方法を提供する。

【解決手段】基板300上のデュアルマスク層をパターニングして第1領域Aには第1マスクパターン320Aを形成し、第2領域Bには第1マスクパターン320Aより幅広である第2マスクパターン320Bを形成する。第1マスクパターン320Aの両側壁を覆う第1スペーサ350Aと第2マスクパターン320Bの両側壁を覆う第2スペーサ350Bとを同時に形成する。第1マスクパターン320Aを除去した後、第1領域Aでは、第1スペーサ350Aをエッチングマスクとして利用し、第2領域Bでは第2マスクパターン320B及び第2スペーサ350Bをエッチングマスクとして利用して第1領域A及び第2領域Bで同時に基板300をエッチングする。

(もっと読む)

電極形成方法および半導体素子

【課題】電極パタンを精度よく形成する。

【解決手段】半導体基板の一方面(コンタクト層10)上に、SiO2膜12−1、SiN膜14−1、SiO2膜12−2、およびSiN膜14−2を順に積層した4層の絶縁膜を形成する工程と、それら4層の絶縁膜にコンタクト層10の表面まで貫通するコンタクトホールを形成する工程と、SiO2膜12に対するエッチングレートがSiN膜14に対するエッチングレートより高い薬液(たとえばフッ酸)を用いて、コンタクトホールに露出したSiO2膜12−2の側面をコンタクトホールに露出したSiN膜14−2の側面より所定長だけ後退させる工程と、コンタクトホールに露出したコンタクト層10上に、SiN膜14−2に当接しない厚さを有する電極層20−1を蒸着により形成する工程と、上記薬液を用いて、SiN膜14−2をSiO2膜12−2とともに除去する工程と、を含む。

(もっと読む)

金属ゲート構造への多層/多入力/多出力(MLMIMO)モデルの使用方法

【課題】 本発明はウエハ処理に関する。

【解決手段】 本発明は、1つ以上の測定処理、1つ以上のポリエッチング(P-E)処理及び1つ以上の金属ゲートエッチング処理を有する多層処理手順並びに多層/多入力/多出力(MLMIMO)モデル及びライブラリを用いてウエハを処理する方法を供する。前記MLMIMO処理制御は、多数の層及び/又は多数の処理工程間での動的に相互作用する挙動のモデル化を用いる。前記多数の層及び/又は多数の処理工程は、等方性及び/又は異方性エッチング処理を用いて作製可能なライン、溝、ビア、スペーサ、コンタクト、及びゲート構造の作製に関連づけられて良い。

(もっと読む)

酸化膜表面の洗浄及び保護方法および酸化膜表面の洗浄及び保護装置

【課題】基板上のITO表面を洗浄及び保護する方法を提供する。

【解決手段】プロセスチャンバPC100の内部に載置された基板上のITO表面にその表面の汚染物の分子の結合エネルギーより強いエネルギーを持つ光を光源から照射し、その照射中又は照射後、直ちに同一チャンバ内にてシランカップリングのガスを供給する。これにより、基板上のITO表面を洗浄及び保護することができる。

(もっと読む)

終点検出方法、基板処理方法、基板処理装置および基板処理システム

【課題】表面に酸化銅が形成された銅膜を有する基板に対し、有機酸にてドライクリーニングを施して酸化銅を除去する際に、その終点を簡便にかつ高精度で、迅速に検出することができる終点検出方法を提供すること。

【解決手段】処理室内に有機酸ガスを導入してドライ洗浄処理を行っている際の処理室内のガスまたは処理室から排出されたガスの分析を行って、酸化銅が形成されている際と酸化銅が除去された際との所定のガス成分の濃度変化に基づいて終点を検出する。

(もっと読む)

フォトレジストの縁部のバリの形成方法とアレイ基板の製造方法

【課題】フォトレジストの縁部のバリの形成方法とアレイ基板の製造方法に関する。

【解決手段】当該アレイ基板の製造方法は、基板にゲート・ラインとゲート電極パターンを形成するステップと、データ・ラインと、ソース電極と、ドレイン電極と、TFTチャネル領域パターンとを形成し、フォトレジストを残し、パッシべーション層を堆積し、剥離工程によってフォトレジスト及びその上のパッシべーション層を除去するステップと、フォトレジストを塗布し、フォトレジストに山状の縁部のバリを形成し、透明導電薄膜を堆積し、剥離工程によってドレイン電極に直接に接続する画素電極パターンを形成する。

(もっと読む)

半導体加工方法

【課題】high−k膜/メタルゲート構造を有する半導体素子のドライエッチングにおいて、メタルゲート部分を垂直にエッチングする。

【解決手段】減圧処理室204と、該減圧処理室に処理ガスを供給するガス供給手段と、前記減圧処理室内に、半導体基板を載置して保持する試料台205と、前記減圧処理室に供給された処理ガスに高周波エネルギを供給してプラズマを生成するプラズマ生成手段を備え、生成したプラズマにより前記半導体基板にプラズマエッチング処理を施す半導体加工方法において、前記試料台上に、HfあるいはZrを含む高誘電率絶縁膜、TiあるいはTaを含む仕事関数制御金属導体膜、およびレジストを順次形成した半導体基板206を載置し、前記レジストを用いて前記導体膜をエッチング加工するに際して、前記試料台にオンオフ変調された基板バイアス電圧を印加する。

(もっと読む)

半導体装置の製造方法

【課題】仕事関数金属膜と低抵抗膜とで構成されたゲート電極をプラズマエッチングする際に、膜質に応じたエッチングステップの切り替えの遅延を防ぐ。

【解決手段】低抵抗膜6中であって、仕事関数金属膜4との界面の近傍に、プラズマ発光モニタに感度のある、窒素を含む進捗モニタ層5を設けることで、エッチング中のプラズマ発光の変化を検知し、エッチングの進捗をモニタすることでエッチングステップ切り替えの遅延を防止することができる。

(もっと読む)

プラズマ処理方法およびプラズマ処理装置

【課題】プラズマ処理室の温度を正確に特定の状態とし、プラズマ処理の特性を一定に保って、高精度のプラズマ処理を実施することが可能なプラズマ処理装置を提供する。

【解決手段】プラズマ処理室1内で被処理物wをプラズマ処理するプラズマ処理装置において、プラズマ処理室1内部の温度とプラズマ生成条件とを関連付けて格納するデータベース25と、データベース25からプラズマ処理室1内部の温度とプラズマ生成条件との相関式を格納するモデル式格納部26と、相関式の作成および最適なプラズマ生成条件の算出を行う演算部24を備えた計算機21とを備え、プラズマ処理の状態を監視するプロセスモニタ31と、プロセスモニタが出力した値とプラズマ処理室の温度とを関連付けてデータベース25に格納し、計算機21がプラズマ処理室の温度が概略一定になるようなプラズマ処理条件を算出し、これに基づいてプラズマ処理を行なうプラズマ処理装置。

(もっと読む)

半導体装置の製造方法

【課題】、デュアルダマシン法により低誘電率膜に埋め込まれた配線層を形成する場合において、オープン不良の発生を伴うことなく、設計通りの配線層を形成し得る半導体装置の製造方法を提供する。

【解決手段】ビアホール形成領域の低誘電率膜42、第1のハードマスク44及び第2のハードマスク46を除去することにより、低誘電率膜42にビアホール52を形成する工程と、配線トレンチ形成領域の第2のハードマスク46を除去する工程と、第2のハードマスク46をマスクとして第1のハードマスク44をエッチングすることにより、配線トレンチ形成領域の第1のハードマスク44を除去する工程とを有し、配線トレンチ形成領域の第1のハードマスク44を除去する工程では、ビアホール52底のバリア膜40をもエッチングすることにより、ビアホール52底のバリア膜40を部分的に除去する。

(もっと読む)

銅めっきされた高アスペクト比のビア、及びその製造する方法

【課題】 最新のスケーリング技術の要件に適応することができ、適切に機能する実行可能なビアを一貫して生成できる、改善されたビア製造プロセスを提供すること。

【解決手段】 改善された高アスペクト比ビア及びそれを形成するための技術が提供される。1つの態様において、銅めっきされた高アスペクト比ビアを製造する方法が提供される。この方法は、以下のステップを含む。誘電体層内に高アスペクト比ビアをエッチングする。高アスペクト比ビア内及び誘電体層の1つ又は複数の表面の上に、拡散バリア領域を堆積させる。拡散バリア層の上に銅層を堆積させる。銅層の上にルテニウム層を堆積させる。高アスペクト比ビアを、ルテニウム層の上にめっきされた銅で充填する。この方法によって形成される銅めっきされた高アスペクト比ビアも提供される。

(もっと読む)

161 - 180 / 594

[ Back to top ]