Fターム[5F005AH02]の内容

Fターム[5F005AH02]に分類される特許

61 - 80 / 102

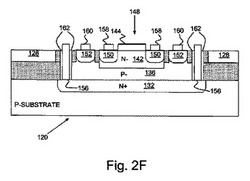

垂直型電流制御型シリコン・オン・インシュレータ(SOI)デバイス及びそれを形成する方法

【課題】 CMOS集積回路(IC)のための静電放電(ESD)保護デバイスとして用いるのに適した電流制御シリコン・オン・インシュレータ(SOI)デバイスを提供すること。

【解決手段】 垂直型シリコン制御整流器(SCR)、垂直型バイポーラ・トランジスタ、垂直型キャパシタ、抵抗器及び/又は垂直型ピンチ抵抗器のようなデバイスを有するシリコン・オン・インシュレータ(SOI)集積回路(IC)チップ、及びそれらのデバイスを作製する方法である。デバイスは、SOI表面層及び絶縁体層を通って基板に達するシード孔内に形成される。例えばN−型埋め込み拡散部が、基板内のシード孔を通って形成される。ドープされたエピタキシャル層が、埋め込み拡散部上に形成され、このドープされたエピタキシャル層は、例えばP−型層及びN−型層などの多数のドープ層を含むことができる。ドープされたエピタキシャル層上に、例えばP−型のポリシリコンを形成することができる。コンタクト・ライナ内に、埋め込み拡散部へのコンタクトが形成される。

(もっと読む)

半導体装置の製造方法

【課題】サイリスタ構成の半導体装置において、アノード側の第1p型領域p1とn型の第1n型領域n1との界面を、急峻な濃度プロファイルに形成することを可能とする。

【解決手段】第1伝導型の第1領域(第1p型領域p1)と、前記第1伝導型とは逆伝導の第2伝導型の第2領域(第1n型領域n1)と、第1伝導型の第3領域(第2p型領域p2)と、第2伝導型の第4領域(第2n型領域n2)とが順に接合されたサイリスタを有する半導体装置1の製造方法において、前記第1n型領域n1をn型の不純物をドーピングしながらエピタキシャル成長により形成する工程と、前記第1n型領域n1の表層を除去する表面処理を行う工程と、前記表面処理をした第1n型領域n1上に、前記第1p型領域p1をp型の不純物をドーピングしながらエピタキシャル成長により形成する工程とを備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を小さくすることのできる半導体装置およびその製造方法を提供する。

【解決手段】IGBT91は、基板Sと、基板Sの上面Sa側に形成されたエミッタ電極17と、基板Sの下面Sb側に形成されたコレクタ電極15と、エミッタ電極17とコレクタ電極15との間を流れる電流を制御するための制御機構(p型ベース領域7、n+不純物領域11、絶縁膜13、およびゲート電極19)とを備えている。n-ドリフト領域1が基板S内に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】急峻な不純物プロファイルを呈する第1n型半導体層と第1p型半導体層を備えたサイリスタを有する半導体装置の製造方法を提供する。

【解決手段】第1p型半導体層p1と、第1n型半導体層n1と、第2p型半導体層p2と、第2n型半導体層n2とを順に接合してなるサイリスタを有する半導体装置の製造方法であって、半導体基板11の表面層に、p型不純物を含む第2p型半導体層p2を形成する工程と、エピタキシャル成長により、第2p型半導体層p2が設けられた半導体基板11上に、n型不純物を含む第1n型半導体層n1を形成する工程と、エピタキシャル成長により、第1n型半導体層n1上に、第1n型半導体層n1を形成する工程よりも低い成膜温度で、p型不純物を含む第1p型半導体層p1を形成する工程とを有することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】急峻な不純物プロファイルを呈する第1n型半導体層と第1p型半導体層とを備えたサイリスタを有する半導体装置の製造方法を提供する。

【解決手段】第1p型半導体層p1と、第1n型半導体層n1と、第2p型半導体層p2と、第2n型半導体層n2とを順に接合してなるサイリスタを有する半導体装置の製造方法であって、半導体基板11の表面層に、p型不純物を含む第2p型半導体層p2を形成する工程と、エピタキシャル成長により、第2p型半導体層p2が設けられた半導体基板11上に、n型不純物を含む第1n型半導体層n1を形成する工程と、エピタキシャル成長により、第1n型半導体層n1上に、ノンドープ半導体層mを形成する工程と、エピタキシャル成長により、ノンドープ半導体層m上に、p型不純物を含む第1p型半導体層p1を形成する工程とを有する半導体装置の製造方法である。

(もっと読む)

静電気保護用半導体装置

【課題】高い保持電圧特性を有するSCR構造の静電気保護用半導体装置を実現すること。

【解決手段】SOI基板に形成されたSCR構造の静電気保護用半導体装置において、埋め込み絶縁膜11上に埋め込みn+ 型領域12を形成し、アノードn型領域20、カソードp型領域21は、延長領域20a、21aを備えている。延長領域20aの長さLnと、延長領域21aの長さLpと、アノードp型領域20、カソードp型領域21から埋め込みn+ 型領域12までの縦方向の距離Lyを調整することで、所望の保持耐圧特性を得ることができ、アノードn型領域20とカソードp型領域21との間の距離Lを調整することで、所望の動作開始電圧値を得ることができる。

(もっと読む)

静電気保護用半導体装置

【課題】高い保持電圧特性を有するSCR構造の静電気保護用半導体装置を実現すること。

【解決手段】SOI基板に形成された双方向型SCR構造の静電気保護用半導体装置において、埋め込み絶縁膜11上に埋め込みn+ 型領域12を形成し、アノードp型領域20、カソードp型領域21は、延長領域20a、21aを備えている。延長領域20a、21aの長さLpと、アノードp型領域20、カソードp型領域21から埋め込みn+ 型領域12までの縦方向の距離Lyを調整することで、所望の保持耐圧特性を得ることができ、アノードp型領域20とカソードp型領域21との間の距離Lを調整することで、所望の動作開始電圧値を得ることができる。

(もっと読む)

圧接型大電力用サイリスタモジュール

【課題】圧接型大電力用サイリスタモジュール全体の上下方向寸法を小型化する。

【解決手段】放熱板1上に絶縁板11、アノード端子バー12を配置し、下面にアノード電極13aを有し、上面の中心部分にゲート電極13bを有し、その周りに環状のカソード電極13cを有するサイリスタチップ13をそれらの上に配置し、カソード電極13c上に導電性カソードスペーサを14配置し、ゲート電極13b上にコイルバネ型ゲート電極信号線15を配置し、導電性カソードスペーサ14とコイルバネ型ゲート電極信号線15とを絶縁する筒状の絶縁性ゲートスペーサ16を配置し、導電性カソードスペーサ14上にカソード端子バー18を配置し、それらを圧接手段19により上下方向に圧接し、コイルバネ型ゲート電極信号線15の上端の水平方向に延ばされた部分15bを絶縁性ゲートスペーサ16の収容溝16aの底面16a2と協働して狭持する狭持突起17bを絶縁性蓋部材17の下面に形成した。

(もっと読む)

半導体装置およびその製造方法

【課題】セル面積を縮小化するとともに、サリサイドプロセスによるサイリスタを構成する領域間の短絡を防ぐことを可能とする。

【解決手段】第1伝導型の第1領域21と、第2伝導型の第2領域22と、第1伝導型の第3領域23と、第2伝導型の第4領域24とが順に接合されたもので、第3領域23が半導体領域(半導体基板11)に形成されたサイリスタ20、および第3領域23上に形成されたゲート(ゲート電極32)を有する半導体装置1であって、第2領域22は第3領域23上に形成された絶縁膜40の第3領域23に達する開口部47内部に形成され、第1領域21は開口部47内の第2領域22上から絶縁膜40上の一部にかけて形成され、第1領域21上、ゲート電極32上、第4領域24上に金属シリサイド膜25、26,27が形成されていることを特徴とする。

(もっと読む)

SiC結晶の質を向上させる方法およびSiC半導体素子

【課題】高温アニーリングにより、キャリア捕獲中心を効果的に減少または除去するSiC層の質を向上させる方法、および該方法により作製されたSiC半導体素子を提供する。

【解決手段】(a)最初のSiC結晶層(E)における浅い表面層(A)に炭素原子(C)、珪素原子、水素原子、またはヘリウム原子をイオン注入して、注入表面層に余剰な格子間炭素原子を導入する工程と、(b)当該層を加熱することにより、注入表面層(A)からバルク層(E)へ格子間炭素原子(C)を拡散させるとともにバルク層における電気的に活性な点欠陥を不活性化する工程と、を含む、幾つかのキャリア捕獲中心を除去または減少することによりSiC層の質を向上させる方法および該方法により作製された半導体素子。上記工程の後、表面層(A)を、エッチングするかまたは機械的に除去してもよい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】移動度を高めることで、オンからオフへのスイッチング速度を高速化することを可能とする。

【解決手段】第1伝導型の第1領域(第1p型領域p1)と、前記第1伝導型とは逆伝導の第2伝導型の第2領域(第1n型領域n1)と、第1伝導型の第3領域(第2p型領域p2)と、第2伝導型の第4領域(第2n型領域n2)とが順に接合されたもので、該第3領域(第2p型領域p2)にゲート(ゲート電極14等)が形成されたサイリスタ2を有する半導体装置1であって、前記サイリスタ2の第1領域乃至第4領域は、シリコンゲルマニウム領域もしくはゲルマニウム領域に形成されていることを特徴とするものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】安価なバルク半導体基板を用いながらも、特別なプロセスを要さずにサイリスタを用いたメモリセルを得ることが可能な半導体装置を提供する。

【解決手段】p型の半導体基板100の表面側に設けられたn型カソードn(K)と、n型カソードn(K)の表面層部分に設けられたp型ベースp(B)と、この上部に順次設けられたn型ベースn(B)およびpアノードp(A)と、p型ベースp(B)上に設けられたゲート電極Gとからなるサイリスタ構成のDRAMセルを備えた半導体装置1aである。

(もっと読む)

半導体装置およびその駆動方法

【課題】ゲート電極からのバイアス効果を大きくするとともに、オンからオフへのスイッチング速度を高速化することを可能とする。

【解決手段】第1伝導型の第1領域(第1p型領域p1)と、前記第1伝導型とは逆伝導の第2伝導型の第2領域(第1n型領域n1)と、第1伝導型の第3領域(第2p型領域p2)と、第2伝導型の第4領域(第2n型領域n2)とが順に接合されたサイリスタ2と、前記第3領域に形成されたゲート電極13と、前記第3領域が形成されるもので前記バルク半導体基板10に形成された第2伝導型のウエル領域11とを有する半導体装置1であって、前記サイリスタ2の第1領域側に第1電圧が印加され、前記サイリスタ2の第4領域側に前記第1電圧よりも高い第2電圧が印加され、前記ウエル領域11に前記第1電圧よりも高い電圧もしくは前記第1電圧と同等の電圧が印加されることを特徴とする。

(もっと読む)

電力変換装置およびワイドギャップバイポーラ半導体素子の駆動方法

【課題】ワイドギャップバイポーラ半導体素子を高信頼性かつ低損失で駆動でき、可制御電流を大きくできる電力変換装置を提供する。

【解決手段】この電力変換装置では、SiC−GTOサイリスタ1の稼動に先立ち、温度上昇用n型MOSFET11のゲート13に信号を印可してオンさせ、電源14 → アノード端子2 → ゲート端子4 → 抵抗12 → 温度上昇用n型MOSFET11 → 電源14の経路で温度上昇用電流(加熱電流)として約40Aの電流を流す。上記温度上昇用電流により、SiC−GTOサイリスタ1の温度を上昇させる。これにより、サイリスタ1の稼動により積層欠陥が増大したとしても、オン電圧の増大や最小ゲート点弧電流の増大、ターンオン時間の増大およびオフ時の電流の不均衡の増大などの劣化現象を抑制できる。

(もっと読む)

圧接型半導体装置およびその製造方法

【課題】本発明は、圧接型半導体装置に組み込む際に付着していた異物を発見しやすくし、より容易に取り除くことができる半導体素子およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体素子は、第1の導電型の第1の半導体層と、前記第1の半導体層の所定の領域上に積層された第2の導電型の第2の半導体層と、前記第1の半導体層上に形成された第1の電極層と、前記第2の半導体層上に形成された第2の電極層と、前記第1の電極層上に形成された絶縁層と、前記絶縁層および前記第2の電極層の上に貼り合わされた導電性シートとを備えたことを特徴とする。

(もっと読む)

光転送アレイ装置およびその製造方法、発光装置ならびに画像形成装置

【課題】 隣接する2つの光転送用発光素子間においてより確実に発光状態を転送することのできる光転送アレイ装置およびその製造方法を提供する。

【解決手段】 光転送アレイ装置1は、相互に間隔をあけて配置される複数のスイッチ素子Tと、隣接する2つのスイッチ素子T間に設けられ、隣接する2つのスイッチ素子Tのうち、一方のスイッチ素子Tからの光を他方のスイッチ素子Tに導く導波体17とを含んで構成される。導波体17の表面103は反射集光領域104を有し、反射集光領域104は、外方に凸となった凸曲面状に形成され、一方のスイッチ素子Tからの光が反射集光領域104で反射されると、他方のスイッチ素子Tに入射するように形成される。

(もっと読む)

絶縁ゲート型サイリスタ

【課題】

オン抵抗が低く、ゲートターンオフの可能な絶縁ゲート型サイリスタを提供する。

【解決手段】

絶縁ゲート型サイリスタは、第1導電型、高不純物濃度の第1電流端子半導体領域と、第1電流端子半導体領域上に形成された、第1導電型と逆導電型の第2導電型、低不純物濃度の第1ベース半導体領域と、第1ベース半導体領域上に形成された、第1導電型、低不純物濃度の第2ベース半導体領域と、第2ベース半導体領域上に形成された、第2導電型、高不純物濃度の第2電流端子半導体領域と、第2電流端子半導体領域表面から第1ベース半導体領域に向かう方向で、第2電流端子半導体領域を貫通し、第2ベース半導体領域に入り、その厚さの一部を残すように形成されたトレンチと、トレンチ内に形成された絶縁ゲート電極構造と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】サイリスタを構成する一部の領域を積層構造とすることで、素子面積の縮小化を図るとともにパンチスルー耐性の向上を図ることを可能とする。

【解決手段】第1伝導型の第1領域(第1p型領域p1)と、前記第1伝導型とは逆伝導の第2伝導型の第2領域(第1n型領域n1)と、第1伝導型の第3領域(第2p型領域p2)と、第2伝導型の第4領域(第2n型領域n2)とが順に接合されたサイリスタを有するとともに、前記第3領域にゲート電極23を有する半導体装置1において、前記第2領域(第1n型領域n1)は半導体基体(半導体基板21)に形成され、前記第2領域上に前記第1領域(第1p型領域p1)が形成されているものである。

(もっと読む)

高電圧炭化ケイ素半導体デバイスのための環境的に堅固なパッシベーション構造

炭化ケイ素における高電界半導体デバイスのための改良された終端構造を開示する。該終端構造は、高電界動作のための炭化ケイ素ベースのデバイスと、該デバイスにおける活性領域と、該活性領域のためのエッジ終端パッシベーションとを含み、該エッジ終端パッシベーションは、表面状態を満足させ、界面密度を低下させるための該デバイスの炭化ケイ素部分の少なくとも一部分上の酸化物層と、水素の取り込みを回避するため、および寄生容量を減少させ、捕捉を最小化するための該酸化物層上の窒化ケイ素の非化学量論的層と、該非化学量論的層および該酸化物層を封入するための該非化学量論的層上の窒化ケイ素の化学量論的層と、を含む。  (もっと読む)

(もっと読む)

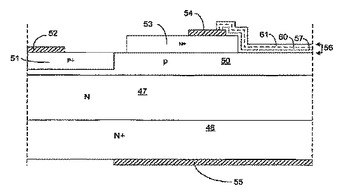

発光サイリスタ、発光サイリスタを用いた発光装置および画像形成装置

【課題】 受光感度を低下することなく発光強度を増大させた発光サイリスタを提供し、さらにこの発光サイリスタを用いた発光装置および画像形成装置を提供する。

【解決手段】 本発明の第1の発光サイリスタは、基板上101に、第1半導体層102、第2半導体層103、第3半導体層104、および第4半導体層107がこの順に積層された発光サイリスタにおいて、第2半導体層103と第3半導体層104のバンドギャップを等しくし、第1半導体層102と第4半導体層104のバンドギャップをそれらより大きくする。また、第3半導体層104を基板側の第1領域105と基板反対側の第2領域106に分け、第2領域106の不純物濃度を第1領域105よりも大きくする。さらに、第4半導体層107の不純物濃度を第2領域106以上にするとともに、第2半導体層103の不純物濃度を第1領域105以上にし、第1半導体層102よりも小さく設定する。

(もっと読む)

61 - 80 / 102

[ Back to top ]