Fターム[5F005AH02]の内容

Fターム[5F005AH02]に分類される特許

21 - 40 / 102

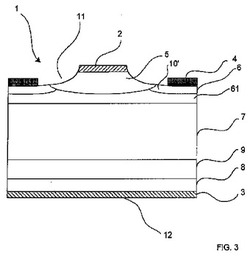

パワー半導体デバイス

4層npnp構造、カソード面11およびアノード面12があり、ゲート電極4を介してターンオフできるパワー半導体デバイス1。カソード電極2とアノード電極3との間に以下の順で複数の層が配置される。−外側縁によって囲まれ、中央領域がある第1導電型カソード層5、カソード層5はカソード電極2と直接の電気的コンタクトにある,−第2導電型ベース層6,−カソード層5よりも低いドーピング濃度を有する第1導電型ドリフト層7、アノード電極3と電気的コンタクトにある第2導電型アノード層8。ゲート電極4は、カソード面11上にカソード電極2の横に配置され、ベース層6と電気的コンタクトにある。ベース層6は、カソード層5の中央領域に接触している、連続的な層としての、第1の深さに最大ドーピング濃度がある少なくとも1つの第1の層61を具備する。第1の層61よりも高いドーピング濃度を有し、第1の層61とカソード層5との間に配置され、第1の層61のほうを向いているカソード層5の外側縁をカバーする第2導電型抵抗減少層10,10’,10’’、この中でカソード層5の外側縁とベース層6との間の接合での抵抗が低減される。 (もっと読む)

駆動回路、駆動装置及び画像形成装置

【課題】発光サイリスタ等の被駆動素子の破壊を防止して信頼性の向上を図る。

【解決手段】ドライバICは、第1端子と、第2端子と、前記第1端子及び前記第2端子間の導通状態を制御する制御端子と、を有する被駆動素子が複数配列された被駆動素子アレイを時分割駆動する回路である。被駆動素子アレイは、隣接配置された被駆動素子毎に被駆動素子群が形成され、各被駆動素子群における第1端子群、第2端子群、及び制御端子群の内、各第2端子群がグランドにそれぞれ接続され、各制御端子群が共通母線にそれぞれ接続されている。ドライバICは、各共通母線をそれぞれ駆動する複数のゲート駆動用バッファ162を備えている。各バッファ162は、電源VDDと共通母線OUTとの間に直列に接続されたスイッチ用PMOS403及び降圧用PMOS406と、共通母線OUTとグランドGNDとの間に接続されたスイッチ用PMOS404とを有している。

(もっと読む)

半導体複合装置、この製造方法、光プリントヘッド及び画像形成装置

【課題】製造工程を簡略化して低コスト化を図る。

【解決手段】半導体複合装置は、シフトレジスタと、これにより時分割駆動される半導体薄膜からなる発光サイリスタアレイとにより構成されている。この製造方法は、例えば、シフトレジスタを構成する複数の回路構成素子243が形成されたシリコン基板241を用意する。シフトレジスタにより駆動される複数の発光サイリスタ261〜264が配列された結晶構造を持った半導体薄膜からなる発光サイリスタアレイを、パッシベーション膜242を介してシリコン基板241上に貼着する。フォトリソグラフィ法により、複数の回路構成素子243間を電気的に接続してシフトレジスタを形成すると共に、そのシフトレジスタ及び複数の発光サイリスタ261〜264間を電気的に接続するメタル配線265〜267を形成する。

(もっと読む)

半導体装置

【課題】高温度における電圧上昇率(dV/dt)耐量を向上し、誤動作を防止することができるサイリスタを提供する。

【解決手段】半導体層(20)の一方の主面において、第1の導電型(p型)をもつ第1の半導体層(21)上に第1の主電極(11)が形成され、前記第1の導電型と反対の第2の導電型(n型)をもち前記第1の半導体層中に局所的に形成された第2の半導体層(24)と、該第2の半導体層と前記第1の半導体層とに接続するゲート電極(13)とが、前記第1の主電極が形成されていない箇所に形成され、

前記半導体層の他方の主面において、第2の主電極(12)が形成され、

前記第1の主電極と前記第2の主電極との間に電流が流れる、サイリスタとしての動作をする半導体装置であって、

前記ゲート電極と前記第1の主電極との間に接続され、SBD(31、32)から成る双方向ダイオードを具備することを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】レイアウト面積をほとんど増加させることなく、SCRのラッチアップ耐性を向上させ、かつラッチアップ耐性の方向依存を低減する。

【解決手段】P型半導体基板1に環状のN型ウエル3が形成されている。P型半導体基板1とは間隔をもってN型ウエル3に互いに間隔をもってN型拡散層5及びP型拡散層7が形成されている。N型拡散層5は、N型拡散層3で囲まれた位置のP型半導体基板1の周囲を取り囲んで環状に形成されている。N型拡散層3で囲まれた位置のP型半導体基板1に、N型拡散層3とは間隔をもって、かつ互いに間隔をもって、N型拡散層9及びP型拡散層11が形成されている。

(もっと読む)

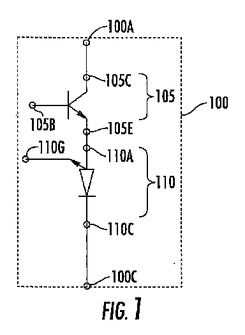

非負の温度係数及び関連した制御回路を有するワイド・バンドギャップ・バイポーラ・ターンオフ・サイリスタ

アノード、カソード及びゲート端子を有するワイド・バンドギャップ・サイリスタと、ベース、コレクタ及びエミッタ端子を有するワイド・バンドギャップ・バイポーラ・トランジスタを含む。バイポーラ・トランジスタとサイリスタとが直列接続されるように、バイポーラ・トランジスタのエミッタ端子は、サイリスタのアノード端子に直接結合される。バイポーラ・トランジスタ及びサイリスタは、ワイド・バンドギャップ・バイポーラ・パワー・スイッチング・デバイスを特徴付け、ワイド・バンドギャップ・バイポーラ・パワー・スイッチング・デバイスは、非導通状態と、ベース端子への第一制御信号の印加及びゲート端子への第二制御信号の印加に応答してバイポーラ・トランジスタのコレクタ端子に対応する第1主端子とサイリスタのカソード端子に対応する第2主端子との間に電流を流すことができる導通状態との間を切り替えるように構成される。関連した制御回路も開示される。  (もっと読む)

(もっと読む)

サイリスタ

【課題】サイリスタ内の残存キャリアがサイリスタ相互に及ぼす影響を抑制し、転流時臨界電圧上昇率を改善し、小型化を図ることができ、更に電流上昇率耐量を向上することができるサイリスタを提供する。

【解決手段】逆並列接続構造を有するサイリスタ1において、第1の主サイリスタと第2の主サイリスタとの間にpn接合によって双方を分離する接合分離領域210が配設される。第1の主サイリスタは第5の半導体領域25、第3の半導体領域23、第1の半導体領域21及び第7の半導体領域27により構成される。第2の主サイリスタは第4の半導体領域24、第2の半導体領域22、第7の半導体領域27及び第8の半導体領域28により構成される。

(もっと読む)

発光サイリスタ、発光素子アレイ、発光装置および画像形成装置

【課題】 ベース層のキャリア濃度および厚み寸法を大きく設定することなく、発光強度に対する電流増幅率βの影響を抑制することのできる発光サイリスタ、発光素子アレイ、発光装置および画像形成装置を提供することである。

【解決手段】 発光サイリスタは、基板上に第1半導体層、第1半導体層と反対導電型の第2半導体層、第1半導体層と同じ導電型の第3半導体層、および第1半導体層と反対導電型の第4半導体層がこの順に積層されており、第3半導体層のバンドギャップは、第2半導体層のバンドギャップと略同一、かつ、第1および第4半導体層のバンドギャップより狭幅であり、第3半導体層は、基板側の第1領域と基板と反対側の第2領域とからなり、かつ、第1領域の不純物濃度は1×1016(cm−3)未満である。

(もっと読む)

3端子サイリスタ

【課題】ターンオン時に流れる主電流の電流密度を低くして、ターンオン時に破壊されにくい構造を有する3端子サイリスタを提供する。

【解決手段】p型アノード層110における第2主面側にはアノード電極132が形成され、n+型カソード領域116及びp+型第1オーミック領域118における第1主面側にはカソード電極128が形成され、p+型第2オーミック領域120における第1主面側にはゲート電極130が形成された3端子サイリスタにおいて、p型第2ベース層114におけるn+型カソード領域116、p+型第1オーミック領域118及びp+型第2オーミック領域120よりも深い領域に、平面的に見てp+型第2オーミック領域120からn+型カソード領域116に延在するように、p型第2ベース層114よりも高濃度のp型不純物を含有するp+型埋込拡散層122が形成されている3端子サイリスタ100。

(もっと読む)

バイポーラパンチスルー半導体装置およびそのような半導体装置の製造方法

2層構造を少なくとも具備する、半導体基板(1)を備えたバイポーラパンチスルー半導体装置が提供される。層の1つは、第1の導電型のベース層(10)である。基板は、第1の電気コンタクト(2)を備えた第1の主側面(11)および第2の電気コンタクト(3)を備えた第2の主側面(12)を具備する。第1の導電型のバッファ層(4)は、ベース層(10)上に配置される。第1の導電型の第1の領域(51、51’)と第2の導電型の第2の領域(52、52’)とを交互に具備する第1の層(5)は、バッファ層(4)と第2の電気コンタクト(3)との間に配置される。第2の領域(52、52’)は、最大2μmの深さおよび接合プロファイル(それは、最大1μmで最大ドーピング濃度の90%から10%まで低下する)を備えた活性化領域である。 (もっと読む)

低角度オフカット炭化ケイ素結晶上の安定なパワーデバイス

【課題】炭化ケイ素中の結晶欠陥を低減することができるプロセスならびにその結果得られる構造体およびデバイスを提供すること。

【解決手段】炭化ケイ素ベースのパワーデバイスが、<0001>方向に対して8°よりも小さいオフアクシス角を形成する平坦な表面を有する炭化ケイ素ドリフト層を含む。

(もっと読む)

電流シフト領域を有する半導体デバイスおよび関連方法

半導体デバイスは、第1の伝導形を有する半導体バッファ層と、バッファ層の表面上にあって第1の伝導形を有する半導体メサとを含む。さらに第2の伝導形を有する電流シフト領域が半導体メサと半導体バッファ層との間の隅に隣接して設けられ、第1と第2の伝導形が互いに異なる伝導形である。関連する方法も開示される。  (もっと読む)

(もっと読む)

III族窒化物系化合物半導体素子及びその製造方法

【課題】積層された各層に平面的に電極が形成された、III族窒化物系化合物半導体素子

【解決手段】pnpトランジスタ100は、基板10の上に、図示しないバッファ層を介して、p型GaN層11、n型GaN層12、p型GaN層13を順に形成した後、ケミカルポリシングにより露出部である傾斜面11t、12t及び13tを形成し、そこに各々、コレクタ電極C、ベース電極B、エミッタ電極Eを形成して構成したものである。図1のpnp型トランジスタ100は、水平形状が1辺が500μmの矩形状で、その外周の1辺に水平面と10度の角度を成す傾斜面が形成されている。p型GaN層11、n型GaN層12及びp型GaN層13の膜厚はいずれも1μmであり、p型GaN層11の傾斜面11t、n型GaN層12の傾斜面12t及びp型GaN層13の傾斜面13tの幅はいずれも約5.8μmである。

(もっと読む)

点滅回路

【課題】消費電力を少なくするとともに、部品点数を少なくすることで低コスト化を図った点滅回路を提供することを目的とする。

【解決手段】発光サイリスタ20の第1端子であるアノード端子は、抵抗13を介して電源VDDに接続するとともにコンデンサ15を介してグランドに接続し、第2端子であるカソード端子は抵抗14を介してグランドに接続し、第3端子であるゲート端子は抵抗11と抵抗12の直列回路の接続中心に接続する。

(もっと読む)

バイポーラ型半導体装置

【課題】表面欠陥に起因する積層欠陥が生じても、リーク電流を低減でき、最小点弧電流の増大を防止できるバイポーラ型半導体装置を提供する。

【解決手段】n型の半導体基板とその半導体基板上にエピタキシャル成長により順に形成された複数の半導体層とを備えたシリコンカーバイト(SiC)を母材とする主構造体1と、上記主構造体1の半導体層の最上層に形成され、半導体基板のオフ方向に対してストライプ方向(矢印R1)が略直交するメサストライプ部2と、上記メサストライプ部2のメサ2a上に形成されたアノード電極3と、上記半導体基板の裏面に形成されたカソード電極5と、上記メサストライプ部2のメサ2a間に露出する半導体層上に形成されたゲート電極4とを備える。

(もっと読む)

半導体装置

【課題】高耐圧と速い動作とを共に実現することが可能な半導体装置を提供する。

【解決手段】N型基板1上に形成されたN型の半導体層2と、この半導体層2の表面に形成されたP型の第1拡散層4と、半導体層2の表面に、第1拡散層4と互いに離間し、かつ、第1拡散層4を囲むように形成された、P型の第2拡散層4と、第1拡散層4の表面に形成された、P型の第3拡散層5と、第2拡散層4の表面に形成された、P型の第4拡散層7と、第1拡散層4の表面に形成され、第3拡散層5と電気的に接続された、N型の第5拡散層6と、第2拡散層4の表面と半導体層2の表面とをまたぐように形成され、第4拡散層7と電気的に接続された、N型の第6拡散層8とを含む、PN接合型ダイオードを有する半導体装置を構成する。

(もっと読む)

静電気保護素子

【課題】特殊な工程や、保護抵抗の挿入なしに被保護回路を保護できる静電気保護素子を提供する。

【解決手段】P型の半導体基板1と、半導体基板1に形成された、N型の第1不純物層3を備える。第1不純物層3内には、ゲートとして動作するP型の第2不純物層5を備える。第2不純物層5には、カソードとして動作するN型の第3不純物層6を備える。また、第2不純物層5から一定距離離間した第1不純物層3内には、N型の第4不純物層4を備える。第4不純物層4内には、アノードとして動作するP型の第5不純物層8と、N型の第6不純物層9とを備える。そして、本静電気保護素子は、第4不純物層4の不純物濃度が第1不純物層3の不純物濃度よりも高く、かつ第4不純物層4の底部が第2不純物層5の底部より深くなっている。

(もっと読む)

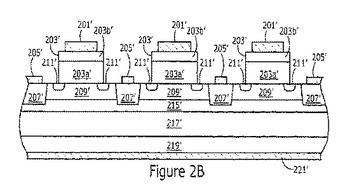

発光素子チップ、露光装置および画像形成装置

【課題】本発明は、発光素子アレイの構造を利用して信号線の引き回しの複雑化を軽減した発光素子チップを提供する。

【解決手段】発光素子チップ51aは、GaAs系の半導体で構成され、基板200上に形成されたpnpn構造からなる、発光部120の発光サイリスタ401と、設定部130の転送サイリスタ402と、制御部140の論理演算素子403とを備え、基板200上にp型の第1半導体層201とn型の第2半導体層202と、p型の第3半導体層203と、n型の第4半導体層204とを積層し、その後、予め定められた箇所をエッチングして形成される。

(もっと読む)

半導体サイリスタ装置

【目的】配線レイアウトの関係で他の配線層の電位に起因して発生する虞のあるリーク電流を回避し得る半導体サイリスタ装置を提供する。

【構成】半導体基板と、各々が互いに接合型を異にし該半導体基板内で隣接して設けられることによって1つのサイリスタ素子を構成する2つのトランジスタと、該半導体基板上に設けられて該トランジスタの一方に接地電位を供給するための第1配線層と、該半導体基板上に設けられて該トランジスタの他方に電源電位を供給するための第2配線層と、を含む半導体サイリスタ装置であり、該第1配線層は、該半導体基板のうちで該2つのトランジスタが隣接し合う領域を被覆している。

(もっと読む)

横方向シリコン制御整流素子及びこれを備えるESD保護素子

【課題】保持電圧を高くすること、及び小型化の両方を実現出来る横方向シリコン制御整流素子及びこれを備えるESD保護素子を提供する。

【解決手段】第1の導電型であるP型シリコン基板2上に形成され、P型シリコン基板2上に形成される第2の導電型であるNウェル領域3と、Nウェル領域3上に形成される第1の導電型であるP+アノード領域4と、P型シリコン基板2上に形成される第2の導電型であるN+カソード領域7とを備える横方向シリコン制御整流素子において、Nウェル領域3に接触して形成される第2の導電型であるN型半導体領域22と、N型半導体領域22上に形成される第1の導電型であるP型半導体領域21とを備える。

(もっと読む)

21 - 40 / 102

[ Back to top ]