Fターム[5F005AH02]の内容

Fターム[5F005AH02]に分類される特許

41 - 60 / 102

保護回路

【課題】静電気印加時には、高速にトリガし、通常使用時には、ラッチアップが起きにくいサイリスタ型の保護回路を提供する。

【解決手段】第1の端子と第2の端子との間に、一端が第2の端子に接続された容量素子と、半導体基板上に設けられたサイリスタであって、上記第1の端子に接続されたアノードと、上記第2の端子に接続された第1カソードと、アノードと第1カソードとの間に配置され上記容量素子の他端に接続された第2カソードと、を備えたマルチカソードサイリスタと、を用いることにより、アノードと第2カソード間で開始したサイリスタ動作がアノードと第1カソード間のサイリスタ動作を誘起するようにした。

(もっと読む)

半導体装置の製造方法

【課題】逆回復時のdV/dtの増加を抑制し、逆回復時の電圧電流波形の振動を抑制し、高速・低損失特性とソフトリカバリー特性の両者を同時に向上させる半導体装置の製造方法を提供すること。

【解決手段】リンを含むn型で高比抵抗のFZのバルクウェハ300にて通常のプロセス処理を行い、一方の表面にpアノード層301、アノード電極302を形成する。その後、プロトン等の軽イオン照射303を行う。照射後、裏面から所定の厚さまで、切削する。切削後、裏面の切削面305にリン等のn型不純物イオン(不純物307)のイオン注入306を行い、熱処理を行い、nカソード層308を形成し、その上にカソード電極309を形成する。

(もっと読む)

メサ型半導体装置及びその製造方法

【課題】メサ型半導体装置及びその製造方法において、耐圧を向上させると共にリーク電流を低減する。

【解決手段】半導体基板1の表面にN−型半導体層2を形成し、その上層にP型半導体層3を形成する。その後、P型半導体層3の表面から、PN接合部JC、N−型半導体層2、半導体基板1の厚さ方向の途中にかけてエッチングし、半導体基板1に近づくに従って幅が大きくなるメサ溝8を形成する。その後、前記エッチングにより生じたメサ溝8の内壁のダメージ層を、ウェットエッチングにより除去すると共に、P型半導体層3の表面に近い領域において、P型半導体層3の表面に近づくに従って幅が大きくなるようにメサ溝8を加工する。その後、半導体基板1及びそれに積層された各層からなる積層体をダイシングする。

(もっと読む)

半導体装置の製造方法

【課題】リーク電流の発生なくp型領域やn型領域を半導体基板上に結晶成長させてなるサイリスタ構成の素子を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1の表面側にp型領域、n型領域、p型領域、およびn型領域がこの順に接して設けられた素子を備え、少なくとも1つの領域が半導体基板1の表面に結晶成長させた結晶成長層からなる半導体装置の製造方法において、第1n領域25および第2p領域27を結晶成長層として形成する際には、半導体基板1上に第1絶縁膜17と第2絶縁膜19との積層膜を成膜する第1工程と、第2絶縁膜19のエッチングに続けて第1絶縁膜17をウェットエッチングすることによって半導体基板1に達する開口を形成する第2工程と、開口底部に露出する半導体基板1の表面に、第1n領域25および第2p領域27を選択的に結晶成長させる第3工程とを行う。

(もっと読む)

半導体装置およびその製造方法およびその駆動方法

【課題】サイリスタ動作時に、寄生バイポーラトランジスタを作らせず、書き込みのディスターブの発生を防止して、誤書き込みを防止することを可能にするSRAM型の半導体装置とその製造方法を提供する。

【解決手段】半導体基板11に形成されたサイリスタ形成領域21を分離する素子分離領域12と、サイリスタ形成領域21に形成されていて、p型の第1領域(第1p型領域)p1と、n型の第2領域(第1n型領域)n1と、p型の第3領域(第2p型領域)p2と、n型の第4領域(第2n型領域)n2とが順に接合されたサイリスタT1、T2と、第2p型領域p2の下部に形成されたn型の第5領域(第1ウエル領域)31を有する半導体装置1において、第5領域31の底部および素子分離領域12の下部に接合するp型の第6領域(第2ウエル領域)32を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】サイリスタの第2n型領域n2表面に金属シリサイド層を形成しても、第2n型領域n2と第2p型領域p2間でショートを起こさないようにすることを可能とする。

【解決手段】第1p型領域p1(第1領域)と、第1n型領域n1(第2領域)と、第2p型領域p2(第3領域)と、第2n型領域n2(第4領域)とが順に接合されたサイリスタT1が形成された半導体装置1であって、第2p型領域p2は、素子分離領域13で分離された半導体基板11に形成され、第2p型領域p2上にゲート絶縁膜21を介して形成されたゲート電極22と、ゲート電極22の両側の側壁に形成されたサイドウォール23、24を有し、2n型領域n2は、その一方側が第2p型領域p2の他方側と素子分離領域13(13−1)との接合部上を被覆し、その他方側がサイドウォール23の他方側に接合していることを特徴とする。

(もっと読む)

半導体装置の駆動方法

【課題】n型のウエル領域に設定される電圧を調整して、寄生素子に無駄な電流が流れないようにすることを可能とする。

【解決手段】第1伝導型(p型)の第1領域(第1p型領域p1)と、前記第1伝導型とは逆伝導の第2伝導型(n型)の第2領域(第1n型領域n1)と、p型の第3領域(第2p型領域p2)と、n型の第4領域(第2n型領域n2)とが順に接合されたサイリスタTと、前記第2p型領域p2にゲート(ゲート電極22)形成され、前記第2p型領域p2の下部にn型のウエル領域31を有する半導体装置の駆動方法であって、前記第1p型領域p1をアノードとし、前記第2n型領域n2をカソードとし、前記サイリスタTがオン状態のときの前記ウエル領域31の電圧を前記ウエル領域31から前記第2n型領域n2に電流が流れるように設定することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタとサイリスタとを同一半導体基板に形成するとき、MOSトランジスタのエクステンション領域に対するサーマルバジェットの問題を回避することを可能にする。

【解決手段】第1p型領域p1、第1n型領域n1、第2p型領域p1、第2n型領域n2が順に接合され、第2p型領域p1にゲートが形成されたサイリスタTと、ソース・ドレイン領域43、44、53、54とエクステンション領域41、42、51、52を備えたMOSトランジスタ3、5とを半導体基板11に形成する半導体装置の製造方法であって、ゲート電極22の側壁に形成した第1サイドウォール23、24(図示せず)を用いてサイリスタTを完成させた後に第1サイドウォール23、24を除去してから、エクステンション領域41、42、51、52を形成することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】サイリスタ構成の半導体装置において、第2p型領域上に第1n型領域、第1p型領域を積層して形成しても、第1p型領域と第2p型領域とがショートを起こさないようにすることを可能とする。

【解決手段】p型の第1p型領域p1(第1領域)と、n型の第1n型領域n1(第2領域)と、p型の第2p型領域p2(第3領域)と、n型の第2n型領域n2(第4領域)とが順に接合されたサイリスタT1が素子分離領域13で分離された半導体装置1であって、第2p型領域p2は、素子分離領域13で分離された半導体基板11に形成され、第1n型領域n1は、第2p型領域p2の一部上に形成されて、かつ、前記第1n型領域n1と第2p型領域p2との界面の一端部が素子分離領域11の側壁部に接合するように形成されていることを特徴とする。

(もっと読む)

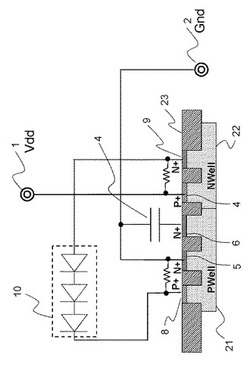

高速トリガーESD保護デバイスおよびその設計方法

【課題】ICに現れるオーバーシュートが低減可能なESD保護デバイス、およびその設計方法の提供。

【解決手段】主ESDデバイス10と、低減された電圧で、ESD電流を流すために、主ESDデバイスのトリガーノードに接続されたトリガーデバイス20とを含むESD保護回路の設計方法。このトリガーデバイス20は、ESD電流のための最初の電流経路中に配置される。この最初の電流経路中に、オフ状態からオン状態にトリガーされる少なくとも1つのトリガー要素を有する。この要素のトリガー速度が考慮され、その設計はそのトリガー速度が増加するように最適化される。更に、少なくとも1つのトリガー要素が、速いトリガー速度を得るために、所定のタイプ、好適にはゲート型ダイオードタイプから選択されESD保護回路。

(もっと読む)

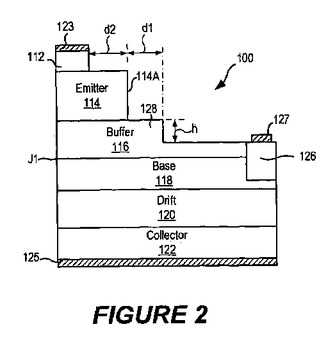

メサ構造とメサ段差を含むバッファ層とを備えた電力半導体デバイス

バイポーラ接合トランジスタが、第1の導電型を有するコレクタと、このコレクタ上の、第1の導電型を有するドリフト層と、このドリフト層上の、第1の導電型と反対の第2の導電型を有するベース層と、このベース層上の、低濃度でドープされ第1の導電型を有しベース層とp−n接合部を形成するバッファ層と、このバッファ層上の第1の導電型を有し側壁を有するエミッタメサとを含む。バッファ層は、エミッタメサの側壁の近傍でそこから横方向に間隔を置いて配置されたメサ段差を含み、エミッタメサの下のバッファ層の第1の厚さは、メサ段差外側のバッファ層の第2の厚さよりも厚い。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】実効的なエピタキシャル成長面積を拡大して、エピタキシャル成長時に発生するファセットの影響を抑えることを可能とする。

【解決手段】第1p型領域p1と、第1n型領域n1と、第2p型領域p2と、第2n型領域n2とが順に接合された第1サイリスタT1と第2サイリスタT2とが素子分離領域14で分離された状態に形成された半導体装置1であって、第1、第2サイリスタT1、T2の第1n型領域n1が素子分離領域14を挟んで設けられ、各第1n型領域n1上に選択エピタキシャル成長により形成される第1、第2サイリスタT1、T2の各第1p型領域p1が、各第1n型領域n1間の素子分離領域14上で連続した状態に形成されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】エピタキシャル成長層上に形成したシリサイド層やエピタキシャル成長層と半導体基板とがショートを起こすのを防止することを可能にする。

【解決手段】半導体基板11に形成された素子分離領域14によって分離された該半導体基板11の素子形成領域12と、前記半導体基板11上に形成された絶縁膜41と、前記素子形成領域12の選択エピタキシャル成長させる領域上を含むように前記絶縁膜41に形成された開口部42と、前記開口部42内の半導体基板11の素子形成領域12より選択エピタキシャル成長により形成された半導体層15とを有することを特徴とする。

(もっと読む)

サイリスタ

【課題】高いゲート・カソード間耐圧を有するサイリスタを提供する。

【解決手段】第1導電型の半導体基板の第1主面には、第1導電型の不純物領域であるカソード領域と、前記カソード領域を取り囲むような第2導電型の不純物領域であるアノード領域と、前記カソード領域と前記アノード領域との間にはメサ溝部とを有し、前記半導体基板の第2主面には、第2導電型の不純物領域部であるゲート領域と、前記第1主面から前記ゲート領域まで達する深さの前記メサ溝部と、前記第1主面の前記カソード領域にはカソード金属電極、前記アノード領域にはアノード金属電極を有し、前記第2主面の前記ゲート領域上にはゲート金属電極を有することを特徴とするサイリスタであり、ゲート・カソード間距離が充分に確保できる構造であるため、ゲート・カソード間耐圧を高く確保することができる。

(もっと読む)

バイポーラ素子及びその製造方法

【課題】メサ型バイポーラトランジスタあるいはサイリスタでは、エミッタ層あるいはアノード層からベース層あるいはゲート層に注入されたキャリアが横方向に拡散し再結合する結果、小型化やスイッチング周波数の向上が困難であった。

【解決手段】エミッタ層あるいはアノード層を高濃度および低濃度からなる二層で構成し、この低濃度層と同一の不純物密度を有する同一の半導体からなる再結合抑制半導体領域をベース層またはゲート層と表面保護絶縁膜とに接して存在させるとともに、この再結合抑制半導体領域の幅をキャリアの拡散距離以上に設定する。このことにより、バイポーラトランジスタの小型化やサイリスタのスイッチング周波数向上を、性能を損なわず実現できる効果がある。また、上記バイポーラトランジスタの高濃度エミッタ層上に、正孔バリア層、伝導帯不連続緩和層、及びエミッタコンタクト層を順次積層することにより、電流増幅率を大幅に向上できる効果がある。

(もっと読む)

絶縁ゲート型サイリスタ

【課題】

オン抵抗が低く、ゲートターンオフの可能な絶縁ゲート型サイリスタを提供する。

【解決手段】

絶縁ゲート型サイリスタは、第1導電型、高不純物濃度の第1電流端子半導体領域と、

第1電流端子半導体領域上に形成された、第1導電型と逆導電型の第2導電型、低不純物

濃度の第1ベース半導体領域と、第1ベース半導体領域上に形成された、第1導電型、低不純物濃度の第2ベース半導体領域と、第2ベース半導体領域上に形成された、第2導電型、高不純物濃度の第2電流端子半導体領域と、第2電流端子半導体領域表面から第1ベース半導体領域に向かう方向で、第2電流端子半導体領域を貫通し、第2ベース半導体領域に入り、その厚さの一部を残すように形成されたトレンチと、トレンチ内に形成された絶縁ゲート電極構造と、を有し、トレンチが第2ベース半導体領域上部を複数の部分に分割し、分割された各部分を取り囲むように形成されている。

(もっと読む)

半導体装置及びその駆動方法

【課題】ターンオフ時間を短くできるサイリスタを有する半導体装置を提供する。

【解決手段】基板に第1導電型の第1半導体領域が形成され、その表層部に第2導電型の第2半導体領域と第2導電型の第3半導体領域(アノードAN)と第1導電型の第4半導体領域(アノードゲートAG)が、第2半導体領域の表層部に第1導電型の第5半導体領域(カソードCA)と第2導電型の第6半導体領域(カソードゲートCG)が形成され、第1及び第2半導体領域の境界から第2及び第5半導体領域の境界までの領域の第2半導体領域上にゲート絶縁膜及びゲート電極MGが、第3半導体領域に負荷素子が形成されてサイリスタSCRが構成された半導体装置において、サイリスタをオンからオフにする際に、アノードより高電位をアノードゲートに印加し、アノードとアノードゲートでサイリスタ内部に構成されるダイオードを降伏させてアノードの電位を制御して駆動する。

(もっと読む)

炭化珪素バイポーラ型半導体装置

【課題】メサ構造をもつ炭化珪素バイポーラ型半導体装置において、素子の表面付近に存在する欠陥核を起点とした積層欠陥の発生およびその面積拡大を抑制し、これにより順方向電圧の増加を抑制する。

【解決手段】第1導電型炭化珪素単結晶基板、第1導電型炭化珪素ドリフト層、第2導電型炭化珪素電荷注入層および該炭化珪素電荷注入層よりもドーピング密度が高い第2導電型の高ドーピング層が、この順序にて積層してなり、前記炭化珪素ドリフト層から前記高ドーピング層側の素子表面に至るメサ構造を有し、前記高ドーピング層の厚さが15nm〜1.5μmであり、かつ、前記高ドーピング層における最大ドーピング密度が1×1020cm-3〜2×1021cm-3であることを特徴とする炭化珪素バイポーラ型半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】大電流容量を有する半導体装置を提供する。

【解決手段】半導体装置は、エピウエハ110と、絶縁膜と、第1の電極と、導電層と、第2の電極160とを備えている。エピウエハ110は、高欠陥領域111と、高欠陥領域111よりも欠陥密度の低い低欠陥領域112とを含み、主表面113と、主表面113と反対側の裏面114とを有する。絶縁膜は、エピウエハ110の主表面113における高欠陥領域111を覆うように形成される。第1の電極は、低欠陥領域の上に形成され、絶縁膜を介して隣り合う。導電層は、絶縁膜を介して隣り合う第1の電極を電気的に接続する。第2の電極160は、エピウエハ110の裏面114上に形成されている。

(もっと読む)

垂直型電流制御型シリコン・オン・インシュレータ(SOI)デバイス及びそれを形成する方法

【課題】 CMOS集積回路(IC)のための静電放電(ESD)保護デバイスとして用いるのに適した電流制御シリコン・オン・インシュレータ(SOI)デバイスを提供すること。

【解決手段】 垂直型シリコン制御整流器(SCR)、垂直型バイポーラ・トランジスタ、垂直型キャパシタ、抵抗器及び/又は垂直型ピンチ抵抗器のようなデバイスを有するシリコン・オン・インシュレータ(SOI)集積回路(IC)チップ、及びそれらのデバイスを作製する方法である。デバイスは、SOI表面層及び絶縁体層を通って基板に達するシード孔内に形成される。例えばN−型埋め込み拡散部が、基板内のシード孔を通って形成される。ドープされたエピタキシャル層が、埋め込み拡散部上に形成され、このドープされたエピタキシャル層は、例えばP−型層及びN−型層などの多数のドープ層を含むことができる。ドープされたエピタキシャル層上に、例えばP−型のポリシリコンを形成することができる。コンタクト・ライナ内に、埋め込み拡散部へのコンタクトが形成される。

(もっと読む)

41 - 60 / 102

[ Back to top ]