Fターム[5F033HH21]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Ta (2,035)

Fターム[5F033HH21]に分類される特許

2,001 - 2,020 / 2,035

銅表面に対する表面還元、不動態化、腐食防止、および活性化のためのシステムおよび方法

【課題】

【解決手段】露出された導電材料を不動態化するシステムおよび方法は、処理チャンバ内に基板を配置する工程と、処理チャンバ内に水素種を注入する工程とを備える。処理チャンバ内で、水素種のプラズマが形成される。基板の上面から、表面層の種が還元される。還元された表面層の種は、処理チャンバから取り除かれる。

(もっと読む)

半導体装置、半導体装置の製造方法

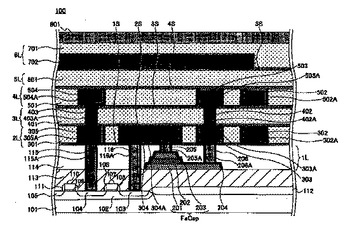

本発明では、水素またはH2Oの拡散を防止することで強誘電体キャパシタの劣化を防止し、高品質の強誘電体キャパシタを有する半導体装置を提供することを課題とする。そのため、本発明では、基板上に形成された強誘電体キャパシタと、前記強誘電体キャパシタ上に形成された配線構造とを有する半導体装置であって、前

記配線構造は、層間絶縁層と当該層間絶縁層中に形成されたCu配線部を含み、前記層間絶縁層に面するように、水素拡散防止層を含むエッチングストッパー層が形成されていることを特徴とする半導体装置を用いた。  (もっと読む)

(もっと読む)

レーザ除去タングステン・ヒューズ用配線保護要素(電気的構造体および形成方法)

【課題】集束放射線(52)によるヒューズ・リンク除去中に電気的構造体(25)を保護するための構造および対応する形成方法を提供すること。

【解決手段】構造体(1)は、ヒューズ要素(2)と、保護プレート(10)と、第1誘電体層(14)と、第2誘電体層(4)とを含む。構造体(1)は、半導体デバイス(5)内に形成される。保護プレート(10)は、ダマシン・プロセスを使用して第1誘電体層(14)内に形成される。第2誘電体層(4)は、保護プレート(10)および第1誘電体層(14)上に形成される。ヒューズ要素(2)は、第2誘電体層(4)上に形成される。ヒューズ要素(2)は、レーザビーム(52)で切断されるように構成される。第2誘電体層(4)の誘電率は、第1誘電体層(14)の誘電率より大きい。保護プレート(10)は、第1誘電体層(14)をレーザビーム(52)のエネルギーから遮蔽するように構成される。

(もっと読む)

半導体装置及びその製造方法

底部電極(11)及び又はキャパシタ誘電体上に導電性平滑化層(16、19)を形成することにより、幾何学的に高くされた電場を低下させると共に、電極を平滑化することで、形成されるMIMキャパシタの信頼性を向上させることができる。一実施形態において、難溶性窒化物で形成された第1のキャッピング層(14)上には、難溶性金属又は難溶性金属リッチ窒化物を含む第1の層(16)が形成される。更に、キャパシタ誘電体上には、難溶性金属(18)又は難溶性金属リッチ窒化物を含む第2の層(19)が形成される。導電性平滑化層(16、19)は、例えば、ゲート電極とゲート誘電体との間のトランジスタ等の他の半導体装置にも使用される。  (もっと読む)

(もっと読む)

低静電容量配線のための調節可能な自己整合型エアーギャップ誘電体

【課題】 低静電容量配線のための調節可能な自己整合型エアーギャップ誘電体を形成すること。

【解決手段】 調節可能で自己整合型の低静電容量集積回路のエアーギャップ構造は、相互接続層上で第二相互接続部に隣接する第一相互接続部と、該第一相互接続部及び該第二相互接続部の隣接する側部に沿って形成されたスペーサと、該第一相互接続部と該第二相互接続部との間に形成されたエアーギャップとを含む。エアーギャップは、第一相互接続部及び第二相互接続部の少なくとも一方の上面より上方で、かつ、該第一相互接続部及び該第二相互接続部の少なくとも一方の下面より下方に延び、スペーサ間の距離が該エアーギャップの幅を定める。エアーギャップは、第一相互接続部及び第二相互接続部の隣接する側部に自己整合する。

(もっと読む)

金属の化学的機械的研磨用の新規なスラリー

一般に集積回路の製造に有用な、金属を取り除くための、及び、特に貴金属の化学的機械的研磨用の、スラリーは、過ヨウ素酸、研磨剤、及び緩衝系を組み合わせることによって、形成されてもよく、ここでそのスラリーのpHは、約(4)と約(8)との間にある。

(もっと読む)

(もっと読む)

磁界を形成する導体

本発明は、電流が電気導体を流れるときに回路構成の少なくともさらにもう1つの部分に作用する磁界を生成する少なくとも1つの電気導体(40)を有する集積回路構成を提供している。電気導体(40)は、この回路構成のこの少なくともさらにもう1つの部分に向かって方向付けられた第1の側を有し、導電材料の主要線(41)と、その第1の側に接続され、磁性材料から成る少なくとも1つの磁界形成ストリップ(42)を備える。磁界形成ストリップ(42)により、電気導体(40)上の磁界プロファイルの不均一性が、低下される。  (もっと読む)

(もっと読む)

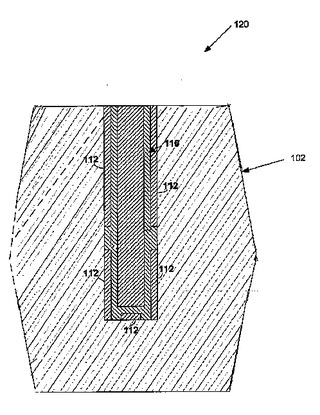

無電解メッキ化学反応を用いた深いビアシードの修復

高アスペクト比ビア内に連続シード層を形成する方法とそれに関連付けられる構造体を記載する。この方法は、基板内に凹部(104)を形成する段階と、凹部内に非連続金属層を形成する段階と、凹部内の非連続金属層(112)と、少なくとも1つの非堆積領域(109)を活性化させる段階と、凹部内の非連続金属層及び少なくとも1つの非堆積領域上にシード層(116)を無電解メッキする段階と、実質的にボイドがなく、金属が充填された凹部を形成するようシード層上に金属充填層を形成する段階を含む。  (もっと読む)

(もっと読む)

製造方法

【課題】 基板内に導電性構造体を形成する方法を提供すること。

【解決手段】 表面上に多段階層構造体を形成する方法が記載される。この方法は、表面上に硬化可能な液体層を堆積させるステップと、内部に多層パターンを有するスタンプを液体層に圧入し、該パターンによって定められる多段階層構造体を該液体層内に生成するステップと、液体層を硬化させ、内部に多段階層構造体を有する固体層を生成するステップとを含む。機械的位置合わせを用いて、構造体を形成することになる基板上に離間配置された複数の突出部及びスタンプのパターン内の相補的陥凹部を介して、基板に対するスタンプの光学的位置合わせを強化することができる。

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

金属−絶縁物−金属キャパシタおよび配線構造

【課題】 金属−絶縁物−金属キャパシタおよび配線構造を提供する。

【解決手段】 ダマシン工程を利用してMIMキャパシタおよび配線構造を含む半導体装置を製造する。前記MIMキャパシタおよび配線構造は静電容量を増やしつつ同じ深さで形成する。

(もっと読む)

半導体基板上の、超臨界流体による物質の蒸着

集積回路デバイス製造のための半導体基板のような基板上への、超臨界流体を利用した物質の蒸着。蒸着は、基板表面に蒸着される物質の前駆体を含む、超臨界流体をベースとする組成物を使用して行われる。そのようなアプローチにより、気相蒸着工程に必要な揮発性および搬送性がないために、蒸着への適用には全く不適切であった前駆体の使用が可能になる。 (もっと読む)

溝配線を有する半導体装置および半導体装置の製造方法

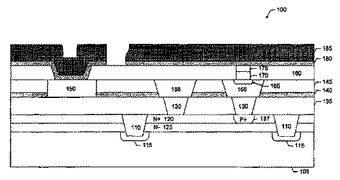

【課題】 多層配線において、ショートやビア抵抗増加のような目合わせずれによる問題を回避し、信頼性の高い多層配線を得る。

【解決手段】 半導体装置は、第1配線層(201)と、層間絶縁層(202〜208)とを具備する。第1配線層(201)は、基板の上面側に設けられ、第1配線を含む。層間絶縁層(202〜208)は、前記第1配線層(201)上に設けられ、一方の端を前記第1配線に接続されたビアと、前記ビアの他方の端に接続された第2配線とを含む。前記層間絶縁層(202〜208)はシリコン酸化膜より低い比誘電率を有する。前記層間絶縁層(202〜208)の上部は、下側から順に、シリコン酸化膜(206)、シリコン窒化膜(207)、シリコン酸化膜(208)を備える。

(もっと読む)

ビア開口部中に形成されるポリマーメモリデバイス

本発明は、ビア内にポリマーメモリデバイスを製造する方法に関する。この方法は、少なくとも1つの金属を含む層をその上に備える半導体基板を提供するステップと、この金属を含む層中に少なくとも1つの銅コンタクトを形成するステップと、銅コンタクト上に少なくとも1つの絶縁層を形成するステップと、絶縁層に少なくとも1つのビアを形成し、銅コンタクトの少なくとも一部を露出するステップと、ビアの下側部分にポリマー材料を形成するステップと、ビアの上側部分にトップ電極材料層を形成するステップとを含む。  (もっと読む)

(もっと読む)

ライン及びビア導体のための異なる材料を有するデュアル・ダマシン相互接続構造体

【課題】 ライン導体のために用いられるものと異なる、ビア又はスタッドのための材料を用いて、デュアル・ダマシン相互接続構造体を形成する方法を提供すること。

【解決手段】 ライン導体に用いられるものとは異なる、ビア又はスタッドのための材料を用いるか、又はトレンチ・ライナに用いられるものとは異なる、ビア・ライナのための材料を用いるか、或いは該トレンチ・ライナのものと異なるビア・ライナ厚を有する、デュアル・ダマシンのバックエンド・オブ・ライン(back−end−of−line:BEOL)相互接続構造体を形成する方法が開示される。改善された機械的強度のために、ビアに厚い超硬合金を用いる一方で、トレンチに薄い超硬合金だけを用い、抵抗を低くすることが好ましい。

(もっと読む)

銅メタライゼーションのためのALD窒化タンタルの集積

窒化タンタル/タンタルバリア層を堆積させるための方法および装置が、集積処理ツールでの使用のために提供される。遠隔発生プラズマによる洗浄ステップの後、窒化タンタルは原子層堆積法で堆積され、タンタルはPVDで堆積される。窒化タンタル/タンタルは、堆積された窒化タンタルの下の導電性材料を露呈するために、誘電体層の部材の底部から除去される。場合によって、さらなるタンタル層が、除去ステップの後に物理気相堆積法で堆積されてもよい。場合によって、窒化タンタル堆積およびタンタル堆積は同一の処理チャンバで生じてもよい。シード層が最後に堆積される。 (もっと読む)

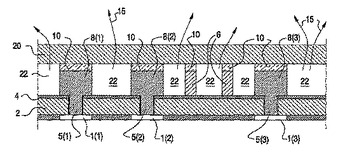

多孔質の誘電体層とエアギャップとを有する基板の製造方法、および基板

金属ライン(8(i))の間および誘電体内にエアギャップを形成する方法である。方法は、デュアルダマシン(dual damascene)構造を得ること、拡散バリア層(10)を、平坦化された面に直接加えること、およびリソグラフィステップを行なうことからなり、これにより、金属ラインを、拡散バリア層の下に遮蔽する。任意として、金属ライン(8(i))間の大きな誘電体領域(6)のいくつかの部分も、遮蔽される。露出した拡散バリア層部分および下にある誘電体がエッチングされる。典型的には150〜450℃の温度に加熱することにより、揮発性成分に分解することができる材料の層が加えられ、エッチングまたはCMPにより平坦化される。分解性生成物に対して透過性である誘電体層(20)が堆積され、その後、基板は加熱される。次いで、使い捨て層が分解し、透過性の誘電体層を通じて消滅し、その後に、金属ライン(8(i))および大きな誘電体領域の間に、エアギャップ(22)を残す。  (もっと読む)

(もっと読む)

半導体製造プロセスの過程で導電面を不動態化するための方法

半導体ウェハの製造プロセスが開示されている。メタル配線の表面に発生するデンドライトや電気分解反応を抑止するため、半導体ウェハに対して溶液が適用される。その溶液は、CMP処理の際又はCMP洗浄後処理の際に適用される。その溶液は、界面活性剤及び防食剤を含む。一実施形態では、その溶液中に含まれる界面活性剤の濃度が約1重量パーセント未満に設定され、防食剤の濃度が約1重量パーセント未満に設定される。また、その溶液は、溶媒及び共溶媒を含むこともできる。別の実施形態では、その溶液が、界面活性剤及び防食剤を含まず、溶媒及び共溶媒を含む。一実施形態では、CMP処理及びCMP洗浄後処理を、約1μm未満の波長を持つ光の存在下で実施できる。  (もっと読む)

(もっと読む)

多層配線構造の製造方法

【課題】バリアメタル膜の表面に形成される自然酸化膜の膜厚を薄くし、ボイドの発生を防止した多層配線構造の製造方法を提供する。

【解決手段】埋め込み型の多層配線構造の製造方法において、絶縁層に孔部4を形成する工程と、少なくとも孔部の内壁を覆うように、タンタルと窒素を主成分とするバリアメタル膜5を形成する工程と、バリアメタル膜の表面に形成された酸化膜6を除去する工程と、銅を含むめっき液にバリアメタル膜を浸漬してバリアメタル膜上に無電解銅めっき膜7を形成する工程とを含み、バリアメタル膜に含まれる窒素とタンタルの元素組成比(N/Ta)を、0.3以上で、かつ1.5以下とする。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つ高バリア性を有するバリアメタルを提供する。

【解決手段】バリアメタル201 が、配線溝16の底面及び側壁の表面に沿って形成された膜厚16nmのTaN0.87膜31と、TaN0.87膜上に形成され、配線溝16に埋め込み形成されたCuダマシン配線17に接する膜厚4nmのTaN1.19膜32とから構成されている。

(もっと読む)

2,001 - 2,020 / 2,035

[ Back to top ]