Fターム[5F033JJ11]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Cu (3,263)

Fターム[5F033JJ11]の下位に属するFターム

Cu合金 (406)

Fターム[5F033JJ11]に分類される特許

2,001 - 2,020 / 2,857

銅相互接続配線、ならびにそれを構成するための方法および機器

ガスクラスターイオンビーム処理プロセスの適用により、集積回路の相互接続構造に使用される、銅の相互接続配線層の表面上で、層をキャップ化する、改良された集積相互接続、集積回路の構造を形成する方法ならびに機器である。銅の拡散が抑制され、電気泳動寿命が向上し、選択金属キャップ化技術の使用、およびそれに付随した問題が解消される。銅のキャップ化処理、清浄化処理、エッチング処理、および膜形成処理用の、ガスクラスターイオンビーム処理モジュールを含む、各種クラスターツール構成について示した。  (もっと読む)

(もっと読む)

シード膜の成膜方法、プラズマ成膜装置及び記憶媒体

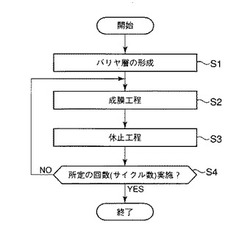

【課題】オーバハング部分を生ぜしめることなくシード膜を形成することができるシード膜の成膜方法を提供することにある。

【解決手段】真空引き可能になされた処理容器24内でプラズマにより金属ターゲット70をイオン化させて金属イオンを発生させ、金属イオンを処理容器内の載置台34上に載置した表面に凹部4を有する被処理体へバイアス電力により引き込んで凹部内を含む被処理体の表面に金属膜を形成することによりメッキ用のシード膜を形成するようにしたシード膜の成膜方法において、バイアス電力を、被処理体の表面に一旦形成された金属膜がスパッタされないような大きさに設定して金属膜を形成する成膜工程と、金属イオンを発生させないで金属膜の形成を休止する休止工程とを、交互に複数回繰り返す。

(もっと読む)

半導体装置とその製造方法、およびそのパターン生成方法

【課題】層間絶縁膜、特にLow−k膜を用いた場合の絶縁膜中の残留ガスによるバリアメタル等の劣化を抑制し、信頼性の高い半導体装置、その製造方法、およびパターン生成方法を提供する。

【解決手段】本発明の実施の形態に係る半導体装置10は、半導体基板上に形成された層間絶縁膜20と、この層間絶縁膜20上に形成された層間絶縁膜20よりも高い密度を有する保護膜21と、これら層間絶縁膜20および保護膜21内に形成された配線14およびダミー配線15の少なくとも一方と、を含む配線層11a〜11cと、前記層間絶縁膜20内で、前記配線14および前記ダミー配線15の被覆密度の合計が所定の規定値よりも低い低密度領域17を取り囲んで他の領域と分離する分離壁(金属壁16)と、を有する。

(もっと読む)

半導体装置

【課題】 NBTI劣化を抑制することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】 半導体装置は、n型領域を有するシリコン基板と、n型領域上に、窒素を含む酸化シリコンを用いて形成されたゲート絶縁膜と、ホウ素を含むシリコンを用いて、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極両側の前記シリコン基板内に形成されたp型ソース/ドレイン領域と、酸化シリコン層と窒化シリコン層との積層を用いて、ゲート電極の側壁上に形成されたサイドウォールスペーサと、ゲート電極、サイドウォールスペーサを覆い、平坦化された表面を有する層間絶縁膜と、層間絶縁膜の平坦化された表面から内部に向って形成された配線用凹部と、凹部を埋める、TaまたはTiで形成された下地バリア層とその上の銅領域を含む銅配線と、を有することを特徴とする。

(もっと読む)

ウェーハレベルパッケージ及びその製造方法

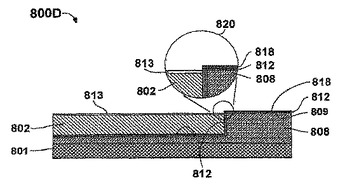

【課題】半田接続部等の接続信頼性を改善することができるウェーハレベルパッケージの製造方法を提供する。

【解決手段】第2導電性パターン層72上に、上面から見てほぼ楕円形状で断面形状がドーム形状の第1ポリマー層26を形成し、この第1ポリマー層26を第2ポリマー層28で覆うことにより、多層構造体27を形成する。この多層構造体27は、信頼性検査や実際検査の際、ウェーハレベルパッケージの接合部又は接続線に加えられる熱機械的損傷と外部衝撃から半導体チップ22を保護する。

(もっと読む)

半導体装置及びその製造方法

【課題】 キャパシタを形成するために必要となる追加工程数がより少ない半導体装置を提供する。

【解決手段】 層間絶縁膜に、第1の用凹部及び配線溝が形成されている。第1の用凹部内に下部電極が充填され、配線溝内に第1の配線が充填されている。層間絶縁膜の上にエッチングストッパ膜とビア層絶縁膜とが配置されている。第1のビアホールが、ビア層絶縁膜及びエッチングストッパ膜を貫通し、第1の配線の上面まで達し、その内部に第1のプラグが充填されている。平面視において下部電極と少なくとも部分的に重なる第2の用凹部が、ビア層絶縁膜に形成されている。上部電極が、第2の用凹部の底面と側面とを覆う。上部電極、エッチングストッパ膜、及び下部電極が、キャパシタを構成する。ビア層絶縁膜の上に、第1のプラグに接続された第2の配線が形成されている。

(もっと読む)

制御された二軸応力を有する超低誘電率膜および該作製方法

【課題】制御された二軸応力を有する超低誘電率層と、該低誘電率層を形成するための方法を提供する。

【解決手段】PECVDとスピン・コーティングとの一方によってSi、C、OおよびHを含む層を形成する工程と、それぞれ10ppm未満の非常に低い濃度の酸素および水を含む環境中で膜を硬化する工程とを組み込んだ、制御された二軸応力を有する超低誘電率層を形成するための方法を含む。この方法を用いて形成された2.8以下の誘電率を有する材料も含む。本発明は、46MPa未満の低い二軸応力を有する膜を形成するための問題を克服する。

(もっと読む)

半導体チップおよびその製造方法、ならびに半導体装置

【課題】配線基板や他の半導体チップに対する接続信頼性が高い半導体チップおよびその製造方法を提供する。

【解決手段】この半導体チップ31は、機能素子3が形成された半導体基板2と、半導体基板2の一方表面に開口を有する貫通孔4の内部を埋めるように配置されたポリマー32と、ポリマー32上に形成され、機能素子3に電気接続された配線層35と、配線層34のうちポリマー32上にある部分に設けられた突起電極14とを含む。

(もっと読む)

銅でないメッキ可能層の上への銅の直接電気メッキのための方法

【課題】銅でないメッキ可能層の上への銅の直接電気メッキのためのプロセスを提供する。

【解決手段】半導体構造物中に相互配線を形成するためのプロセスであって、基板の上に誘電体層を形成する工程と、誘電体層の上に第一の障壁層を形成する工程と、第一の障壁層の上に第二の障壁層を形成する工程であって、第二の障壁層は、ルテニウム、白金、パラジウム、ロジウムおよびイリジウムからなる群から選ばれ、第二の障壁層の形成は、第二の障壁層中の酸素のバルク濃度が20原子パーセントまたはそれ未満となるように操作される工程と、第二の障壁層の上に導電層を形成する工程と、を含むプロセス。本プロセスは、さらに、第二の障壁を処理して第二の障壁層の表面の酸化物の量を減少させる工程を含むことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】封止される被対象物に段差部を備えているが、封止部を設けた際に該段差部に起因したボイドの発生が抑制され、ひいては優れた耐食性を備える半導体装置と、その製造方法を提供する。

【解決手段】本発明に係る半導体装置1は、導電性を有する剛体からなる基板2と、該基板の少なくとも一方の面に絶縁部3を介して配された導電部5と、該絶縁部及び該導電部を覆うように配された感光性樹脂からなるフィルム6と、を備えている。前記基板2は、一方の面に開口する凹部及び/又は貫通孔2aを備え、該凹部及び/又は該貫通孔はその内部が略全域にわたって、前記フィルム6により充填されている形態をなす。

(もっと読む)

半導体素子のボンディングパッド構造

【課題】十分な量の電流をチップ内へ供給でき、かつ導電膜間の絶縁膜内に亀裂が発生しない半導体素子のボンディングパッド構造を提供する。

【解決手段】所定距離離隔された第1導電膜及び第2導電膜と、この第1導電膜及び第2導電膜の間に存在して所定距離離隔された第1導電膜及び第2導電膜を電気的に連結する連続的な第3導電膜及びこの連続的な第3導電膜内に存在して連続的な第3導電膜を貫通するように延びてその側壁が各々連続的な第3導電膜で取り囲まれた複数個の島型絶縁体とを含む。

(もっと読む)

半導体集積回路

【課題】セルアレイの大容量化と信頼性向上に有効なレイアウトを提案する。

【解決手段】本発明の例に関わる半導体集積回路は、セルアレイ11と、セルアレイ11上に配置されるライン&スペースのパターンを有する導電線WL11,・・・WL1nと、導電線WL11,・・・WL1nよりも上に形成される引き出し線L11,・・・L1nと、導電線WL11,・・・WL1nと引き出し線L11,・・・L1nとを接続するコンタクトホールCS11,・・・CS1nとを備え、導電線WL11,・・・WL1nの一端は、導電線WL11,・・・WL1nのうちの一つから他の一つに向かうに従って、順次、セルアレイ11の端部から離れていく。

(もっと読む)

半導体装置

【課題】動作信頼性を向上させた半導体装置を提供する。

【解決手段】RFパワーモジュールを構成する半導体チップ1のゲート電極用のバンプ電極8gと、ドレイン電極用のバンプ電極8dとの間に、発振シールドとしてソース電極用のバンプ電極8sを設けた。ソース電極用のバンプ電極8sは、他のバンプ電極8g,8dよりも長い帯状のパターンとなっている。また、バンプ電極8g,8d,8sは、ボンディングパッド上に下地金属を介して金属層を設け、さらにその上に半田層を設けた縦構成を有している。

(もっと読む)

半導体装置

【課題】出力画像に半導体基板の裏面に形成された配線のパターンが映り込むという問題を解消した半導体装置を提供する。

【解決手段】受光素子1と配線層10との間に光透過性基板6から半導体基板2を介して配線層10の方向に入射する赤外線を配線層10に到達させずに受光素子1側に反射する反射層8を形成する。反射層8は少なくとも受光素子1の領域の下方に一様に形成するか、あるいは受光素子1の領域の下方にのみ形成してもよい。また、反射層8ではなく、入射される赤外線を吸収し透過を防止する機能を有する反射防止層30を形成してもよい。

(もっと読む)

太いワイヤ構造およびそれを形成するためのデュアル・ダマシン方法(太いワイヤ構造を形成するためのデュアル・ダマシン・プロセス)

【課題】 極太ワイヤを有する半導体デバイスと、デュアル・ダマシン・プロセスを使用してそれを製造する方法を提供することにある。

【解決手段】 この方法では、スタック構造内で少なくとも1つの部分ビア(26)がエッチングされ、少なくとも1つの部分ビア(26)の周りにボーダ(32)が形成される。この方法は、少なくとも1つのエッチング・ストップ層(22)までビア・エッチングを続行しながら、選択エッチングを使用して太い配線を形成するステップをさらに含む。

(もっと読む)

半導体装置の製造方法

【課題】工程数の増加を抑えながら、ビア間の耐圧の低下を抑制することができる半導体装置の製造方法を提供する。

【解決手段】配線2上に低誘電率膜5及び6を形成した後、低誘電率膜5及び6上にハードマスク7、8及び9を形成する。ハードマスク7〜9上にレジストマスクを形成する。レジストマスクを用いて低誘電率膜5及び6にビアホール11を形成する。レジストマスクをアッシングする。このとき、レジストマスクから生じる飛散物をビアホール11の少なくとも側面に付着させて保護膜12を形成する。その後、ビアホール11を配線2まで到達させ、ビアホール11内に導電材を埋め込む。

(もっと読む)

Cu配線膜構造、Cu配線膜構造物の製造方法、及びCu拡散防止材

【課題】 Cuの拡散を効果的に防止でき、特に、厚さが薄くてもCuの拡散を効果的に防止でき、更には薄くて高精度なCu拡散防止膜を簡単に形成でき、高性能で信頼性に富む半導体素子を提供することである。

【解決手段】 基板と、

前記基板上に構成されたCu又はCu合金からなるCu配線膜と、

前記Cu配線膜上に構成されたAl−Cu合金膜

とを具備するCu配線膜構造。

(もっと読む)

半導体装置の製造方法

【課題】エアギャップの大きさを確保して配線間容量の低下を促進すると共に、エアギャップの形成による半導体装置の形成精度の低下を防止することを目的とする。

【解決手段】エアギャップ溝111を形成するための絶縁膜のエッチングとして等方性の高いエッチングを実施することにより、配線側壁の近傍の絶縁膜が十分に除去できるようになるため、エアギャップの大きさを十分確保することができ、配線間の容量を十分に低減することができる。

(もっと読む)

半導体装置

【課題】 NBTI劣化を抑制することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】 半導体装置の製造方法は、n型領域を有するシリコン基板の上に、窒素を含む酸化シリコンを用いたゲート絶縁膜と、ホウ素を含むシリコンを用いたゲート電極とを形成する工程と、ゲート電極両側の前記シリコン基板内にp型ソース/ドレイン領域を形成する工程と、ゲート電極の側壁上に酸化シリコンを用いてサイドウォールスペーサを形成する工程と、ゲート電極、サイドウォールスペーサを覆い、平坦化された表面を有する層間絶縁膜を形成する工程と、層間絶縁膜の平坦化された表面から内部に向って凹部を形成し,該凹部内に下地のバリア層とその上の銅領域を含む銅配線とを埋め込む工程と、銅配線の上に炭化シリコン層を形成する工程と、 前記炭化シリコン層の上方に絶縁層をCVDで形成する工程と、を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 フォトリソグラフィ工程を新たに追加することなく形成でき、引出し配線の構成の自由度が高いキャパシタ構造を有する半導体装置を提供する。

【解決手段】 半導体基板上の層間絶縁膜の厚さ方向の途中まで達するように、配線溝(53B)が形成され、配線溝の底面から層間絶縁膜の底面まで達するように、ビアホール(51B)が形成されている。層間絶縁膜の底面まで達するように、キャパシタ用凹部(55)が形成されている。配線溝及びビアホール内に導電部材(62B)が充填されている。キャパシタ用凹部内に、下部電極(62A)、キャパシタ誘電体膜(65A)、及び上部電極(68A)を含むキャパシタ(69)が充填されている。キャパシタの下部電極は、導電部材と同一の材料で形成され、キャパシタ用凹部の底面及び側面に沿って配置されている。下部電極の上面に窪みが形成されており、キャパシタ誘電体膜は、この窪みの内面を覆う。上部電極は、この窪みの内部に充填されている。

(もっと読む)

2,001 - 2,020 / 2,857

[ Back to top ]