Fターム[5F033JJ13]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Au、Au合金 (649)

Fターム[5F033JJ13]に分類される特許

201 - 220 / 649

半導体装置

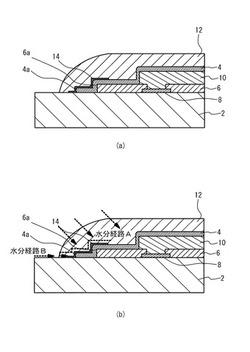

【課題】水分の浸入による半導体装置の信頼性低下を抑制した装置の提供。

【解決手段】GaAs系半導体、InP系半導体、及びGaN系半導体のいずれかからなる半導体層2と、半導体層2上に設けられ、端部4aが半導体層2上に位置する第1窒化シリコン膜4と、第1窒化シリコン膜4の端部4aを覆うように、半導体層2上及び第1窒化シリコン膜4上に設けられたポリイミドまたはベンゾシクロブテンのいずれかからなる保護膜12と、半導体層2の上面及び第1窒化シリコン膜4の端部4aに接するように、半導体層2と保護膜12との間から第1窒化シリコン膜4の端部4aと保護膜12との間にかけて連続的に設けられた第1Ti層14と、を具備することを特徴とする半導体装置。

(もっと読む)

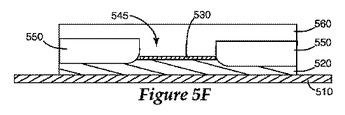

陽極酸化された薄膜構造用の電気的接続

第1の薄膜メタライゼーション層と第2の薄膜メタライゼーション層とを電気的に接続する回路ビアの形成のための手法が述べられる。ビアの形成では、第1のメタライゼーション層の陽極酸化に先立って、ビア接続領域に配置される陽極酸化バリア及び/又は補助パッドを使用する。バリアを形成するために使用される材料は、陽極酸化の際に陽極酸化液を実質的に透過せず、導電層とバリアとの間に酸化物が形成されることを阻止するものである。補助パッドは非陽極酸化性であり、陽極酸化の際に、パッドを通じて電流が流れることを実質的に防止するためにバリアによって覆われる。陽極酸化の後に、バリアは除去される。補助パッドが充分な導電性を有する場合には、バリアの除去後に第1のメタライゼーション層上に残存されてもよい。第2のメタライゼーション層が陽極酸化層上に配置され、ビア接続領域において第1の導電層と電気的に接触する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】複数の半導体チップを多数積層した半導体装置において、生産性を損なうことなく高性能化する。

【解決手段】シリコン基板1の主面s1上に順に形成された複数の素子、層間絶縁膜2およびパッド3と、パッド3に電気的に接続するバンプ電極4と、シリコン基板1の裏面s2に形成され、バンプ電極4に電気的に接続する裏面電極6とを有する半導体装置である。バンプ電極4は、パッド3を貫通し、シリコン基板1側に向かって突出するような突出部d1を有する。また、裏面電極6は、シリコン基板1の裏面s2側から主面s1側に向かって、バンプ電極4の突出部d1に達し、パッド3には達しないような裏面電極用孔部7の内側を覆うようにして形成されていることで、バンプ電極4と電気的に接続されている。

(もっと読む)

半導体装置の作製方法

【課題】複数の半導体集積回路を接続する配線の位置を容易に決定することを課題にする。

【解決手段】第1の基板上に第1の分離層と第1の半導体素子層を形成し、第1の半導体素子層に第1のレーザビームを照射することにより第1の開口部を形成し、第1の開口部に第1の半導体素子層と接続する第1の配線を形成し、第1の半導体素子層上に第1の保護材を形成し、第1の保護材に第1の配線に接続する第1の電極を形成し、第1の分離層に沿って第1の基板と第1の半導体素子層を分離し、上述の作製工程により第2の基板上に、第2の分離層、第2の半導体素子層、第2の配線、第2の保護材、第2の電極を作製し、第2の電極と第1の配線を接続するように第2の保護材上に第1の半導体素子層を貼り合わせ、第2の分離層に沿って第2の基板と第2の半導体素子層を含む積層構造を分離する半導体装置の作製方法に関する。

(もっと読む)

配線構造及びその形成方法、並びに半導体装置

【課題】炭素元素からなる線状構造体を有する接続部の更なる低抵抗化を実現して、更なる接続部の微細化を可能とする。

【解決手段】ビア孔28a内を充填し、配線溝32aの内壁面を覆うように、例えば超臨界CVD法により、ビア孔28a内におけるCNT28d間の空隙及びCNT28dの中空内を導電材料34で埋め込み、ビアプラグ33と、ビアプラグ33上で配線溝32aの内壁面を覆う下地膜32bとを同時形成する。

(もっと読む)

貫通電極形成方法

【課題】電極パッドのダメージを低減し、高信頼性の貫通電極を提供することを目的とする。

【解決手段】工程(a)〜(c)では、基板(1)の他方の面から電極パッド(5)に達する孔(1ab)を形成し、工程(d)では、孔(1ab)の内側に一端が電極パッド(5)に接触し他端が基板(1)の他方の面に達する導電経路(2)を形成し、工程(e)では、基板(1)をエッチングして導電経路(2)の周囲に凹部(1c)を形成し、更に凹部(1c)の内側で導電経路(2)の周面に絶縁膜を形成する。

(もっと読む)

微細空間への金属充填方法

【課題】空隙やボイドなどを生じることなく、微細空間を硬化金属によって満たし得る方法を提供すること、微細隙間で冷却された硬化金属の凹面化を回避し得る方法を提供すること、及び、工程の簡素化、歩留りの向上などに寄与し得る方法を提供すること。

【解決手段】処理対象である対象物2に存在する微細空間21に溶融金属4を充填し硬化させるに当たって、微細空間21の開口する開口面からその内部に溶融金属4を充填した後、微細空間21内の充填溶融金属41を、大気圧を超える強制外力F1を印加した状態で冷却し硬化させる工程を含む。

(もっと読む)

貫通電極配線の製造方法

【課題】複雑な工程を用いることなく、コストの増加や破損の発生などを抑制した状態で、より均一な深さの孔部を形成することで貫通電極配線が形成できるようにする。

【解決手段】酸化シリコン層104をマスクとしたRIEにより、シリコン基板101を選択的にエッチングすることで、シリコン基板101の一方の面(埋め込み酸化層102との界面)に到達する貫通孔106を形成する。貫通孔106の形成のためのエッチング処理(REI)においては、シリコン基板101の深さ方向に、シリコン基板101と埋め込み酸化層102との界面までしかエッチングが進行しない。この結果、シリコン基板101の板厚が均一であれば、貫通孔106の深さも均一に形成されるようになる。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】半導体装置の材料コスト、製造コストを低減可能な半導体装置およびその製造方法を提供する。

【解決手段】本発明にかかる半導体装置の製造方法は、シリコンサーメット膜5を形成する工程と、シリコンサーメット膜5を保護する保護膜4を形成する工程と、保護膜4をプラズマエッチングすることでコンタクトホール6を形成する開口工程と、を備える。そして、開口工程におけるエッチングの終点を検出するためのエッチング検出層3が保護膜4と接するように形成されている。保護膜4とエッチング検出層3の少なくとも一方には、保護膜4に含まれる元素とエッチング検出層3に含まれる元素のうち両方に共通しない元素が含まれている。開口工程において、両方に共通しない元素のプラズマ発光に基づき保護膜4のエッチングの終点を検出する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 貫通電極を有する半導体装置及び製造方法において、半導体装置の信頼性及び歩留りの向上を図る。

【解決手段】 電極パッド12に対応した位置で半導体基板11を貫通する貫通孔2を形成する。次に、貫通孔2を含む半導体基板11の裏面上に絶縁膜1を形成する。次に、少なくとも貫通孔開口部の絶縁膜1の表面に金属もしくは無機絶縁膜から密着安定化層3を形成する。

密着安定化層3の上に、ボトムエッチングのマスクとなるレジスト層4を形成する。次に、ボトムエッチングを行い、電極パッド12を露出させる。次に、レジスト層4を剥離して、ボトムエッチング後であっても凹凸のない絶縁膜1を得る。その後、低温プロセスで、バリア層5、シード層6、導電層7を形成して、パターニングを行い、密着安定化層3を有する貫通電極8付半導体装置を作る。

(もっと読む)

半導体装置及びその製造方法

【課題】 高アスペクト比の貫通電極を有する半導体装置を低温プロセスによって製造する。

【解決手段】 半導体基板1の表面側に配置された第1の電極3と裏面側の第2の電極6は、接続孔4に充填された導電物7と、接続孔4内に延在する第2の電極6の延在部6aとによって電気的に接続される。接続孔4が高アスペクト比であっても、第2の電極6を接続孔4の底部まで形成する代わりに導電物7を用いることで、低温プロセスによる成膜が可能となる。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106は、面積重み付けした平均結晶粒径が13μm以上の金属材料を少なくとも含む。また、導通部106は、結晶粒径が29μm以上の金属材料を含む。

(もっと読む)

集積回路デバイスのヒューズ構造

【課題】 集積回路デバイスのヒューズ構造を提供する。

【解決手段】 本発明のヒューズ構造は、半導体基板の一部の上に配置された金属含有導電性材料のストリップを含み、ストリップは、第1方向に沿って延伸し、均一な線幅を有する。誘電体層は、導電層を覆う。誘電体層内は、第1ビアと第2ビアを有し、第1インターコネクトと第2インターコネクトをそれぞれ含む。第1インターコネクトは、ストリップ上の第1位置と物理的且つ電気的に接触しており、第2インターコネクトは、ストリップ上の第2位置と物理的且つ電気的に接触している。導電ストリップ上の第1と第2位置は、シリコンを含まない。誘電体層の上方は、第1インターコネクトに電気的に接続された第1配線構造と、第2インターコネクトに電気的に接続された第2配線構造である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半田バンプが採用された半導体装置において、隣接する半田バンプ同士の接触の抑制が図られた半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、第1主表面を有する半導体チップ120と、第1主表面に形成された複数の電極123と、電極123ごとに複数形成されたランド部127と、半導体チップ120の第1主表面と対向する第2主表面を有するパッケージ基板160と、第2主表面に形成された複数の電極162と、電極162に形成されたランド部170と、ランド部127およびランド部170とを接続する半田バンプ125とを備える。

(もっと読む)

微粒子膜形成装置・形成方法、ならびに半導体装置およびその製造方法

【課題】 導電性微粒子膜を用いた現実的なバンプ電極構造の形成方法を実現すること。

【解決手段】半導体基板上に設けられた第1の電極と、この第1の電極上に設けられ、導電性微粒子からなる導電性微粒子膜と、この導電性微粒子膜上に設けられた第2の電極としての半田で形成されたバンプ電極とから構成された電極構造を具備してなる。

(もっと読む)

半導体装置の製造方法

【課題】孔のないキャリア(支持基板)を用いても、キャリアの取り外し時の半導体チップの散乱を防止することができる半導体装置の製造方法を提供する。

【解決手段】半導体素子が形成された素子形成基板の表面に、接着剤11を用いてキャリア(支持基板)12を貼り付ける。その後、素子形成基板の裏面から、素子形成基板の途中まで延びる複数のスルーホール1bを互いに離間して形成する。次に、裏面の処理として、裏面の研磨及びAu層23の形成等を行う。次に、複数のスルーホール1bを接着剤11まで到達させる。そして、複数のスルーホール1bから接着剤11の溶解液を接着剤11まで浸透させて、接着剤11を溶解させる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、薄膜トランジスタアレイ及び画像表示装置

【課題】溶剤乾燥や熱硬化のための熱処理工程を用いずに形成した欠陥の少ない絶縁層を有する薄膜トランジスタ、薄膜トランジスタの製造方法、薄膜トランジスタアレイ及び画像表示装置を提供すること。

【解決手段】バンプ107と、バンプ107により貫通される層間絶縁層105とを含む薄膜トランジスタにおいて、バンプ107がフッ素化合物を含み、層間絶縁層105がフィルム状ホットメルト接着剤の加熱圧着により形成され、バンプがフッ素化合物を含み、フッ素含有量が、0.01wt%以上5wt%以下であることを特徴とする薄膜トランジスタ。

(もっと読む)

貫通電極基板の製造方法

【課題】導通部におけるボイドの発生を抑えた貫通電極基板の製造方法を提供する。

【解決手段】基板101に表裏を貫通する貫通孔102を形成し、次に基板101の表面および貫通孔102の内壁に絶縁膜103を形成した後、閉塞部材を貫通孔102の少なくとも一方を塞ぐように配置し、前記閉塞部材を配置した側の基板101上にシード層を形成し、前記閉塞部材を除去し、前記シード層に給電する電解めっき法により、貫通孔102内に導電材料を充填して導通部105を形成する。

(もっと読む)

半導体装置

【課題】絶縁体に蓄積した電荷が放電を起こすことにより、アンテナ又は薄膜トランジスタを有する回路を破壊してしまう問題(静電気破壊の問題)を解決することを目的とする。

【解決手段】第1の絶縁体と、前記第1の絶縁体上に設けられた薄膜トランジスタを有する回路と、前記回路上に設けられ、前記回路と電気的に接続されたアンテナと、前記アンテナ上に設けられた第2の絶縁体と、を有し、前記第1の絶縁体と前記回路との間に第1の導電膜が設けられ、前記第2の絶縁体と前記アンテナとの間に第2の導電膜が設けられる。

(もっと読む)

一体型ビア及びビア端子を有する半導体回路基板、並びに関連するシステム及び方法

一体型ビア及びビア端子を有する半導体回路基板と、関連のシステム及び方法とが開示されている。特定の実施例に従う代表的な方法は、半導体回路基板に非貫通ビア(140)を形成することと、ビアの側壁面に保護層(122)を塗布することと、保護層が塗布された回路基板材料の除去から保護している間に、ビアの端面から回路基板材料を選択的に除去することにより端子穴(111)を形成することと、を含む。この方法は、ビア内の導電性材料が単一である導電性端子を形成するためにビア及び端子穴の双方に導電性材料を配置することをさらに含むことができる。端子に隣接する回路基板材料は、その後、回路基板の外部の導電性構造体に接続することができる端子を露出させるために除去することができる。 (もっと読む)

201 - 220 / 649

[ Back to top ]