Fターム[5F033JJ31]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 化合物 (4,106)

Fターム[5F033JJ31]の下位に属するFターム

Fターム[5F033JJ31]に分類される特許

61 - 80 / 101

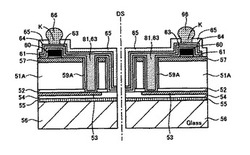

半導体装置

【課題】 本発明は半導体装置における信頼性向上を図るものである。

【解決手段】 本発明の半導体装置は、半導体チップの第1の主面上に形成されたパッド電極53と、前記半導体チップの第1の主面に接着されたガラス基板56と、前記半導体チップの第2の主面から前記パッド電極53の表面に貫通するビアホール81と、前記ビアホール81の側壁及び前記半導体チップの側端部に形成されたCVD膜から成る側壁絶縁膜59Aと、前記ビアホール81を通して、前記パッド電極53と電気的に接続された配線層63とを具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜の酸素含有量が低い部分とCu配線との密着性およびバリア性を十分に高めることができるバリア層を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置DVは、半導体基板SBと、Cu配線WRと、層間絶縁膜ILと、バリア層BRとを有する。Cu配線WRは銅を含有し半導体基板SB上に設けられている。層間絶縁膜ILはCu配線WRを埋め込むように半導体基板SB上に設けられている。バリア層BRは層間絶縁膜ILとCu配線WRとの間に設けられている。層間絶縁膜ILは、バリア層BRに面し、かつ炭素および窒素の少なくともいずれかを含有するライナー膜LNを含む。バリア層BRのライナー膜LNと面する部分BLは、炭素および窒素の少なくともいずれかを含む化合物からなる。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】メタルキャップ層の信頼性と生産性を向上させた半導体装置の製造方法及び半導体装置の製造装置を提供する。

【解決手段】成膜チャンバ40Dの内部空間Sに吸着期間の間だけZr(BH4)4を導入した。そして、シリコン基板2の表面、すなわち第2層間絶縁膜の表面及び第1配線の表面に、あるいはハードマスクの表面及び第2配線の表面にZr(BH4)4を吸着させ、吸着分子からなる単分子層を形成した。また、吸着期間の経過後、照射管47の内部に改質期間の間だけマイクロ波を照射し、プラズマ化したH2を、すなわち水素活性種をシリコン基板2の表面に供給した。そして、Zr(BH4)4の供給と、水素活性種の供給と、を交互に繰り返した。

(もっと読む)

エアギャップ構造の作製方法及びシステム

基板上にエアギャップ構造を作製する方法及びシステムが記載されている。当該方法は、基板上に犠牲層を形成する工程を有する。前記犠牲層は、約350℃より高温の熱分解温度で熱分解する分解可能材料を有する。その後、前記犠牲層の熱分解温度よりも低い基板温度で前記犠牲層上にキャップ層が形成される。前記犠牲層は、紫外(UV)放射線への前記基板の第1曝露を実行し、かつ前記基板を前記犠牲層の熱分解温度よりも低い第1温度にまで加熱することによって分解される。前記の分解した犠牲層は前記キャップ層を介して除去される。UV放射線への前記基板の第2曝露を実行し、かつ前記基板を前記第1温度よりも高い第2温度にまで加熱することによって、前記キャップ層は架橋して硬化する。  (もっと読む)

(もっと読む)

半導体装置

【課題】配線間抵抗およびSIV発生率を低減することができる、半導体装置を提供する。

【解決手段】下層配線5上には、第2層間絶縁膜8が積層されている。第2層間絶縁膜8には、その上面から掘り下げて形成された第2溝9に、Cuからなる上層配線10が埋設されている。また、第2層間絶縁膜8には、上層配線10の底面に接続され、Cuを含む金属材料からなるビア12が貫通形成されている。上層配線10およびビア12の底面および側面は、Cuの拡散に対するバリア性を有する材料からなるバリア膜13で連続して被覆されている。また、ビア12は、その側面がバリア膜6,13を介して下層配線5に接続されている。

(もっと読む)

貫通配線基板の製造方法

【課題】貫通配線基板を他基板に実装する際には圧力と熱が掛かる場合でも、貫通配線基板及び被実装物の耐久性を向上せしめた貫通配線基板の製造方法を提供する。

【解決手段】基板に設けられた貫通孔に貫通配線を備える貫通配線基板の製造方法において、基板部材7の両面に絶縁層9を形成する工程と、基板部材7下面の絶縁層9の窓開けを行い、前記基板をエッチングし基板部材7に貫通孔3を形成する工程と、貫通孔3の内周面に絶縁層9を形成する工程と、貫通孔3における基板部材7の上面側の絶縁層9の窓開けを行う工程と、貫通孔3を充填すると共に、貫通孔3から所定距離離れた位置まで貫通配線基板の一方の面上に伸延した貫通伸延配線13を形成する工程と、貫通孔3の位置を除く貫通伸延配線13上に導電性を有するバンプ15を形成する工程とを備える。

(もっと読む)

タングステン材料の原子層堆積法

【課題】ALDプロセスを使用して、均一性が良好で、ほとんどまたは全く汚染がなく、かつ導電率が高いつまり抵抗率が低いタングステン含有材料を堆積するための改良されたプロセスを提供する。

【解決手段】一実施形態では、プロセスチャンバ内に基板を位置決めするステップであって、該基板がこの上に配置されている下地層を含有するステップと、該基板をタングステン前駆体および還元ガスに順次曝してALDプロセス時に該下地層上にタングステン核形成層を堆積するステップであって、該還元ガスが約40:1、100:1、500:1、800:1、1,000:1以上の水素/ハイドライド流量比を含有するステップと、該タングステン核形成層上にタングステンバルク層を堆積するステップとを含む、基板上にタングステン含有材料を形成するための方法が提供される。該還元ガスはジボラン、シランまたはジシランなどのハイドライド化合物を含有している。

(もっと読む)

ダメージフリー被覆刻設堆積法

【課題】 周辺表面を殆ど汚染又は乱さずに、スパッタリングされたキャリア/バリヤ層を堆積させて所望の形状に刻設する方法を提供する。

【解決手段】 堆積層のイオンの衝突により浸食・汚染されないように、刻設された層の適用された表面が保護される、イオン堆積スパッタリング法を用いて刻設された材料層を半導体の特徴表面に適用する方法であり、刻設された層の第1の部分を、その層の適用される表面が浸食又は汚染されない程度に基板バイアスを十分低くして適用するステップと、刻設された層の次の部分を、さらなる層材料を堆積させながら、第1の部分からの形状を刻設可能な程度に基板バイアスを十分高くして適用するステップとを含む。この方法は、半導体の特徴表面上にバリヤ層、ウェッティング層及び導電層等を刻設するのに特に適しており、導電層が銅である場合は特に有益である。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性の低下を抑制しながら、消費電力の上昇および製造プロセスの煩雑化を抑制することが可能な半導体装置を提供する。

【解決手段】この表面形状認識用センサ(半導体装置)50は、シリコン基板1の上面上に積層され、厚み方向に貫通する開口部3bを有する複数の層間絶縁膜3と、W(タングステン)から構成されるとともに、複数の層間絶縁膜3の各々の開口部3b内に形成された複数の導電性プラグ10と、層間絶縁膜3間に形成されたメタル配線層2とを備え、複数の導線性プラグ10は、メタル配線層2を介することなく、シリコン基板1の厚み方向に互いに直接接触することにより柱状構造体11に構成されている。

(もっと読む)

電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置

【課題】電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置を提供する。

【解決手段】層を異ならせて互いに交差する二層以上の導電層を備える電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置において、導電層のうち少なくとも何れか一層は、長手方向に沿って幅を異ならせる幅変動部を備え、幅変動部を備える導電層240と隣接する導電層のうち、少なくとも何れか一つには、これら導電層同士が交差しないその一つの導電層の非交差部に静電気を誘発させる電荷を集中させるためのダミー部241が備えられることを特徴とする。

(もっと読む)

半導体装置、およびその製造方法

【課題】配線間絶縁膜からビア間絶縁膜への水分の移動を抑制し、配線間の実効誘電率に与える影響の少ない絶縁膜を有する半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置1は、表面に半導体素子を有する半導体基板と、前記半導体基板上に形成された配線2bと、前記配線2bと同じ層に形成された配線間絶縁膜4bと、前記配線2bの下面に接続された第1のビア7aと、前記第1のビア7aと同じ層に形成された第1のビア間絶縁膜8aと、前記配線2bの上面に接続された第2のビア7bと、前記第2のビア7bと同じ層に形成された第2のビア間絶縁膜8bと、前記配線間絶縁膜4bと前記第1のビア間絶縁膜8aとの間、および前記配線間絶縁膜4bと前記第2のビア間絶縁膜8bとの間の少なくともいずれか一方に形成されたCuSiN膜9と、を有する。

(もっと読む)

層間絶縁膜および配線構造と、それらの製造方法

【課題】 リーク電流の発生や熱アニールによる膜の縮小が抑制された、低誘電率で安定な層間絶縁膜を提供することにある。

【解決手段】 層間絶縁膜は、Si原子を含有するハイドロカーボン層とN原子を含有するフルオロカーボン層とを積層してなり、かつ前記ハイドロカーボン層は、C原子数に対するH原子数の比(H/C)が0.8乃至1.2となる割合でH原子とC原子とを含有する。

(もっと読む)

バリア膜の形成方法及びバリア膜、並びに多層配線構造の作製方法及び多層配線構造

【課題】Ta膜以外のバリア膜の形成方法及びその方法によりえられたバリア膜を提供する。このバリア膜を含む多層配線構造及び多層配線構造の作製方法を提供する。

【解決手段】 ホール及び配線溝が形成されている絶縁膜を有する成膜対象物の表面上で、CVD法により、Zr(BH4)4ガスからなる原料ガスと、N2ガスからなる反応ガスを励起手段によって励起せしめて得られたガスとを反応させ、バリア膜としてのZrBN膜41を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】バリアメタルの低抵抗化により配線抵抗の低抵抗化を図ると共に、バリアメタルのCuに対する拡散バリア性を高める。

【解決手段】層間絶縁膜10内に下層配線14が形成される。層間絶縁膜10及び下層配線14上にライナー膜20と層間絶縁膜22とが順次形成される。ライナー膜20と層間絶縁膜22内にビア28と上層配線30とが形成される。下層及び上層配線14,30とビア28とは、バリアメタル16,32とCu18,36とを有している。バリアメタル16,32は、RuxSinOy膜とRuxOy膜とRuxSin膜の少なくとも1つの膜17A,34Aと、RuxNy膜17B,34Bと、Ru膜17C,34Cとが積層されてなる。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の大面積化や配線の微細化に伴って銅のシード層が薄くなると、電解めっきでめっき膜のばらつきが大きくなる。

【解決手段】デュアルダマシン法で埋め込み配線を形成するにあたって、下層配線2上に孔加工や溝加工の加工マスクとなるTiN膜8を用いて、配線埋め込み領域(9,10)を形成する工程と、配線埋め込み領域を除くフィールド部に導電膜11を成膜する工程と、配線埋め込み領域を覆うようにバリアメタル層/シード層12を成膜する工程と、配線埋め込み領域を電解めっき法により銅配線材料13で埋め込む工程とを含むものとする。

(もっと読む)

半導体装置とその製造方法

【課題】ALD−TaN膜上にPVD−Ta膜を形成することなく信頼性に優れた低抵抗なCu配線を形成した半導体装置を得ること。

【解決手段】半導体基板上にトランジスタを含む電子部品が形成された半導体基材上に、少なくとも1層の銅配線を含む多層配線構造が層間絶縁膜を介して形成される半導体装置において、銅配線が形成される下部層間絶縁膜11と、下部層間絶縁膜11に形成された配線用溝12の側面と底面に、原子層レベルで膜厚が制御されて形成されるバリアメタル膜13と、バリアメタル膜13上に形成されるCuAl合金からなるCuAl合金シード膜14と、バリアメタル膜13が形成された配線用溝12に埋め込まれたCuを含む材料からなる下層Cu配線15と、を備える。

(もっと読む)

Ru膜および金属配線構造の形成方法

【課題】高速論理回路素子に利用される配線構造において、連続したルテニウム(Ru)薄膜を容易に形成する方法を提供する。

【解決手段】 ルテニウム(Ru)薄膜を基板上に堆積する方法は、(i)基板表面を有機金属前駆体で処理する工程と、(ii)処理した基板表面にルテニウム前駆体を吸着させる工程と、(iii)吸着させたルテニウム前駆体を励起させた還元性ガスで処理する工程と、そして(iv)工程(ii)および(iii)を繰り返すことにより、ルテニウム薄膜を基板上に形成する工程とを含む。

(もっと読む)

超小型電子デバイスの製造におけるフィチャーを埋め込むための銅堆積

【課題】半導体集積回路デバイス基板上にフィチャーの底面そして実質的にその上に金属をもたない側壁の部分上に金属からなる輪郭をもつフュチャー内に最初の金属堆積を形成することにより銅めっきをし、銅でフィチャーを埋め込むため最初の金属堆積上に銅を無電解的に堆積するための方法。半導体集積回路デバイス基板上にフィチャー内に銅に濡れる金属からなる堆積を形成し、頂部部分表面上に銅ベースの堆積を形成し、そして銅でフィチャーを埋め込むため銅に濡れる金属からなる堆積上に銅を堆積することによって銅をめっきするための方法。 (もっと読む)

半導体装置、およびその製造方法

【課題】高い信頼性と低い電気抵抗を有する配線構造を備えた半導体装置、およびその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成されたシリサイド層と、

前記シリサイド層上に形成された層間絶縁膜と、前記層間絶縁膜内に形成され、前記シリサイド層に前記コンタクト膜を介して電気的に接続された金属層と、前記金属層と前記層間絶縁膜との間に形成された拡散バリア膜と、を備え、前記コンタクト膜は、前記金属層に含まれる金属元素と、前記拡散バリア膜に含まれる金属元素と、前記シリサイド層に含まれる金属元素またはSiと、を少なくとも1つずつ含むことを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線材とバリアメタル層の密着性を向上させる。

【解決手段】第1の基板温度で、表面に凹部が形成された層間絶縁膜中及びその表面の酸

化種を放出させ、その後、前記第1の基板温度より低い第2の基板温度で、前記層間絶縁

膜の少なくとも一部と接触するようにして、Ti及びNを含み、酸素(O)及び貴金属成分を除く全成分におけるTi含有量が50at%を超える層を形成する。次いで、前記層上にCu金属層を形成して半導体装置を製造する。

(もっと読む)

61 - 80 / 101

[ Back to top ]