Fターム[5F033JJ31]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 化合物 (4,106)

Fターム[5F033JJ31]の下位に属するFターム

Fターム[5F033JJ31]に分類される特許

41 - 60 / 101

半導体装置とその製造方法、電気光学装置とその製造方法、回路基板とその製造方法、及び電子機器

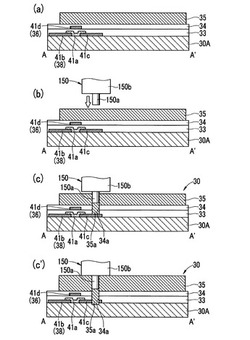

【課題】フォトリソグラフィー法及びエッチング法を用いることなく導電層間を接続することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板上に第1導電層と層間絶縁膜と第2導電層とを順に積層形成する導電層工程と、前記第2導電層の表面から物理的加工を施すことで、前記第2導電層と前記層間絶縁膜とを貫通して前記第1導電層に達する凹部を形成するコンタクトホール形成工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において歩留まりを向上させること。

【解決手段】シリコン基板30の上方に金属からなる第1の配線66を形成する工程と、第1の配線66の上に層間絶縁膜69を形成する工程と、第1の配線66の表面が露出する開口69aを層間絶縁膜69に形成する工程と、開口69aの内面及び層間絶縁膜69の表面に、上記金属の拡散を抑制するバリアメタル膜72を形成する工程と、バリアメタル膜72上に第1の導電膜73を形成する工程と、第1の導電膜73の表面を化学機械研磨法により研磨し、バリアメタル膜72の表面を露出させる工程と、開口69aの内の第1の導電膜73上及びバリアメタル膜72上に、第2の導電膜80を形成する工程と、第2の導電膜80を、開口69aよりも拡大した領域に残して選択的に除去し、第2の配線80aを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

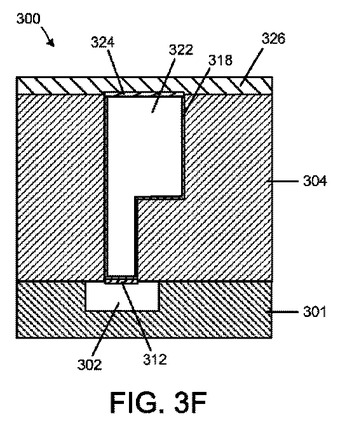

高アスペクト比プラグの充填方法

【課題】高アスペクト比を有するプラグを充填する方法を提供する。

【解決手段】高アスペクト比を有するプラグを充填する本発明の方法においては、核形成層を、バイアの側壁上ではなく、バイアの底に形成する。プラグ充填はバイアの底からトップへの方向であり、側壁から内側へではない。得られるプラグは、無ボイドであり、継ぎ目無しである。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、薄膜トランジスタアレイ及び画像表示装置

【課題】溶剤乾燥や熱硬化のための熱処理工程を用いずに形成した欠陥の少ない絶縁層を有する薄膜トランジスタ、薄膜トランジスタの製造方法、薄膜トランジスタアレイ及び画像表示装置を提供すること。

【解決手段】バンプ107と、バンプ107により貫通される層間絶縁層105とを含む薄膜トランジスタにおいて、バンプ107がフッ素化合物を含み、層間絶縁層105がフィルム状ホットメルト接着剤の加熱圧着により形成され、バンプがフッ素化合物を含み、フッ素含有量が、0.01wt%以上5wt%以下であることを特徴とする薄膜トランジスタ。

(もっと読む)

配線構造及び配線構造の製造方法

【課題】シリコンへのオーミック接合が得られると共に、シリコン中への元素の拡散を抑制できる配線構造及び配線構造の製造方法を提供する。

【解決手段】本発明に係る配線構造1aは、シリコン層10と、シリコン層10上に設けられ、ニッケル(Ni)が添加された銅合金からなる下地層20と、下地層20上に設けられる銅層30とを備え、シリコン層10と下地層20との界面を含む領域でNiが濃化することにより、電気導電性を有する拡散バリア層25が形成される。

(もっと読む)

配線構造及び配線構造の製造方法

【課題】シリコンへのオーミック接合が得られると共に、シリコン中への元素の拡散を抑制できる配線構造及び配線構造の製造方法を提供する。

【解決手段】本発明に係る配線構造1aは、シリコン層10と、シリコン層10上に設けられ、マンガン(Mn)が添加された銅合金からなる下地層20と、下地層20上に設けられる銅層30とを備え、シリコン層10と下地層20との界面を含む領域でMnが濃化することにより、電気導電性を有する拡散バリア層25が形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低誘電率膜を用いた層間絶縁膜SiOCH膜をCMPプロセスにおけるダメージから保護しつつ、配線間層間絶縁膜SiOCH膜の実効誘電率を低減する。

【解決手段】半導体装置100は、SiOCH膜10の表層が改質されることにより形成された、SiOCH膜10よりも炭素濃度が低くかつSiOCH膜10よりも酸素濃度が高い表面改質層20が設けられるとともに、Cu配線50の表面及び表面改質層20の表面に接するキャップ絶縁膜60を有している。このため、SiOCH膜10全体の誘電率の上昇を低減しつつ、CMPプロセスにおいて親水性の表面改質層20が露出することによって水滴が残りにくくなり、CMPプロセス後のパーティクルの残留やウォーターマークの発生を低減できる。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】合金膜18上に、SiおよびOを含む絶縁材料からなる犠牲層41が積層される。犠牲層41の積層後、熱処理が行われる。第2絶縁層6および犠牲層41にSiおよびOが含まれるので、熱処理が行われると、第2絶縁層6と合金膜18との界面および合金膜18と犠牲層41との界面において、Si、OおよびMnが結合し、それぞれMnSiOからなる第2バリア膜13および反応生成膜42が形成される。合金膜18に含まれるMnが反応生成膜42の形成に使用されることにより、第2バリア膜13の形成後、その第2バリア膜13の形成に寄与せずに合金膜18に残留するMnの量が減少する。そのため、合金膜18上に積層されるCu層20に拡散するMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

ルテニウム金属キャップ層を形成する方法

ルテニウム(Ru)金属の堆積を半導体デバイスの製造に統合することで、銅(Cu)金属のエレクトロマイグレーション及びストレスマイグレーションを改善する方法が供される。本発明の実施例は、NHx(x≦3)ラジカル及びHラジカルによって、金属層及びlow-k誘電材料を含むパターニングされた基板を処理することで、前記low-k誘電材料に対する前記金属層上でのRu金属キャップ層の選択形成を改善する方法を有する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】エアギャップ内への水分や絶縁材料の侵入を防ぎ、動作信頼性の劣化や電気容量の増加を抑えることのできる半導体装置の製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置の製造方法は、半導体素子を有する半導体基板上に、内部に配線が設けられた層間犠牲膜、および前記層間犠牲膜上に位置する絶縁膜を形成する工程と、前記絶縁膜および前記層間犠牲膜にエッチングを施し、前記層間犠牲膜に達する溝を形成する工程と、前記溝内にガス透過性膜を形成する工程と、前記層間犠牲膜をガス化させ、前記溝および前記ガス透過性膜を通して除去する工程と、前記層間犠牲膜を除去した後、前記ガス透過性膜上に、前記溝の開口部近傍を封止する封止膜を形成する工程と、を含む。

(もっと読む)

半導体装置の製造装置及び半導体装置の製造方法

【課題】多層配線構造における硼窒化ジルコニウム膜のパーティクルレベルを低減させて、また当該硼窒化ジルコニウム膜の耐酸化性や抵抗選択性を向上させることで半導体装置の信頼性を向上させた半導体装置の製造装置及び半導体装置の製造方法を提供することを目的とする。

【解決手段】窒素ガスにマイクロ波を照射することで生成した窒素ラジカルと成膜流量のZr(BH4)4とを成膜室31Sへ供給して成膜温度下にある基板Sの表面に硼窒化ジルコニウム膜を成膜するに際し、成膜装置は、成膜流量のZr(BH4)4が熱分解により形成する膜の成膜速度に関して成膜温度の増加に対するその成膜速度の増加率を基準増加率とすると、硼窒化ジルコニウム膜の成膜速度に関しては成膜温度の増加に対するその成膜速度の増加率を前記基準増加率にする。

(もっと読む)

銅めっきされた高アスペクト比のビア、及びその製造する方法

【課題】 最新のスケーリング技術の要件に適応することができ、適切に機能する実行可能なビアを一貫して生成できる、改善されたビア製造プロセスを提供すること。

【解決手段】 改善された高アスペクト比ビア及びそれを形成するための技術が提供される。1つの態様において、銅めっきされた高アスペクト比ビアを製造する方法が提供される。この方法は、以下のステップを含む。誘電体層内に高アスペクト比ビアをエッチングする。高アスペクト比ビア内及び誘電体層の1つ又は複数の表面の上に、拡散バリア領域を堆積させる。拡散バリア層の上に銅層を堆積させる。銅層の上にルテニウム層を堆積させる。高アスペクト比ビアを、ルテニウム層の上にめっきされた銅で充填する。この方法によって形成される銅めっきされた高アスペクト比ビアも提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート誘電膜を用いるpチャネルFETをゲート先作りプロセスにより形成すると閾値が大きくなる。

【解決手段】High-Kゲート誘電膜104の側面と接触するようにHigh-K誘電膜102を形成した後、酸素雰囲気中でアニールする。

(もっと読む)

コンタクト構造物の形成方法、及びこれを利用した半導体装置の製造方法

【課題】コンタクト構造物の形成方法及びこれを利用した半導体装置の製造方法を提供する。

【解決手段】コンタクト領域103を有する対象体100上に絶縁層106を形成した後、絶縁層106をエッチングしてコンタクト領域103を露出させる開口を形成する。露出されたコンタクト領域103上にシリコン及び酸素を含む物質膜を形成した後、シリコン及び酸素を含む物質膜上に金属膜を形成する。シリコン及び酸素を含有する物質膜と金属膜を反応させて、少なくともコンタクト領域103上に金属酸化物シリサイド膜121を形成した後、金属酸化物シリサイド膜121上の開口を埋める導電膜を形成する。コンタクト領域とコンタクトとの間に金属、シリコン、及び酸素が三成分系を成す金属酸化物シリサイド膜を均一に形成することができるため、改善された熱安定性及び電気的特性を有する。

(もっと読む)

マルチゲート型電界効果トランジスタおよびその製造方法

【課題】平坦化工程を行っても、金属汚染を防止することのできるマルチゲート型電界効果トランジスタおよびその製造方法を提供することを可能にする。

【解決手段】基板2上に並列するように設けられた第1導電型の複数の半導体層6と、複数の半導体層のそれぞれに、離間して設けられた第2導電型のソース/ドレイン領域60a、60bと、複数の半導体層のそれぞれに、ソース領域とドレイン領域との間に設けられるチャネル領域と、チャネル領域のそれぞれの上面に設けられた保護膜8と、チャネル領域のそれぞれの両側面に設けられたゲート絶縁膜9と、チャネル領域のそれぞれの両側面にゲート絶縁膜を挟むように設けられるとともにチャネル領域のそれぞれの上面に保護膜を挟むように設けられた金属元素を含む複数のゲート電極10と、複数のゲート電極のそれぞれの側面を覆うように基板上に設けられた層間絶縁膜20と、複数のゲート電極のそれぞれの上面を共通に接続する接続部23と、接続部に接続されたゲート配線24と、を備えている。

(もっと読む)

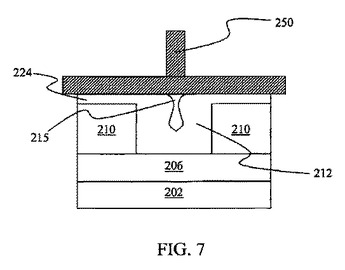

相変化メモリデバイスに電極を形成する方法

サブリソグラフィックな寸法又は高アスペクト比を含む、小寸法の開口内に電極材料を均一に形成する方法を提供する。この方法は、内部に形成された開口を有する絶縁層を提供するステップと、開口の上部及び内部に非等質的導電又は準抵抗性材料を形成するステップと、導電材料を移動化して開港内に圧縮するステップとを有する。この方法は、導電又は準抵抗性材料における空孔又は欠陥密度を堆積されたままの状態に対して低減する。移動化するステップは、押出又は熱的リフローによって達成され、空隙又は欠陥を合体、崩壊、染み透り又は他の方法によって堆積したままの導電又は準抵抗性材料から除去する。  (もっと読む)

(もっと読む)

半導体装置の製造方法、半導体装置、電子機器、半導体製造装置及び記憶媒体

【課題】基板上の凹部が形成された層間絶縁膜の露出面にバリア膜を成膜し、凹部内に下層側の金属配線と電気的に接続される銅配線を形成するにあたり、段差被覆性の良好なバリア膜を形成することができ、しかも配線抵抗の上昇を抑えた半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜に形成された凹部21の底面に露出した下層側の銅配線13の表面の酸化膜を還元あるいはエッチングして、当該銅配線13の表面の酸素を除去した後、マンガンを含み、酸素を含まない有機金属化合物を供給することによって、凹部21の側壁及び層間絶縁膜の表面などの酸素を含む部位に自己形成バリア膜である酸化マンガン25を選択的に生成させる一方、銅配線13の表面にはこの酸化マンガン25を生成させないようにして、その後この凹部に銅を埋め込む。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、ダマシン構造を有する銅多層配線を構成するトレンチのCMP工程後に露出した低誘電率膜表面のダメージを回避して配線信頼性を確保するとともに、直列抵抗の増大を抑制する。

【解決手段】 ポーラス絶縁膜に設けた凹部に埋め込まれた第1の金属膜の少なくとも頂面を、前記ポーラス絶縁膜の頂面と整合する高さまでZr及びBを含む第2の金属膜で覆う。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】微細パターンのCuの埋め込みが良好であり、Cuの層間絶縁膜中への拡散を抑制することを目的とする。

【解決手段】半導体装置では、下層配線102が半導体基板上の絶縁膜101内に形成され、上層配線112が絶縁膜101の上の層間絶縁膜104内に形成され、下層配線102と上層配線112とは層間絶縁膜104内に形成されたビアプラグ111を介して接続されている。ビアプラグ111および上層配線112では、それぞれ、第1および第2のバリアメタル膜107,108とCu膜110とが順に積層されており、第1のバリアメタル膜107は窒素を含有し、第2のバリアメタル膜108は白金族元素を含有している。

(もっと読む)

二つの導電層の間の電気的相互接続を作製するための方法

少なくとも一つの絶縁体層又は半導体層(4)によって分離された二つの導電層(2,5)の間の電気的相互接続の作製方法であって、少なくとも下方の導電層(2)及び上方の導電層(5)との間に伸びる分離層(4)の作製又は堆積よりも前にスタッド(3)を形成する段階を含み、前記スタッドの性質及び/又は形状は分離層(4)に関して使用される材料に対する非濡れ性を付与する。  (もっと読む)

(もっと読む)

41 - 60 / 101

[ Back to top ]