Fターム[5F033KK03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 半導体(基板を除く) (1,188)

Fターム[5F033KK03]の下位に属するFターム

Fターム[5F033KK03]に分類される特許

41 - 60 / 156

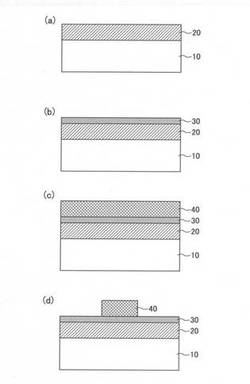

薄膜のパターニング方法、デバイス及びその製造方法

【課題】本発明は、表面エネルギーの低い薄膜に、ダメージなくパターニングを行う薄膜のパターニング方法、デバイス及びその製造方法を提供することを目的とする。

【解決手段】薄膜20上に、蒸着膜30を積層する工程と、

前記蒸着膜上に、フォトレジスト層40を積層する工程と、

フォトリソグラフィにより、前記フォトレジスト層をパターニングし、パターニングされた前記フォトレジスト層を用いて前記蒸着膜をエッチングしてパターニングする工程と、

パターニングされた前記蒸着膜をパターンマスクとして、前記薄膜をエッチングしてパターニングを行う工程と、を含むことを特徴とする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

リフトオフ方法及び薄膜トランジスタの製造方法

【課題】歩留まりの低下を防止して、製造工程の簡素化を図ることが可能になるとともに、製造コストの低減を図ることができる表示装置及びその製造方法を提供することを目的とする。

【解決手段】半導体ナノワイヤ3とリフトオフレジスト12と金属膜13とが形成された基板1を、気体のマイクロバブルが混合された液体により構成された剥離液に浸漬させることにより、リフトオフレジスト12とともにリフトオフレジスト12上の金属膜13を剥離して、基板2上に金属膜13からなる所定のパターンを形成する。

(もっと読む)

半導体装置

【課題】コンタクトホールの加工時において配線のダメージを受けにくく、信頼性の低下を抑制できる構造の接続部を有する半導体装置を提供すること。

【解決手段】接続部1は、第1導電層2と第2導電層4とが、その交差個所に設けられたコンタクトホール5を介して接続されたものである。矩形状のコンタクトホール5は第2導電層4の幅方向の略中央に配置されている。そして、コンタクトホール5のパターンを囲むように矩形状の半導体層3が設けられている。半導体層3は、コンタクトホール5の底部において第1導電層2上に形成されている。この半導体層3は、第1導電層2とのエッチング選択比が高く、第1導電層2に対するエッチング効率が充分に高いものである。

(もっと読む)

配線構造、及びそれを備えた液晶表示装置、並びに配線製造方法

【課題】配線を高精細化しても断線が生じ難い、信頼性の高い配線回路を実現する。

【解決手段】配線構造1は、ゲート電極17・17b・17cが配された基板9上に配される半導体層10と、ゲート電極17・17b・17c及び半導体層10が配された基板9上に配された第2層間絶縁膜13と、第2層間絶縁膜13上に配される配線18とを備え、第2層間絶縁膜13に形成されたコンタクトホール15内で、半導体層10と、配線18とが電気的に接続され、第2層間絶縁膜13は感光性樹脂材料からなり、さらに、コンタクトホール15内には導電性微粒子16が充填されており、導電性微粒子16によって、半導体層10と、配線18とが電気的に接続されている。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】全体としてのコンタクト抵抗を小さく維持しつつバリヤ性の高い薄膜の成膜方法及びプラズマ処理装置を提供する。

【解決手段】凹部6を有する絶縁層4が表面に形成された被処理体Wに対して薄膜を形成する成膜方法において、前記凹部内の表面を含む前記被処理体の表面にプラズマCVD法を用いて窒化チタン膜10の薄膜を形成する薄膜形成工程と、窒化ガスの存在下でプラズマを用いた窒化処理を行うことにより前記薄膜を窒化する窒化工程と、を有することを特徴とする成膜方法である。これにより、抵抗を小さく維持しつつバリヤ性の高い薄膜を形成する。

(もっと読む)

半導体装置

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

表示装置用Al合金膜および表示装置

【課題】バリアメタル層を省略して透明画素電極と直接接続させた場合にも、低いコンタクト抵抗と電気抵抗を示し、好ましくは耐熱性や耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、Al合金膜は、Ni及び/又はCoを0.1〜6原子%、Geを0.1〜2原子%含有すると共に、アルミマトリックス結晶粒界Ge濃度が、前記Al合金膜のGe濃度の1.8倍超を満足するAl合金膜である。

(もっと読む)

シリコン基板上に形成されるCMOSデバイスおよびIII−V族デバイスのための電気コンタクト

半導体構造体は、基板(12)と、基板を覆うシード層(13)と、シード層上に配置されるシリコン層(22)と、シリコン層中のトランジスタデバイス(27)と、シード層上に配置されるIII−V族デバイスと、複数の電気コンタクトと、を備え、それぞれの電気コンタクトは、TiNまたはTaNの層(32)と、TaNまたはTiNの層上の銅またはアルミニウムの層(34)と、を備え、電気コンタクトの1つは、トランジスタ(27)に電気的に接続され、電気コンタクトの別の1つは、III−V族デバイスに電気的に接続される。 (もっと読む)

有機トランジスタアレイ、表示パネル及び表示装置

【課題】オフ電流を低減することが可能な有機トランジスタアレイ、表示パネル及び表示装置を提供する。

【解決手段】マトリクス状に設けられている走査線11及び信号線12と、走査線11と接続するゲート電極21と、ゲート電極21及び走査線11を覆うように形成されている第1のゲート絶縁膜と、信号線12と接続するソース電極23と、チャネル領域Cを挟んでソース電極23と対向して形成されているドレイン電極24と、チャネル領域Cに形成されている有機半導体層25とを備え、走査線11及び信号線12が交差して形成されている画素領域A1、A2に設けられる有機トランジスタ20とを有する有機トランジスタアレイ10において、ゲート電極21は、更に平面視でドレイン電極24と信号線12とに挟まれる領域Sに形成され、有機半導体層25は、更に平面視でドレイン電極24と信号線12に挟まれる領域S1に形成されている。

(もっと読む)

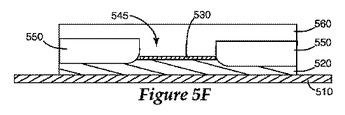

陽極酸化された薄膜構造用の電気的接続

第1の薄膜メタライゼーション層と第2の薄膜メタライゼーション層とを電気的に接続する回路ビアの形成のための手法が述べられる。ビアの形成では、第1のメタライゼーション層の陽極酸化に先立って、ビア接続領域に配置される陽極酸化バリア及び/又は補助パッドを使用する。バリアを形成するために使用される材料は、陽極酸化の際に陽極酸化液を実質的に透過せず、導電層とバリアとの間に酸化物が形成されることを阻止するものである。補助パッドは非陽極酸化性であり、陽極酸化の際に、パッドを通じて電流が流れることを実質的に防止するためにバリアによって覆われる。陽極酸化の後に、バリアは除去される。補助パッドが充分な導電性を有する場合には、バリアの除去後に第1のメタライゼーション層上に残存されてもよい。第2のメタライゼーション層が陽極酸化層上に配置され、ビア接続領域において第1の導電層と電気的に接触する。  (もっと読む)

(もっと読む)

有機トランジスタ、有機トランジスタアレイ及び表示装置

【課題】マイクロコンタクトプリント法を利用し、簡便に、安定して微細なパターンを有する有機薄膜トランジスタを提供する。

【解決手段】マスク7を介して、基板5にエネルギーを付与することにより、相対的に、臨界表面張力の大きな高表面自由エネルギー部5aと臨界表面張力の小さな低表面自由エネルギー部5bとを形成する。マイクロコンタクトプリント法を用いて臨界表面張力の大きな高表面自由エネルギー部5aにインク3を付着させる。高表面自由エネルギー部5aでは、スタンプ1からインク3が転写されやすく、低表面自由エネルギー部5bでは、表面自由エネルギーが小さいためにスタンプ1からインク3が転写されにくくなるため、有機TFT素子の製造において、電極パターンの微細化や、電極層の厚膜化が可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層に新たな機能を有する素子を設けた半導体装置を提供する。

【解決手段】半導体基板上に形成された第1配線層150、及び半導体素子200を備える。第1配線層150は、絶縁層156と、絶縁層156の表面に埋め込まれた第1配線154とを備える。半導体素子200は、半導体層220、ゲート絶縁膜160、及びゲート電極210を備える。半導体層220は、第1配線層150上に位置する。ゲート絶縁膜160は、半導体層220の上又は下に位置する。ゲート電極210は、ゲート絶縁膜160を介して半導体層220の反対側に位置する。

(もっと読む)

有機薄膜トランジスタ

【課題】ゲート絶縁層に対する密着性が良好で、且つ有機半導体層との間の寄生抵抗が低いソース電極とドレイン電極とを有する有機薄膜トランジスタを実現する。

【解決手段】本発明の有機薄膜トランジスタは、絶縁性基板上に、ゲート電極と、ゲート絶縁層と、ソース電極と、ドレイン電極と、有機半導体層とを備える有機薄膜トランジスタであり、上記ソース電極と絶縁性基板若しくはゲート絶縁層との間、及び上記ドレイン電極と絶縁性基板若しくはゲート絶縁層との間に、金を主成分とした合金からなる密着層をそれぞれ備え、上記ソース電極及びドレイン電極は金からなり、上記密着層は、金の含有量が、67原子%以上97原子%以下の範囲内である。

(もっと読む)

半導体装置及びその製造方法

【課題】配線層間の正常な電気的導通が取れている半導体装置を提供することを課題とする。

【解決手段】基板上又は基板の表面層に少なくとも2層の配線層を備え、前記2層の配線層の内、下層配線層がシリコンからなる際に、前記下層配線層と上層配線層間に炭化珪素層を備えたことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

表示装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一とする。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置において、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二種類の酸化物半導体層とを組み合わせて構成され、ゲート電極層と重なるチャネル形成領域となる半導体層上にチャネル保護層が設けられた逆スタガ型薄膜トランジスタが設けられた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続するパッド部が設けられている。

(もっと読む)

電極の製造方法、これを用いた薄膜トランジスタ素子及び有機エレクトロルミネッセンス素子

【課題】透明導電性微粒子を含む流動性材料の塗布により、ゲート電極を形成する方法において、従来よりも低抵抗、かつ充分な表面平滑性をもった透明導電膜の製造方法を提供する。

【解決手段】ガラス基板106上に、金属酸化物微粒子(ITO)及び金属酸化物の前駆体を含む薄膜104”を塗布する。この薄膜にマイクロ波を照射することにより、前駆体が発熱体として作用し、焼成され、導電性薄膜を形成する。これをパターンニングしゲート電極104とする。ついで、ゲート絶縁膜105を形成し、半導体前駆体を塗布、乾燥し、半導体前駆体材料薄膜101’を得る。これにマイクロ波を照射することにより、ゲート電極が発熱し、この熱により半導体前駆体材料薄膜が加熱され、酸化物半導体膜に変換され半導体層101が形成される。マスクを介して金を蒸着し、ソース、ドレイン電極102,103を形成し、薄膜トランジスタとする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置及びその製造方法について、ホウ素含有タングステン層を核形成層とする場合に、コンタクト抵抗値の増大を抑制する。

【解決手段】半導体装置100は、半導体基板101上に形成された第1絶縁膜103と、第1絶縁膜103に埋め込まれた導電膜109を含み且つ半導体基板101に達するコンタクト110と、半導体基板101及び第1絶縁膜103のそれぞれと、導電膜109との間に形成され、高融点金属を含む第1バリア層107とを備える。更に、第1バリア層107と導電膜109との間に形成され、第1バリア層107よりも水分透過性の低い第2バリア層118を備える。

(もっと読む)

半導体装置

【課題】耐熱性に優れ、不均一動作が抑制される高周波高出力半導体装置を提供する。

【解決手段】半導体基板上に形成される複数の電界効果トランジスタが並列接続される単位セルを、さらに複数並列接続する半導体装置において、この単位セルを構成する電界効果トランジスタの複数のゲート電極同士を接続するゲートバス配線に接続され、複数の導電層が積層した構造を有するゲートパッド電極と、隣接するゲートパッド電極間同士を接続し、ゲートパッド電極外周部の少なくとも一辺に沿って形成され、ゲートパッド電極を構成する複数の導電層の少なくとも一つの導電層で形成される抵抗体とを有することを特徴とする半導体装置。

(もっと読む)

41 - 60 / 156

[ Back to top ]