Fターム[5F033KK03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 半導体(基板を除く) (1,188)

Fターム[5F033KK03]の下位に属するFターム

Fターム[5F033KK03]に分類される特許

81 - 100 / 156

薄膜抵抗体及びその製造方法

【課題】薄膜抵抗層を損傷することなく形成して、抵抗値の制御性を向上するとともに、微細化にも有利な薄膜抵抗体の製造方法を提供する。

【課題の解決手段】半導体基板1上に設けた絶縁層2上に薄膜抵抗層3のパターンを形成する工程と、レジストのパターンを用いて薄膜抵抗層3の配線接続領域に金属層6を形成する工程と、レジストを除去した後に金属層6を含む薄膜抵抗層3全体を覆うように層間絶縁膜7を形成する工程と、層間絶縁膜7に金属層6に達する開口部(コンタクトホール)10を形成する工程と、少なくとも開口部(コンタクトホール)10を含む領域に金属層6と接続される配線層12を形成する工程とを、順次施す。

(もっと読む)

Al合金膜、電子デバイス及び電気光学表示装置用アクティブマトリックス基板

【課題】ITOやSiとの界面拡散を防止するとともに、低温プロセスが要求される各種電子デバイスに適用可能な低抵抗の電極膜用Al合金膜を提供すること。

【解決手段】本発明の一態様に係るAl合金膜は、Niからなる第1の添加元素と、元素周期表の周期2又は3に属する2a族のアルカリ土類金属、3b、4b族の半金属から選ばれる少なくとも1種類以上の第2の添加元素とを含む。また、第1の添加元素の組成比は0.5〜5at%であり、第2の添加元素の組成比は0.1〜3at%である。

(もっと読む)

半導体装置およびその製造方法

【課題】ダイシング工程で発生する膜剥離やクラックがチップ内部に伝播するのを防ぐ。

【解決手段】半導体装置100は、基板102と、ビア層130および配線層132が形成される素子形成領域であるチップ内部202と、平面視においてチップ内部202を囲むようにチップ内部202の外周に形成されたシールリング部204と、を含む。シールリング部204において、シールリングは、平面視においてチップ内部202を囲むように形成された貫通孔122aを有する第1のメタル層122と、第1のメタル層122上に第1のメタル層122に接して形成された第2のメタル層124と、を含み、第1のメタル層122の貫通孔122aの下部分には絶縁性材料(層間絶縁膜106)が形成され、貫通孔122aの上部分には第2のメタル層124を構成するメタル材料がくい込んで形成される。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】

CMOS装置の製造工程におけるコンタクト不良発生を抑制する。

【解決手段】

半導体装置の製造方法は、(a)Si基板に、n型の第1の活性領域、p型の第2の活性領域を形成する工程と、(b)活性領域に、第1、第2のゲート電極構造、第1、第2のソース・ドレイン領域をそれぞれ形成する工程と、(c)第1のソース/ドレイン領域に、凹部を形成する工程と、(d)凹部にSi−Geを含むp型の圧縮応力を有する半導体エピタキシャル層を形成する工程と、(e)半導体基板上に引張応力を有する窒化シリコンのエッチストッパ膜、層間絶縁膜を形成する工程と、(f)層間絶縁膜、エッチストッパ膜を貫通して、コンタクト孔をエッチングする工程と、(g)半導体基板上方に酸素を含むプラズマを発生する工程と、(h)コンタクト孔に導電性プラグを埋め込む工程と、を有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】例えば、液晶装置等の半導体装置について、製造プロセスを煩雑化させることなく、且つコンタクト抵抗の上昇を低減する。

【解決手段】凹部221a及び221bは、絶縁膜213上にレジスト膜222を形成した後、半導体製造プロセスで汎用される回折法或いはハーフトーン法を用いてレジスト膜222を部分的に除去することによって形成されている。したがって、レジスト膜221は、レジスト膜222を部分的に除去することによって形成された凹部221a及び221bの底部を構成するレジスト膜222の一部を含んで構成されている。凹部221bの深さd2は、凹部221aの深さd1より浅い。言い換えれば、凹部221bの底部の厚みは、凹部221aの底部の厚みより厚くなっている。

(もっと読む)

シード印刷及びめっきによるコンタクト金属及び相互接続金属の印刷

シリサイド形成金属を含むインクを用いて、コンタクト形成方法、そのコンタクト及び局所相互接続を含むダイオード及び/又はトランジスタ等の電気デバイスとその形成方法に関する。コンタクト形成方法は、露出したシリコン表面上にシリサイド形成金属インクを堆積させるステップと、インクを乾燥させ、シリサイド形成金属前駆体を形成するステップと、シリサイド形成金属前駆体及びシリコン表面を加熱して、金属スイサイドコンタクトを形成するステップとを含む。任意選択的に、露出したシリコン表面に隣接する誘電体層上に、金属前駆体インクを選択的に堆積させて、金属含有相互接続を形成できる。更に、1つ又は複数のバルク導電性金属を、残りの金属前駆体インク及び/又は誘電体層上に堆積させてもよい。かかる印刷したコンタクト及び/又は局所相互接続を用いて、ダイオード及びトランジスタ等を作製できる。 (もっと読む)

フローティングボディ素子及びバルクボディ素子を有する半導体素子及びその製造方法

【課題】フローティングボディ素子及びバルクボディ素子を有する半導体素子及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は、バルクボディ素子領域及びフローティングボディ素子領域を有する基板を準備する工程を含む。バルクボディ素子領域の基板の活性領域を画定するとともに、フローティングボディ素子領域のうち第1素子領域の基板上に順に積層された第1犠牲パターン及び第1活性パターンを画定する素子分離膜を形成する。フォトリソグラフィ及びエッチング工程を用いて素子分離膜に第1犠牲パターンの一部分を露出させる第1リセス領域を形成する。第1犠牲パターンを除去して第1活性パターン下部に第1空間を形成する。第1空間の内壁及び第1リセス領域の内壁に第1埋込誘電膜を形成する。第1埋込誘電膜を有する基板上に少なくとも第1空間を埋め込む第1埋込パターンを形成する。

(もっと読む)

半導体装置

【課題】基板上にCMISFETを備えた半導体装置において、Global Strainによる応力印加を有効に活用しつつ、回路のスイッチ動作速度の低下を生じさせない半導体装置を提供する。

【解決手段】基板の一方の面に形成される第1の素子領域と、基板の他方の面に形成される第2の素子領域と、第1の素子領域と第2の素子領域との間の、比誘電率が3.9よりも低い絶縁層とを備え、第1の素子領域にn型MISFETが形成され、第2の素子領域にp型MISFETが形成され、絶縁層中を貫通する配線によって、第1の素子領域と第2の素子領域とが電気的に接続され、第1の素子領域が形成される面が凸形状、第2の素子領域が形成される面が凹形状となるように基板が湾曲していることを特徴とする半導体装置。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コンタクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置

【課題】電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置を提供する。

【解決手段】層を異ならせて互いに交差する二層以上の導電層を備える電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置において、導電層のうち少なくとも何れか一層は、長手方向に沿って幅を異ならせる幅変動部を備え、幅変動部を備える導電層240と隣接する導電層のうち、少なくとも何れか一つには、これら導電層同士が交差しないその一つの導電層の非交差部に静電気を誘発させる電荷を集中させるためのダミー部241が備えられることを特徴とする。

(もっと読む)

半導体装置の製造方法及び表示装置

【課題】段差部における配線の被覆性の向上と、微細な配線の形成と、配線間における寄生容量の増加の抑制とが可能である半導体装置の製造方法を提供する。

【解決手段】基板の一方の主面側に、接続孔が形成された絶縁膜と上記絶縁膜上に形成された配線とを備える半導体装置の製造方法であって、上記製造方法は、液状導電性材料を用いて少なくとも接続孔内に導電部を形成する工程(導電部形成工程)と、ウェットエッチングにより接続孔内以外に形成された導電部を除去する工程(導電部除去工程)とを含む半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】 集積度が低下することを最大限抑制しつつ、必要に応じて大きい電流容量の確保を可能にしたコンタクトプラグを備えた半導体装置の製造方法を提供する。

【解決手段】 半導体基板1上にソース・ドレイン領域8を形成後、層間絶縁膜10を堆積し、ソース・ドレイン領域8の上面が露出するようにコンタクトホールを開口する。このとき、比較的小電流容量で機能を奏するロジック素子形成領域上面においては最小加工寸法で規定される程度の小さい孔径で開口する一方、大電流容量を必要とする保護素子形成領域上面においては、第1孔径よりも大きい第2孔径で開口する。その後、これらのコンタクトホールを完全に充填するように、コンタクトプラグ材料膜13を層間絶縁膜10の堆積膜厚以上成膜する。その後、コンタクトプラグ材料膜13に対して平坦化処理を行った後、配線層を形成する。

(もっと読む)

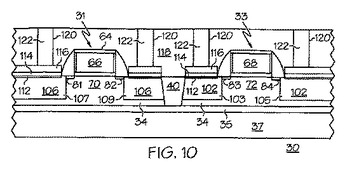

歪みが強化された半導体デバイスとその製造方法

歪みが強化された半導体デバイス30とその製造方法が提供される。1つの方法において、デバイスチャネル70、72に歪みを誘発するために、デバイスのソース領域103、107とドレイン領域105、109とに歪み誘発半導体材料102、106が埋め込まれる。誘発された歪みを緩和しないように、ソースおよびドレイン領域に対して薄い金属シリサイドコンタクト112が形成される。導電性材料114、116の層が薄い金属シリサイドコンタクトに接触して選択的に蒸着され、金属化されたコンタクト122が導電性材料に対して形成される。  (もっと読む)

(もっと読む)

エッチング方法

【課題】銅薄膜にダメージを与えないエッチング方法を提供する。

【解決手段】本発明では処理対象物10上でフッ素系ガスのプラズマを発生させ、電極溝18内に露出する銅薄膜(例えばソース電極21、ドレイン電極22)にフッ素化合物薄膜を予め形成しておくので、ハロゲンガスのプラズマでシリコン層17をエッチングする際に、銅薄膜がハロゲンガスのプラズマで腐食されない。シリコン層17をエッチングした後に、O2ガスのプラズマに曝すか、水洗すれば、銅薄膜表面に残留するハロゲンガスが除去されるので保存性も高くなる。

(もっと読む)

半導体装置

【課題】レーザ光を用いてウエハを個々のチップに分離する場合に、チップサイズをあまり大きくせずに、レーザ光の照射によって発生する熱がチップ内の回路素子に与える影響を低減する。

【解決手段】この半導体装置は、周辺領域に沿って不純物拡散領域が形成された半導体基板と、半導体基板上に形成された少なくとも1つの層間絶縁膜であって、半導体基板の周辺領域に沿って複数列のスルーホールが形成されている少なくとも1つの層間絶縁膜と、少なくとも1つの層間絶縁膜を介して形成された少なくとも1つの配線層であって、半導体基板の周辺領域に沿って略一定の幅で連続的に設けられ、少なくとも1つの層間絶縁膜に形成された複数列のスルーホールを介して不純物拡散領域に電気的に接続された周回パターンを有する少なくとも1つの配線層と、最上層の配線層上に設けられた保護膜とを具備する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】浅いソース、ドレイン接合位置を保ちつつ、ソース、ドレインがシリサイド化され、かつ、接合リークが低く抑えられた半導体装置の製造方法および半導体装置を提供する。

【解決手段】MISFET(金属絶縁物半導体電界効果トランジスタ)を有する半導体装置の製造方法であって、シリコン基板1100の表面に、このMISFETのゲート絶縁膜を形成し、このゲート絶縁膜上にゲート電極を形成し、このゲート電極の両側に、{110}面方位を有するシリコン面上に設けられ、このシリコン面上の<100>方向に垂直な長辺と、この<100>方向に平行で幅が0.5μm以下の短辺からなる矩形状を呈し、MISFETのソース、ドレイン領域の一部を構成する複数のニッケルシリサイド(NiSi)領域501a、502aを形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】無線信号から生成できる電流値及び電圧値の範囲内で駆動できるメモリを搭載した半導体装置を提供することを課題とする。また、半導体装置製造後にデータの書き込みを行える追記型のメモリを提供することも課題とする。

【解決手段】絶縁表面を有する基板上にアンテナと、アンチヒューズ型のROMと、駆動回路とを形成する。アンチヒューズ型のROMを構成する一対の電極の間に、シリコン膜とゲルマニウム膜との積層を設ける。この積層を有するアンチヒューズ型のROMは、書き込み電圧のバラツキを低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホール内に形成される銅プラグの接合リークの増加を抑制し、銅プラグの良好なコンタクトを達成できる半導体装置の製造方法を提供することである。

【解決手段】シリサイド層32を有する半導体基板1の上に絶縁膜38を形成し、さらに、シリサイド層32上の絶縁膜38にホール38fを形成し、ホール38f内とシリサイド層32の表面をクリーニングし、ホール38fの底面及び内周面に化学気相成長法によりチタン層41を形成し、銅拡散防止用のバリア層42をホール38f内のチタン層41上に形成し、銅層44をホール38f内に埋め込む工程を含む。

(もっと読む)

半導体装置の作製方法

【課題】レジストを使用することなく、薄膜加工を簡単な工程で精度良く行う方法を提案する。また、低コストで半導体装置を作製する方法を提案する。

【解決手段】基板上に第1の層を形成し、第1の層上に剥離層を形成し、剥離層側から剥離層に選択的にレーザビームを照射して一部の剥離層の付着力を低減させる。次に、付着力が低減された剥離層を除去し、残存した剥離層をマスクとして第1の層を選択的にエッチングする。また、基板上に剥離層を形成し、少なくとも剥離層に選択的に第1のレーザビームを照射して一部の剥離層の付着力を低減させる。次に、付着力が低減された剥離層を除去する。次に、残存した剥離層上に第1の層を形成し、残存した剥離層に第2のレーザビームを照射して残存した剥離層の付着力を低減させ、残存した剥離層及び当該剥離層に接する第1の層を除去する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】DRAM素子の微細化を進めた場合における、周辺回路側のトランジスタの短チャネル効果を抑制すると共に、コンタクト抵抗を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1と、半導体基板1の表面に形成されたMOSトランジスタTr2と、MOSトランジスタTr2のソース108A及びドレイン108Bにそれぞれ接続されるコンタクトプラグ11Aとを具備してなり、コンタクトプラグ11Aが、ソース108A及びドレイン108B上に形成されて不純物が拡散されたエピタキシャル成長層を含んでなることを特徴とする半導体装置を採用する。

(もっと読む)

81 - 100 / 156

[ Back to top ]