Fターム[5F033KK03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 半導体(基板を除く) (1,188)

Fターム[5F033KK03]の下位に属するFターム

Fターム[5F033KK03]に分類される特許

21 - 40 / 156

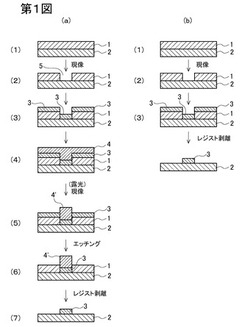

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

半導体記憶装置

【課題】さらなるDRAMの大記憶容量化を図る。

【解決手段】半導体記憶装置が、単結晶半導体材料を含む基板の一部を有する駆動回路と、当該駆動回路上に設けられる多層配線層と、当該多層配線層上に設けられるメモリセルアレイ層とを有する。すなわち、当該半導体記憶装置においては、駆動回路と、メモリセルアレイとが重畳して設けられる。したがって、単結晶半導体材料を含む基板に駆動回路及びメモリセルアレイを同一平面に設ける場合と比較して、当該半導体記憶装置の集積度を高めることが可能となる。

(もっと読む)

開口部の形成方法及び半導体装置の作製方法

【課題】少なくともフォトマスクの枚数を増加させることなく、積層構造の下部の導電層が露出するように該導電層上の絶縁膜に対する開口部の形成方法を提供する。

【解決手段】開口部が設けられる部分の積層構造の下部の導電層を、該開口部を形成するフォトマスクと同一のフォトマスクを用いて形成されたエッチングマスクにより予め露出させ、その後保護絶縁膜を形成し、前記積層構造の上部の導電層が開口部において露出されないように、保護絶縁膜に開口部を形成する。このような開口部の形成方法は、半導体装置の作製方法に適用することができる。

(もっと読む)

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】レンチ2内に埋め込まれた埋め込み絶縁膜3の一部を除去することで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1を形成し、空隙AG1は、制御ゲート電極8下に潜るようにしてトレンチ2に沿って連続して形成する。

(もっと読む)

ディスプレイ装置及びその製造方法

【課題】構造及び製造工程を簡素化しながら、開口率を向上させた、ディスプレイ装置及びその製造方法を提供する。

【解決手段】本発明の実施形態に係るディスプレイ装置101は、基板111、前記基板111上に形成された前記第1透明導電膜1301及び前記第1透明導電膜1301上に形成された第1金属膜1302を含む多重膜構造と前記第1透明導電膜1301で形成された単一膜構造とを含むゲート配線、前記ゲート配線の一部の領域上に形成された半導体層153、そして前記半導体層上に形成された第2透明導電膜1701及び前記第2透明導電膜1701上に形成された第2金属膜1702を含む多重膜構造と前記第2透明導電膜1701で形成された単一膜構造とを含むデータ配線を含む。

(もっと読む)

回路基板の製造方法

【課題】印刷法にて、回路基板に容易にヴィアホールを開口できる回路基板の製造方法を提供する事。

【解決手段】基板上に第一導電体を形成する第一導電体形成工程を行い、次に第一導電体を被覆する様に第一絶縁膜を成膜する第一絶縁膜成膜工程を行い、次に第一導電体上の第一絶縁膜に貫通孔32を開口して、第一導電体の表面を露出させる貫通孔形成工程を行い、次に第一導電体の表面を撥液化させる撥液化工程を行い、次に貫通孔32以外の領域に前駆体樹脂を印刷し、印刷後に前駆体樹脂を硬化して第二絶縁膜を形成する第二絶縁膜形成工程を行う。

(もっと読む)

半導体装置とその作製方法

【課題】特性が良好なトランジスタを提供する。

【解決手段】例えば、ボトムゲート・ボトムコンタクト構造のトランジスタを作製するに際して、ソースとドレインを構成する導電層を3層の積層構造とし、2段階のエッチングを行う。すなわち、第1のエッチング工程には、少なくとも第2の膜及び第3の膜に対するエッチングレートが高いエッチング方法を採用し、第1のエッチング工程は少なくとも第1の膜を露出するまで行う。第2のエッチング工程には、第1の膜に対するエッチングレートが第1のエッチング工程よりも高く、「第1の膜の下に接して設けられている層」に対するエッチングレートが第1のエッチング工程よりも低いエッチング方法を採用する。第2のエッチング工程後にレジストマスクをレジスト剥離液により剥離するに際し、第2の膜の側壁が少し削られる。

(もっと読む)

半導体装置及び製造方法

【課題】 基板及び表面層にビアホールが形成された半導体装置において、表面層の剥離及び破壊を抑制すること。

【解決手段】 本半導体装置は、基板10と、基板10上に設けられた基板10と異なる材料からなる表面層20と、表面層20上に設けられた電極パッド50と、を備え、基板10及び表面層20にはビアホール30が形成され、ビアホール30内には、電極パッド50と電気的に接続された金属層32が設けられ、ビアホール30の開口部の周囲には、ビアホール30を囲むように表面層20に溝22が形成されている。

(もっと読む)

半導体装置の作製方法

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置の作製方法を提供することを目的の一とする。

【解決手段】酸化物半導体膜と、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有する半導体装置の作製方法であって、酸化物半導体膜上に接して、酸化ガリウムを含む第1の絶縁膜を形成し、第1の絶縁膜上に接して第2の絶縁膜を形成し、第2の絶縁膜上にレジストマスクを形成し、第1の絶縁膜および第2の絶縁膜にドライエッチングを行ってコンタクトホールを形成し、レジストマスクを、酸素プラズマによるアッシングを用いて除去し、コンタクトホールを介して、ゲート電極、ソース電極またはドレイン電極のいずれか一または複数と電気的に接続される配線を形成する、半導体装置の作製方法である。

(もっと読む)

SiCの除去法

【課題】基板に形成されたカーバイドシリコン層の少なくとも露出された部分を除去するための方法を提供する。

【解決手段】カーバイドシリコン層45を酸素含有プラズマに曝すことにより、前記カーバイドシリコン層45の少なくとも露出された部分を酸化シリコン層に変換し、そして基板から前記酸化シリコン層を除去するステップからなる。

(もっと読む)

薄膜トランジスタ基板、および薄膜トランジスタ基板を備えた表示デバイス

【課題】金属配線膜のドライエッチングレートの低下やエッチング残渣を発生させることがなく、また該金属配線膜のヒロック耐性や電気抵抗率が抑制され、更に該金属配線膜と直接接続する透明導電膜や酸化物半導体層とのコンタクト抵抗率が抑制された薄膜トランジスタ基板、及び該薄膜トランジスタ基板を備えた表示デバイスを提供する。

【解決手段】薄膜トランジスタ基板であって、金属配線膜は、ドライエッチング法によるパターニングで形成された、Ni:0.05〜1.0原子%、Ge:0.3〜1.2原子%、Laおよび/またはNd:0.1〜0.6原子%を含有するAl合金膜とTi膜とからなる積層膜あって、該Ti膜が、該酸化物半導体層と直接接続していると共に、該Al合金膜が、該透明導電膜と直接接続している。

(もっと読む)

熱の抽出及び遮蔽のための埋込み式熱伝導層

【課題】多ブロック半導体デバイスにおいて熱を抽出しかつ遮蔽するための方法及び装置。

【解決手段】一実施形態は、互いに上下して積み重ねられる複数のブロック205,305は、熱伝導材料で充填される垂直バイア240,350によって相互に接続され、かつ埋込み式の熱伝導層340によって分離される。熱伝導層は、複数のブロックのうちの一番上または下へ熱抽出層または接地平面として接着される。熱伝導層は、高い熱伝導率を有する。基板110上には、断熱層210,320が堆積される。断熱層は、基板の加熱を低減するための温度勾配をサポートすることができる。断熱層の内部には埋込み式の熱伝導層が形成され、これは、基板を介して外部の熱抽出層へ接続される垂直バイアを有する。半導体層はこの断熱層上へ堆積され、電気配線用にパターン化される。

(もっと読む)

半導体装置およびその製造方法

【課題】3次元デバイスのような多層配線を有する半導体装置をより簡単な工程で作製する製造方法を提供する。

【解決手段】第1層10と第2層20とを、それぞれのTSV6が略一直線上になるように積層する半導体装置の製造方法で、基板の上面に入出力回路を構成するトランジスタ3を形成し、トランジスタ3を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第1層の製造工程と、基板20を準備し、基板の上面に論理回路を構成するトランジスタ13を形成し、トランジスタ13を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第2層の製造工程と、第1層のTSV6と第2層のTSV6とが略一直線上になるように、第1層と第2層の、基板の反対側面を接続する接続工程と、第1層の基板1を除去する工程とを含む。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を用いた、表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

電子モジュールの製造方法、および、電子モジュール

半導体基板に集積された回路と、基板と、ヒートシンクとしての支持体と、基板および支持体をはんだ付けにより接続する熱伝導性接続部とを備えた電子モジュールを提案する。ここでは、基板で用いられる後面金属化部として、まず第1の厚いAu層(23)、ついでバリア層(24)、最後に第2の薄いAu層(25)が堆積される。バリア層の材料は、はんだ付け過程において、第2のAu層の領域のAuSn液相のSnないしAuSnが第1のAu層(23)へ浸入することを阻止するように選定される。また、基板の貫通孔にも、後面金属化部の積層体が堆積される。ここで、第2のAu層の表面は、バリア層から拡散する材料によって、はんだ付け材料に対する低減された濡れ性を有する。  (もっと読む)

(もっと読む)

有機発光表示装置及びその製造方法

【課題】酸化物半導体層と多結晶シリコン半導体層を共に用い得る有機発光表示装置及びその製造方法を提供する。

【解決手段】基板本体と、基板本体上に形成された第1ゲート電極及び第2半導体層と、第1ゲート電極及び第2半導体層の上に形成されたゲート絶縁膜と、ゲート絶縁膜を介在して第1ゲート電極及び第2半導体層上にそれぞれ形成された第1半導体層及び第2ゲート電極と、第1半導体層と少なくとも一部が相接して重畳した複数のエッチングストッパ層と、複数のエッチングストッパ層をそれぞれ露出する複数のコンタクトホールを有し、第1半導体層及び第2ゲート電極上に形成された層間絶縁膜と、層間絶縁膜上に形成され、複数のエッチングストッパ層を通じて第1半導体層とそれぞれ直接的/間接的に接続された第1ソース電極及び第1ドレイン電極と、層間絶縁膜上に形成され、第2半導体層と接続された第2ソース電極及び第2ドレイン電極とを含む。

(もっと読む)

半導体装置

【課題】画素TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現し、信頼性と生産性を向上させる技術を提供することを課題とする。

【解決手段】画素領域に形成する画素TFTをチャネルエッチ型の逆スタガ型TFTで基板上に形成し、ソース領域及びドレイン領域のパターニングと画素電極のパターニングを同じフォトマスクで行う。また、ソース配線を画素電極と同じ材料である導電膜で覆い、基板全体を外部の静電気等から保護する構造とする。このような構成とすることで、製造工程において製造装置と絶縁体基板との摩擦による静電気の発生を防止することができる。特に、製造工程で行われる液晶配向処理のラビング時に発生する静電気からTFT等を保護することができる。

(もっと読む)

半導体装置、半導体装置の製造方法、および電子機器

【課題】IGZO層とITO層とを電気的に接続する場合には、易加工性を備え電気抵抗率が低いアルミ等の金属と高融点金属としてのチタン等との積層構造を用いる必要があるが、積層構造を形成する場合、複数の金属層を形成する必要がある。そのため製造工程が増えると共に、パーティクル等の発生確率が増え、歩留まりを落とすという課題がある。

【解決手段】ITO等の金属酸化物を用いた画素電極2aが、層間絶縁層9に形成されたコンタクトホール9aを介してIGZO層を用いた配線層7aと電気的に接続している。画素電極2aとAl−Nd合金を用いた上電極6cと直接接触させた場合、コンタクト抵抗が高くなるが、配線層7aにIGZO層を用い、画素電極2aにITO等の第2金属酸化物配線層を用いた場合、互いの構造が類似していることから、密接させるだけで接触抵抗の増大を招くことなく電気的に導通を取ることが可能となる。

(もっと読む)

21 - 40 / 156

[ Back to top ]