Fターム[5F033KK03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 半導体(基板を除く) (1,188)

Fターム[5F033KK03]の下位に属するFターム

Fターム[5F033KK03]に分類される特許

141 - 156 / 156

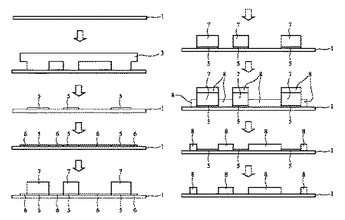

半導体装置の製造方法、半導体装置、表示装置および電子機器

【課題】目的とする方向に沿って正確に形成された細幅の導電膜を備える半導体装置を製造し得る半導体装置の製造方法、これにより製造された半導体装置、かかる半導体装置を備える表示装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板2上に半導体層5と、ソース電極3と、ドレイン電極4と、を形成する工程と、半導体層5上にゲート絶縁層6を形成する工程と、ゲート絶縁層6上に一定方向へ延びる溝61を複数形成する工程と、複数の溝61上に液状材料を吐出しゲート電極7を形成する工程とを有し、ゲート電極7は、複数の溝61に重なるように、この溝61と同一方向へ延在する。

(もっと読む)

導電性フィーチャへの接点を作る際の誘電体オーバーエッチングを低減するための方法

本発明の第1の好ましい実施形態において、導電性フィーチャが第1の誘電体エッチング停止層上に形成され、第2の誘電材料が導電性フィーチャ上およびその間に堆積される。第1の誘電体と第2の誘電体との間で選択的な導電性フィーチャへのバイアエッチングは、誘電体エッチング停止層上で停止し、オーバーエッチングを制限する。第2の実施形態において、複数の導電性フィーチャが減法的なパターン形成およびエッチングプロセスで形成され、誘電性充填材で満たされ、次に形成された表面が導電性フィーチャおよび誘電性充填材を同時露出する。誘電体エッチング停止層が表面に堆積させられ、次に第3の誘電体が誘電体エッチング停止層を覆う。第3の誘電体を貫通して接点がエッチングされると、この選択的エッチングは、誘電体エッチング停止層上で停止する。第2のエッチングが導電性フィーチャへの接点を作る。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の性能を向上させることが可能な技術を提供する。

【解決手段】半導体基板1には、NMOSトランジスタ11,31とPMOSトランジスタ21,41とが形成されている。NMOSトランジスタ11のゲート絶縁膜13と、PMOSトランジスタ21のゲート絶縁膜23とは、それぞれ、シリコン酸化膜及びシリコン窒化酸化膜よりも高い誘電率を有する膜から成る。NMOSトランジスタ31のゲート絶縁膜33は、下層膜33aと、その上に積層された、ゲート電極34と接触する上層膜33bとから成る。NMOSトランジスタ11のゲート絶縁膜13と、PMOSトランジスタ21のゲート絶縁膜23とは異なる材料から成り、NMOSトランジスタ11のゲート絶縁膜13と、NMOSトランジスタ31におけるゲート絶縁膜33の上層膜33aとは同じ材料から成る。

(もっと読む)

細線状MOSFETを含む半導体装置

【課題】 簡単な構成を採ることで、細線状素子領域に於けるソース領域及びドレイン領域からチャネル領域に向かって機械的な応力を効率良く印加し、キャリヤ移動度を向上させようとする。

【解決手段】 細線状チャネル領域4を挟んで細線状ソース領域8及び細線状ドレイン領域9が配設された細線状素子領域と、細線状ソース領域8及び細線状ドレイン領域9それぞれの少なくとも側面を覆う圧縮或いは引張の応力を発生する応力発生膜11或いは12とを備える。

(もっと読む)

半導体解析装置およびその方法

【課題】 本発明の目的は、低価格で簡単に半導体回路の故障解析をおこなうことができる半導体解析装置およびその方法を提供することにある。

【解決手段】 半導体解析装置は、絶縁層24および取り出し電極26の上に液体状の絶縁物12を塗布する手段と、塗布された絶縁物12を膜状にする手段と、膜状にされた絶縁物12を硬化させる手段と、を含む。また半導体解析装置は、絶縁物12にビアホールを形成する手段と、絶縁物12の上に導電性のパッドを形成し、かつ、取り出し電極26とパッドとを接続する手段と、を含む。

(もっと読む)

表面のパターン処理および制御された析出成長物を用いたビアの製造

本発明は、表面のパターン処理の方法、および制御された析出成長物を用いたビアの製造、ならびにそのような本発明による方法によって調製されたパターン化された基板に関する。本発明による方法は、上部に材料をパターン化する必要のある、少なくとも一つの表面を有する基板を提供するステップであって、前記表面は、異なる表面特性を有する少なくとも第1および第2の表面領域を有し、前記第1の領域には、さらに保護析出成長物が設置されるステップと、少なくとも前記第2の表面領域に、少なくとも一つの材料を設置するステップであって、前記設置された材料は、前記第1の表面領域には実質的に設置されないか、前記第1の表面領域に設置される場合、前記設置された材料は、前記第1の表面領域から選択的に除去されるステップと、を有する。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 良質でかつ良好な形状のサイドウォールを備えた半導体装置を形成する。

【解決手段】 ゲート電極側壁のサイドウォールを炭素含有シリコン窒化酸化膜を用いて形成する。炭素含有シリコン窒化酸化膜は、BTBASと酸素を原料に用い、BTBAS流量/酸素流量比を適当に設定すると共に、例えば約530℃等の低成膜温度のCVD法で成膜することができる。炭素含有シリコン窒化酸化膜を用いてサイドウォールを形成することで、窒素原子や炭素原子の寄与により、HF耐性向上やフリンジ容量低減を図れる。また、低温条件で成膜することにより、半導体基板内に導入されている不純物の不要な拡散が抑えられるようになる。これにより、トランジスタ特性を高めかつ安定化させ、半導体装置の高性能化、高品質化を図れるようになる。

(もっと読む)

絶縁膜の成膜方法及びその絶縁膜を備えた半導体装置

【課題】絶縁膜の成膜方法において、シリコン原子を堆積させる第1ステップと、シリコン原子を窒化する第2ステップとを有するALD法を用い、フラットバンド電圧及び界面準位の小さい好適な特性を有する薄い絶縁膜の成膜方法を提供する。

【解決手段】第1及び第2ステップでの成膜温度と圧力を同一とし、成膜温度を510℃以下の低温とし、圧力を70Pa以下、RFパワーを0.1KW以上とすることでフラットバンド電圧及び界面準位の小さい好適な特性の絶縁膜が得られる。これらの好適な絶縁膜を備えた半導体装置が得られる。

(もっと読む)

半導体装置とその製造方法

【課題】 周辺回路領域に形成されるロジック回路等に不具合が発生するのを防ぐことができるフラッシュメモリセルを備えた半導体装置とその製造方法を提供すること。

【解決手段】 第1導電体25aのコンタクト領域CR上の第2絶縁膜26を除去する工程と、第2絶縁膜26の上に第2導電膜30を形成する工程と、第1導電体25aのコンタクト領域CR上の第2導電膜30を除去し、該第2導電膜30を第2導電体30aとする工程と、第2導電体30aを覆う層間絶縁膜(第3絶縁膜)44を形成する工程と、コンタクト領域CR上の層間絶縁膜44に第1ホール44aを形成する工程と、コンタクト領域CRと電気的に接続される導電性プラグ45aを第1ホール44a内に形成する工程と、を有することを特徴とする半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】 微細な薄膜トランジスタの製造工程において、大型基板面内で均一性良く信頼性が高いコンタクトコールおよびコンタクト配線を形成する。

【解決手段】 層間絶縁膜9に対する10:1 BHFによるウェットエッチングに続いて、同一レジストマスク10を用いたドライエッチングを行うことにより、層間絶縁膜9およびゲート絶縁膜4にコンタクトホール11,12を連続して形成する。コンタクトホール11,12は、層間絶縁膜9の深さ方向途中まで設けられて、表面側に広く開口するテーパ状開口部と、このテーパ状開口部に連通し、層間絶縁膜9の深さ方向途中からソース/ドレイン領域3cが露出するまで設けられた表面に垂直な壁面の筒状開口部とを有する。

(もっと読む)

半導体装置、その製造方法、及び電子機器

【課題】製造工程を増加させることなく、エッチング工程においてコンタクトホールを形成するに際し、第1酸化膜と第2酸化膜との界面に切込み部が形成されず、コンタクトホールに形成される配線の断線を有効に回避することができるようにする。

【解決手段】第1酸化膜5と、この第1酸化膜5上に成膜された第2酸化膜8とを有する半導体装置において、第2酸化膜8が少なくともボロンを含む酸化シリコン膜であり、第2酸化膜8の第1酸化膜5との界面に形成される界面層8aのボロン濃度が高く設定されている。界面層8aのボロン濃度を高く設定することで、ウエットエッチングレートが遅くなり、両酸化膜5,8の界面に切込み部が形成されることが防止される。

(もっと読む)

回路基板、電気光学装置、及び電子機器

【課題】 トランジスタ等の能動素子が安定に動作し、大画面化と長期にわたって安定した表示動作とを可能にする。

【解決手段】 陰極(222)と陽極(23)とに狭持され、基板(2)の上方に配置された電気光学素子と、電気光学素子を駆動する能動素子(24)と、陰極(222)及び陽極(23)のうち少なくとも一方と基板(2)との間に配置された誘電率が所定の値以下の絶縁材料からなる絶縁膜(283、284)とから電気光学装置(1)を構成する。

(もっと読む)

半導体装置

【課題】 ダマシン配線構造体を有する半導体装置において、シールリングと配線あるいは電極パッドとの短絡発生を無くする。

【解決手段】 半導体装置の層間絶縁膜の溝側壁に形成され導電性のバリア材料膜から成る上層バリア層4、溝内に埋め込まれ配線材料膜から成るたとえば10μm幅の上層シールリング配線5が設けられ、上層シールリング配線5内に混在して複数の島状の絶縁体6が形成されている。この島状の絶縁体6は、上記ダマシン配線が形成される層間絶縁膜により形成される。そして、素子形成領域に第1上層溝配線7、第2上層溝配線8等が配設され、上層バリア層4がその周囲に設けてある。ここで、上層シールリング配線5および両上層配線は共に(デュアル)ダマシン配線構造になる。

(もっと読む)

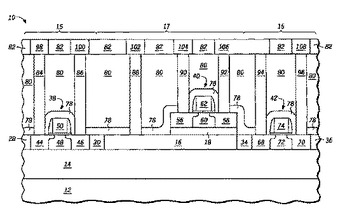

複数の半導体層を備えた半導体デバイス

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

半導体装置

【課題】Low−k膜を層間絶縁膜として用いた半導体装置であっても、ダイシング時に発生するクラックがシールリング部へ伝播するのを抑制し、半導体装置の信頼性を向上する技術を提供する。

【解決手段】ダイシング領域側の各層にダミービア125,135,145,155,165を形成する。ダミービア125,135,145,155,165は上面からみて、縦横に等間隔に形成する。ダイシング時にクラックが発生しても、ダミービア125,135,145,155,165によって、クラックがシールリング部190にまで伝播するのを抑制することができる。その結果、回路形成領域の吸湿耐性を向上させ、信頼性の劣化を防止することができる。

(もっと読む)

配線構造およびその製造方法

【課題】感光性絶縁膜を用いたダマシン配線法により、微細で信頼性の高い多層配線構造を形成する。

【解決手段】感光性ポリシラザンを主成分とした感光性絶縁膜で第1ビアホール6を有するビアホール用絶縁膜7を形成し、全面にスピン塗布法で第2の感光性絶縁膜8を形成する。そして、フォトリソグラフィ法による露光/現像のみで上記第1ビアホール6の上部に配線溝9あるいは第2ビアホール10を形成する。そして、この配線溝9および第2ビアホール10に導電体材料を埋め込んでデュアルダマシン配線を形成する。ここで、感光性絶縁膜の下層に反射防止機能を有しそのまま層間絶縁膜として使用できる絶縁膜を形成する。

(もっと読む)

141 - 156 / 156

[ Back to top ]