Fターム[5F033KK12]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Cu (2,449) | Cu合金 (304)

Fターム[5F033KK12]に分類される特許

141 - 160 / 304

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、ダマシン構造を有する銅多層配線を構成するトレンチのCMP工程後に露出した低誘電率膜表面のダメージを回避して配線信頼性を確保するとともに、直列抵抗の増大を抑制する。

【解決手段】 ポーラス絶縁膜に設けた凹部に埋め込まれた第1の金属膜の少なくとも頂面を、前記ポーラス絶縁膜の頂面と整合する高さまでZr及びBを含む第2の金属膜で覆う。

(もっと読む)

半導体装置

【課題】配線の幅広配線部から突出した凸状配線部に形成されたビアについて、ストレスマイグレーション耐性を向上し得る半導体装置を提供する。

【解決手段】第1の配線18と、第1の配線18の上方に形成され、第1の配線18に接続されたビア38を一体的に有する第2の配線34と、ビア38に隣接して配置され、ビア38と同層に形成された複数のダミービア40a、40b、40c、40dとを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部端子に加わる外力により外部端子の下方の絶縁膜にクラックが生じるのを抑制または防止する。

【解決手段】半導体基板1の主面上には複数の配線層が形成されている。この複数の配線層のうちの最上の配線層MHの直下の第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成しない。上記第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下以外の領域には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体装置の配線層の信頼性を高める。

【解決手段】層間絶縁膜3に形成した配線溝4内に、バリアメタル膜5を介して、CuMnシード膜6及びCu膜7を有する配線部1を形成した後、SiH4とNH3のガスに曝し、その配線部1の表面にOを含有しないSiNの保護層8を形成する。この上にキャップ膜9を形成する。キャップ膜9の形成時には、配線部1のバリアメタル膜5との界面領域にはMnO層10が形成される一方、配線部1の上面には保護層8があることでMnの析出が抑制される。配線部1のMn含有量を高めても、配線部1とキャップ膜9との間にMnを含有するバリア性の低い層が形成されることがなく、エレクトロマイグレーション耐性及びストレスマイグレーション耐性の向上を図ることができる。

(もっと読む)

半導体集積回路装置

【課題】複数層の埋め込み配線を有する半導体集積回路装置において、埋め込み配線と底部にて接続するプラグとその埋め込み配線との界面でのストレスマイグレーションによる導通不良を防ぐ。

【解決手段】たとえば、Cu配線33Wの幅が約0.9μm以上かつ約1.44μm未満であり、Cu配線43の幅およびプラグ43Pの径が約0.18μmである場合において、Cu配線33W上にてCu配線33WとCu配線43とを電気的に接続するプラグ43Pを2個以上配置する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】生産性を向上することができ、凹部の計測を正確に行うことができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、第一絶縁膜11中に形成された平膜状の第一遮光膜12と、この第一遮光膜12の上部に設けられ、複数の凹部131が形成された第二絶縁膜13とを有する。遮光膜12は、平面視において、中心から外郭までの距離が2μm以上であり、遮光膜12上に第二絶縁膜13の複数の凹部131が位置する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化によっても配線間ショートによる不良の発生を確実になくしつつ、EM耐性をより向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上の第一の層間絶縁膜2に配線溝を形成し、その配線溝に第一のCu膜4を堆積して第一のCu配線5を形成し、その第一のCu配線5上および第一の層間絶縁膜2上に第一のライナー膜6を形成し、その第一のライナー膜6に第一のCu配線5の表面が露出するように第一のCu配線5上に開口部13を部分的に形成し、その開口部13内に露出した第一のCu配線5の表面にキャップメタル膜7を形成する。

(もっと読む)

半導体装置

【課題】電気ヒューズを切断する際のショートを防ぐことができる。

【解決手段】半導体装置100は、半導体基板(不図示)上に形成され、それぞれ異なる層に形成された第1の配線122と、第2の配線134と、第1の配線122と第2の配線134の間の層に設けられ、第2の配線134の一端部分に接続されるとともに第1の配線122に接続されたビア128とを含む電気ヒューズ200と、第2の配線134と同層に形成され、第2の配線134の一端部分の周囲を取り囲むように形成されたガード配線部160とを含む。平面視において、第2の配線134は、他端から一端部分の方向に延在して形成され、ガード配線部160は、第2の配線134の一端部分を中心として、当該一端部分の周囲三方を取り囲むように形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】Cu配線パターンの表面に自己形成されるMn酸化物膜よりなるバリア膜を有する多層配線構造において、配線の寿命を向上させる。

【解決手段】Cu−Mn合金層を側壁に形成したCu配線パターンの表面に、炭素および酸素源となる炭素含有膜を接触させ、熱処理により、前記Cu−Mn合金層中のMn原子と前記炭素源からの炭素原子と酸素原子を反応させ、炭素を含むMn酸化物膜をバリア膜として形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】高融点金属元素を含むバリアメタル膜と組みあわせてCu配線パターンのバリアメタル構造を形成するCu−Mn合金層において、ストレスマイグレーション耐性を向上させると同時に、Cu配線パターンの抵抗を低減する。また、さらには配線中のボイド欠陥を低減する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上方に形成された酸素を含む絶縁膜と、前記絶縁膜に形成された凹部と、前記凹部の内壁に形成された銅を含む第1の膜と、前記第1の膜上方であって、前記凹部に埋め込まれた銅を含む第2の膜と、前記第1の膜と前記第2の膜の間にマンガンを含む酸化層と、を有する。さらに、前記構造に対し、電解メッキ法で銅配線を形成し、引き続き80℃〜120℃の温度で短時間の熱処理を行う。

(もっと読む)

半導体装置

【課題】半導体装置のボンディングパッドに加えられる外部からの、特定箇所への応力集中を緩和しつつ、半導体装置の製造容易性を向上させることを可能とする構造を備える半導体装置を提供する。

【解決手段】半導体層の上に位置する、第4メタル配線層が延びる方向と、第4配線層の上に位置する第3配線層ML30,37が延びる方向とが直交するように設けられている。これにより、上方に位置するボンディングパッドBP1,BP2に外部から応力が加えられた場合であっても、下方に伝達された力は、互いに交差するように積層配置された第3配線層および第4配線層により、応力が全体に分散され、特定箇所への応力集中を緩和し、半導体装置の強度劣化を最小限に抑制することを可能とする。

(もっと読む)

多層配線の形成方法

【課題】実効的な低配線間容量を維持しつつ、高密着性かつ高い配線間絶縁信頼性を有する多層配線の形成方法を提供する。

【解決手段】本発明に係る多層配線の形成方法は、シロキサン構造を含むビア層間絶縁膜43及び配線層間絶縁膜44を金属配線41a上に形成する第一の工程(図1[1])と、ビア層間絶縁膜43及び配線層間絶縁膜44の一部に金属配線41aに達する凹部としてのデュアルダマシン溝48を形成する第二の工程(図1[2]〜図2[2])と、ビア層間絶縁膜43及び配線層間絶縁膜44とデュアルダマシン溝48内で露出した金属配線41aとに水素プラズマ処理を施すことにより、ビア層間絶縁膜43及び配線層間絶縁膜44の表面に改質層49を形成するとともに金属配線金属配線41aの表面を還元する第三の工程(図3[1])と、を含むことを特徴とする。

(もっと読む)

表示装置およびこれに用いるCu合金膜

【課題】電気抵抗率が従来のCu合金膜よりも低く、且つ、バリアメタルを形成せずとも透明導電膜との間で低コンタクト抵抗の直接接続を実現でき、液晶ディスプレイなどに適用した場合に高い表示品質を与えることのできる表示装置用Cu合金膜を提供する。

【解決手段】基板上にて、透明導電膜5,41に直接接続する表示装置用Cu合金膜25,26,34であって、該Cu合金膜は、Geを0.1〜0.5原子%含有し、かつNi、Zn、Fe、及びCoよりなる群から選択される1種以上を合計で0.1〜0.5原子%含有することを特徴とする表示装置用Cu合金膜。

(もっと読む)

電子装置及びその製造方法

【課題】 電子装置及びその製造方法に関し、エッチングストッパ膜となる絶縁膜に過度のダメージを与えることなく、塗布系の低誘電率膜との密着性をバラツキなく改善する。【解決手段】 基板9上に形成されたSi−CH2 −Si構造を10〜90重量%含有するシリコンオキシカーバイドからなる第1の絶縁膜1と、第1の絶縁膜1上に形成されたポーラスシリカ系の第2の絶縁膜3とを有し、第1の絶縁膜1と第2の絶縁膜3の界面において、第1の酸素4と二重結合している炭素5を介して、第1の珪素6と、第2の珪素7と結合した第2の酸素8とが連結された構造を形成する。 (もっと読む)

半導体装置及びその製造方法

【課題】同一配線層の配線間における実効誘電率の増大及び配線幅のばらつきの増加を解消しつつ、ナノホールパターンの形成時における反射率差に起因する課題と、エッチングによる配線信頼性低下の課題とを同時に解決できるようにする。

【解決手段】半導体装置は、半導体基板の主面に垂直な方向に筒状に延びる複数の空間部である第1のナノコラム型ホール11bを有する第1の層間絶縁膜11と、該第1の層間絶縁膜11に選択的に形成された下層配線12とを有している。下層配線12の上部には、金属又は金属を含む材料からなるキャップ膜12cが形成されている。

(もっと読む)

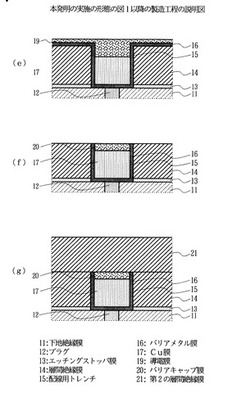

半導体集積回路装置およびその製造方法

【課題】SiOF膜を含む層間絶縁膜にダマシン法で埋め込み配線を形成する半導体集積回路装置において、埋め込み配線用の配線溝を形成する際に用いるエッチングストッパ層とSiOF膜との界面剥離を防止する。

【解決手段】SiOF膜26、29を含む層間絶縁膜をドライエッチングして形成した配線溝32の内部にダマシン法でCu配線33を埋め込む際、上記ドライエッチングのエッチングストッパ層を構成する窒化シリコン膜28とSiOF膜26との間に酸窒化シリコン膜27を介在させ、SiOF膜26中で発生した遊離のFを酸窒化シリコン膜27でトラップする。

(もっと読む)

パターン形成方法及びそれを利用した表示装置の製造方法

【課題】

互いにパターン(平面形状)の異なる2種類以上の薄膜を積層した積層構造を形成する工程にて、1回のフォトリソグラフィ工程で夫々の薄膜形状を画定すること。

【解決手段】

基板1上に2層の薄膜3,2を順次成膜し、次に薄膜2の上面に形成された第1マスクパターン4を用いて薄膜2のエッチングを行い、第1の薄膜パターン6を形成する。その後、第1マスクパターン4を残した状態で第1マスクパターン4及び薄膜2の上に、有機材料のオフセット印刷、インクジェット印刷、又はディスペンサノズルによる追加塗布で第2マスクパターン5を形成する。最後に、薄膜3を第1マスクパターン4及び第2マスクパターン5を用いて第2の薄膜パターン7に成形し、続いて2つのマスクパターン4,5を除去する。以上の工程により、フォトリソグラフィが第1マスクパターン4を形成する1回のみに制限されるも、基板1の主面に所望の積層構造が形成される。

(もっと読む)

半導体装置

【課題】ビアの断線不良の発生を防止することができる、半導体装置を提供する。

【解決手段】第2層間絶縁膜7およびSiC膜6を挟んで、Cuからなる下層配線4および上層配線11a,11bが形成されている。下層配線4と上層配線11aとは、Cuからなるビア12aにより電気的に接続されている。また、下層配線4と上層配線11bとは、Cuからなるビア12bにより電気的に接続されている。そして、下層配線4には、Cuからなり、下層配線4と上層配線11a,11bとの電気接続に寄与しないダミービア13が接続されている。ダミービア13は、ビア12a,12bよりも小さなビア径を有している。

(もっと読む)

半導体装置

【課題】高速化および高集積化の双方を両立可能な半導体装置を提供する。

【解決手段】CMOSインバータNT1、PT1がスタンダードセル51aに含まれている。電源線は、CMOSインバータNT1、PT1に電気的に接続され、かつ下層配線32a、32bおよび上層配線34c、34dを有している。下層配線32a、32bは互いに隣り合うスタンダードセル51aの境界に沿って境界上に延在している。上層配線34c、34dは平面視において下層配線32a、32bよりもスタンダードセル51aの内側に位置している。CMOSインバータNT1、PT1は上層配線34c、34dを介して下層配線32a、32bに電気的に接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】表面が平坦なバンプ電極を有する半導体装置及び半導体装置の製造方法を提供する。

【解決手段】表面に電極パッド13が形成された半導体チップ11、電極パッド13の上に配置され、半導体チップ11と対向する上面が平面をなす上部配線層17、上部配線層17の上面と同一面をなし、上部配線層17の側面と接し、半導体チップ11の表面を被うパシベーション膜15、上部配線層17及び上部配線層17の周囲のパシベーション膜15の上に配置され、上部配線層17と接続されたバンプ下地金属21、及び平面をなすバンプ下地金属21の上に側面を共有して配置され、所定の膜厚の金バンプ25とを備える。

(もっと読む)

141 - 160 / 304

[ Back to top ]