Fターム[5F033KK12]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Cu (2,449) | Cu合金 (304)

Fターム[5F033KK12]に分類される特許

121 - 140 / 304

電子装置及びその製造方法

【課題】絶縁膜とCuを含む配線との間に介在する下地膜であって、特に酸素のバリア性が高い下地膜を含む電子装置を提供する。

【解決手段】電子装置は、凹部の形成された絶縁膜と、凹部内に形成され、Cuを含む配線層と、絶縁膜と前記配線層との間に形成され、Ta及びMnを含む下地膜とを有する。

(もっと読む)

電磁波検出素子

【課題】信号配線の電子ノイズをより低減させた電磁波検出素子を提供する。

【解決手段】走査配線101(2)、信号配線3、及び共通配線102(18)をセンサ部103よりも下層に各々絶縁膜を介して設けられた異なる金属層により形成されており、信号配線3を走査配線101及び共通配線102よりも厚く形成した。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程を複雑化することなく、配線の信頼性低下を招かない、配線構造を有する半導体装置及びその製造方法を得る。

【解決手段】接続孔30の底面及び側面上並びに配線用溝31の底面及び側面上にTa/TaN積層バリア層12を介して、NiFe磁性層13をPVD装置のNiFeチャンバを用いたPVD法によって成膜する。次に、同一のPVD装置の同一のNiFeチャンバを用いて、成膜条件を変更することにより、接続孔30及び配線用溝31の底面上及び層間絶縁膜11の表面上におけるNiFe磁性層13を選択的に除去する。さらに、同一のPVD装置のTaチャンバ及びCuチャンバを用いて、接続孔30の底面及び側面上並びに配線用溝31の底面及び側面上にTaバリア層及びCuシード層を順次形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗上昇や表面の電極パッドの突き抜けを防止できる構造を備えた固体撮像装置を提供する。

【解決手段】 半導体装置は、半導体基板6を貫通して形成された貫通電極5と、貫通電極5の上に形成され、貫通電極5と電気的に接続する導電体からなる導電体パッド14と、半導体基板6の表面に形成され、導電体パッド14と電気的に接続する配線層3とを備える。

(もっと読む)

導電性コンタクトの組み込みのための構造体及びプロセス

【課題】 キーホール・シームの形成を排除した信頼性が高い高アスペクト比のコンタクト構造体を含む半導体構造を提供する。

【解決手段】 キーホール・シームの形成は、本発明においては、誘電体材料内部に存在する高アスペクト比のコンタクト開口部内に高密度化貴金属含有ライナを設けることによって排除される。高密度化貴金属含有ライナは拡散バリアの上に配置され、これら両方の要素は、本発明のコンタクト構造体の導電性材料を、下層の半導体構造体の導電性材料から分離する。本発明の高密度化貴金属含有ライナは、第1の抵抗率を有する貴金属含有材料の堆積、及び、堆積した貴金属含有材料の抵抗率をより低い抵抗率に減少させる高密度化処理プロセス(熱又はプラズマ)を、堆積した貴金属含有材料に施すことによって形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜中の水分による配線メタルの腐食を防止することができ、配線の信頼性向上をはる。

【解決手段】埋め込み配線を有する半導体装置であって、一部に配線用溝113が形成された配線間絶縁膜111,112と、配線間絶縁膜111,112の配線用溝113内に埋め込み形成され、且つ配線用溝113の側壁面との間にギャップを有する金属配線層115と、配線層115の側壁面と上面を覆うように形成された耐水性バリア層118とを備えた。

(もっと読む)

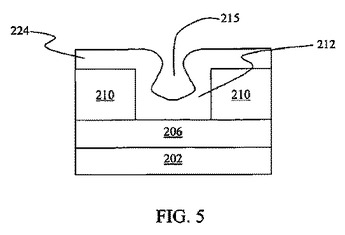

半導体素子のためのキャパシタおよびその製造方法

【課題】ダマシン構造に組み込まれたキャパシタを有する半導体素子を提供する。

【解決手段】キャパシタ25は、ダマシン構造内の半導体素子構成要素を有するダマシン構造の金属化層内全体に形成される。好ましくは、金属層の誘電体内にエッチングされる溝内にキャパシタは形成され、キャパシタは金属層の素子構成要素16に電気的に接続する凹部内部に形成される第1のキャパシタ電極26を包含する。絶縁体30上に形成される第2のキャパシタ電極27と共に絶縁体は前記第1のキャパシタ電極上に形成されるのが好ましい。これらの要素は凹部を形成するように、溝に適合するように堆積されるのが望ましく、その一部は溝内部に延在する。次に形成される素子構成要素は、第2のキャパシタ電極に電気的に接触するようにされる。

(もっと読む)

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

半導体装置

【課題】切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】半導体装置200は、基板上に形成された下層配線120と、下層配線120上に下層配線120に接続して設けられたビア130と、ビア130上にビア130に接続して設けられた上層配線110とを含み、切断状態において、上層配線110を構成する導電体が上層配線110の外方に流出してなる流出部が形成されることにより切断される電気ヒューズ100と、少なくとも上層配線110と同層に形成され、上層配線110に生じる熱を吸収するガード上層配線152(導電吸熱部材)とを含む。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供すること。

【解決手段】半導体装置1は、半導体基板(図示略)と、半導体基板上に設けられた第一の電気ヒューズ12と、第二の電気ヒューズ13とを備える。第一の電気ヒューズ12は、異なる配線層に形成された第一の上層配線121および第一の下層配線122と、第一の上層配線121および第一の下層配線122を接続するビア123とを有する。第二の電気ヒューズ13は、異なる配線層に形成された第二の上層配線131および第二の下層配線132と、第二の上層配線131および第二の下層配線132を接続するビア133とを有する。半導体装置1は、第一の電気ヒューズ12の前記第一の上層配線121と、第二の電気ヒューズ13の第二の下層配線132とを接続する接続部14を有する。この接続部14は、第一の電気ヒューズ12および第二の電気ヒューズ13を直列に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体の製造工程において、層間絶縁膜へのダメージを極力抑えることが可能な配線の還元処理方法の開発。

【解決手段】本発明は、基板上に導電部材および絶縁膜を有する半導体装置の製造方法であって、該方法は、基板上に導電部材を形成する工程、該導電部材上に絶縁膜を形成する工程、該導電部材上の絶縁膜を除去する工程、該導電部材上の酸化された領域を還元するために有機シランガスおよび水素ガスをブローする工程からなり、ここで該導電部材上の酸化された領域は、該絶縁膜が除去されたときに形成されることを特徴とする。

(もっと読む)

三次元構造体の製造方法および三次元構造体

【課題】導電体内の欠陥の発生を抑制し、導電体が連続的に形成される三次元構造体の製造方法および三次元構造体を提供する。

【解決手段】第1の導電体上に、絶縁体と、この絶縁体内に、第1の導電体と異なる第2の導電体で構成される縦構造体と横構造体が組み合わされた三次元の擬似導電体構造とを形成する工程と、擬似導電体構造を溶解除去して三次元の空洞を形成し、第1の導電体を露出させる工程と、第1の導電体をシード層として、電解めっき法により第3の導電体を空洞に充填し、三次元の導電体構造を形成する工程を有することを特徴とする三次元構造体の製造方法およびこれによる三次元構造体。

(もっと読む)

半導体装置の製造方法、半導体装置、電子機器、半導体製造装置及び記憶媒体

【課題】基板上の凹部が形成された層間絶縁膜の露出面にバリア膜を成膜し、凹部内に下層側の金属配線と電気的に接続される銅配線を形成するにあたり、段差被覆性の良好なバリア膜を形成することができ、しかも配線抵抗の上昇を抑えた半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜に形成された凹部21の底面に露出した下層側の銅配線13の表面の酸化膜を還元あるいはエッチングして、当該銅配線13の表面の酸素を除去した後、マンガンを含み、酸素を含まない有機金属化合物を供給することによって、凹部21の側壁及び層間絶縁膜の表面などの酸素を含む部位に自己形成バリア膜である酸化マンガン25を選択的に生成させる一方、銅配線13の表面にはこの酸化マンガン25を生成させないようにして、その後この凹部に銅を埋め込む。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体製造検査装置、および検査装置

【課題】配線幅の変遷に影響されない、表面欠陥を実用可能なレベルよりさらに低いレベルまで低減できる基本的な結晶構造を具備したCu配線を有する半導体装置及びその検査技術を提供する。

【解決手段】半導体装置において、バリア膜及びシード膜を特定すると共に、Cu配線の全ての結晶粒界に占める、粒界Σ値27以下の対応(CSL)粒界の割合(頻度)を60%以上とすることにより、表面欠陥を実用可能な現状レベルの1/10以下まで低減できる。または、該半導体装置において、バリア膜及びシード膜を特定すると共に、Cu配線の全ての結晶粒界に占める、粒界Σ値3の対応(CSL)粒界の割合(頻度)を40%以上とすることにより、表面欠陥低減の同様の効果を得ることができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ワイヤボンディングで実装されるチップとバンプ電極で実装されるチップとで、製造工程を共通化できる技術を提供する。

【解決手段】バンプ電極によりチップ1が外部との電気的接続を行う場合においても、ボンディングワイヤによりチップ1が外部との電気的接続を行う場合においても、1本の最上層の配線7にバンプ接続部15およびボンディングパッド16の両方を設ける。バンプ電極を用いる場合にはバンプ接続部15上の絶縁膜に開口部を設け、ボンディングパッド16上は絶縁膜で覆う。一方、ボンディングワイヤを用いる場合にはボンディングパッド16上の絶縁膜に開口部を設け、バンプ接続部15上は絶縁膜で覆う。

(もっと読む)

基板モジュールおよびその製造方法ならびに電子機器

【課題】基板モジュールの製造工程中において、絶縁層の剥離ならびに接続電極の断線および剥離が発生する虞があった。

【解決手段】基板モジュール1では、接続電極4が基板2の第一の表面2a上に設けられており、第一の貫通孔部5が接続電極4の裏面に達するように基板2の厚み方向に貫通しており、第一の貫通孔部5の内部には貫通電極6が設けられている。貫通電極6は接続電極4の裏面に対向する部分に凹部6aを有し、貫通電極6の上部は貫通電極6の側部よりも分厚い。貫通電極6は、基板2の第二の表面2b上にも設けられており、第二の表面2b上において配線電極7に接続されている。絶縁層8が配線電極7の表面を覆うように第二の表面2b上に設けられており、貫通電極6の凹部6a内にも設けられている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置70には、積層形成される配線膜6及び10から構成される配線層が設けられる。キャップ膜3上に形成される層間絶縁膜4の第1の開口部には、配線膜6が埋設される。配線膜6の底部及び側面部にはバリアメタル膜5が設けられる。層間絶縁膜4及び配線膜6上に形成されるキャップ膜7及び層間絶縁膜8の第2の開口部には、配線膜10が埋設される。配線膜10の底部及び側面部にはバリアメタル膜9が設けられる。層間絶縁膜8及び配線膜10上に形成される。配線膜10は配線膜6上に設けられ、配線膜10の端部は配線層6の端部よりも内側に設けられる。

(もっと読む)

表示装置およびこれに用いるCu合金膜

【課題】Cu系材料の特徴である低電気抵抗率を維持しつつ、絶縁膜(例えばSiN膜)との密着性に優れた、表示装置用Cu合金膜を提供する。

【解決手段】表示装置における薄膜トランジスタの、ソース電極および/またはドレイン電極並びに信号線、および/または、ゲート電極および走査線に用いられるCu合金膜であって、該Cu合金膜は、Geを0.1〜0.5原子%含有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】Ru材料をCu配線のバリアメタル膜として使用した際、CMP時にCu溶出の発生しないCu配線形成方法を提供する。

【解決手段】層間絶縁膜上面の第1のバリアメタル上に形成された第2のバリアメタル膜(Ru膜)を除去する工程(d)と、前記工程(d)の後に、前記第1及び第2のバリアメタル膜上にシード銅(Cu)膜を堆積する工程(e)とを有する。このように、シード銅膜を形成する前に、上面の第2のバリアメタル膜を除去してしまうことにより、この第2のバリアメタル膜と銅との電池効果で、銅がスラリー中に溶出することを防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】エアギャップにビアが侵入することを防止すると共に配線間容量のさらなる低減を図り、また、空隙部を有する多層配線構造の機械的強度の向上及び酸化性物質の拡散防止を図り、歩留まりの低下を抑止できるようにする。

【解決手段】半導体装置は、第1の層間絶縁膜101と、第1の層間絶縁膜101に形成された複数の第1の配線105とを有している。第1の層間絶縁膜101における複数の第1の配線105の隣り合う配線同士の間には、空隙部112が選択的に形成されており、空隙部112の上で且つ配線同士の間に形成されたキャップ絶縁膜111が形成されている。空隙部112における下端部の幅及び上端部の幅は、空隙部112と隣接する配線同士の間隔と同一であり、空隙部112の下端部の位置は、該空隙部112と隣接する第1の配線105の下端部の位置よりも低い。

(もっと読む)

121 - 140 / 304

[ Back to top ]