Fターム[5F033KK36]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 炭化物 (42)

Fターム[5F033KK36]に分類される特許

1 - 20 / 42

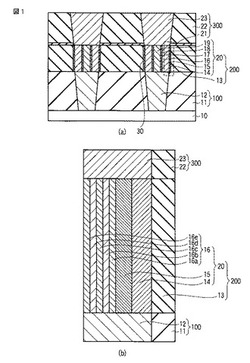

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線は、配線溝を有する絶縁膜13と、前記配線溝内の両側面の前記絶縁膜上に形成された第1触媒膜15と、前記配線溝内の両側面の前記第1触媒膜上に形成され、両側面に対して垂直方向に積層された複数のグラフェンシートで構成された第1グラフェン層16と、を具備する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バリアメタルの被覆性を向上させる。

【解決手段】本発明の半導体装置は、キャップ絶縁膜1d上に形成された絶縁膜と、絶縁膜に形成された配線溝と、配線溝の底面に形成されたビア孔と、少なくともビア孔の側壁を覆うバリアメタル膜と、を有する。ビア孔は、径が異なる複数の孔から構成されており、複数の孔は、下に向けて径が小さくなるように深さ方向に接続し、複数の孔の接続部にキャップ絶縁膜に対してほぼ平行な面を有する。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

配線構造体の製造方法及び配線構造体

【課題】 横方向(基板表面に平行な方向)にカーボンナノチューブを成長させるためには、側壁に平坦かつ微小な表面を持つ触媒膜を形成する必要がある。ところが、このような触媒膜を形成することは困難である。

【解決手段】 基板表面の相互に離隔した2つの縦配線領域に、第1の厚さの縦配線用触媒膜を形成し、1つの縦配線領域から他の縦配線領域まで連続する横配線領域に、第1の厚さよりも厚い第2の厚さの横配線用触媒膜を形成する。縦配線用触媒膜及び横配線用触媒膜の上に、カーボンを含む構造体を気相成長させる。気相成長の初期段階には、縦配線用触媒膜及び横配線用触媒膜の上にグラファイトが形成され、その後、縦配線領域の前記グラファイトと基板との間にカーボンナノチューブが成長し、横配線領域の前記グラファイトが、縦配線領域に成長したカーボンナノチューブによって中空に支持されるように第1の厚さ及び第2の厚さが設定されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】エアギャップ部を有し、かつ、高い機械的強度を有する半導体装置およびその製造方法を提供する。

【解決手段】酸素を含有する層間絶縁膜IL1の複数の溝部の側壁を被覆するバリア金属層ALが形成される。複数の溝部を充填するように配線金属層PCが形成される。層間絶縁膜IL1の酸素を熱拡散させることによってバリア金属層ALの少なくとも一部を酸化することで、酸化物バリア層BL1が形成される。配線金属層のうち複数の溝部の外側の部分を除去することによって、第1および第2の配線間領域IW1,IW2と第1〜第3の配線WR1〜WR3とが形成される。第1の配線間領域IW1を覆い、かつ第2の配線間領域IW2上に開口部OPを有するライナー膜LN1が形成される。開口部OPを介したエッチングが行なわれる。

(もっと読む)

半導体装置及びその製造方法

【課題】高速動作が可能なMIPS構造を持つメタルゲートを含む半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜3と、該ゲート絶縁膜3の上に順次形成され、TiN膜4とポリシリコン膜5とにより構成されたゲート電極20の第2のゲート電極部20bと、半導体基板1の上にゲート電極20を覆うように形成された層間絶縁膜8とを有している。層間絶縁膜8及びポリシリコン膜5を貫通して形成されたコンタクト9は、TiN膜4と直接に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極である金属膜/多結晶シリコン膜間の接触抵抗が大きい場合であっても、ゲートコンタクトプラグに印加した電界を十分な速度で十分に金属膜に伝えることができる半導体装置、およびその製造方法を得ることを目的とする。

【解決手段】本発明の一実施形態における半導体装置は、半導体基板1と、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成された金属膜4、当該金属膜4上に形成された多結晶シリコン膜5、を有するゲート電極6と、ゲート電極6上に形成された層間絶縁膜11と、層間絶縁膜11および多結晶シリコン膜5を貫通して金属膜4と接触するように形成されたコンタクトプラグ12と、を備える。

(もっと読む)

半導体装置

【課題】ボンディングする際に、電極パッドの下方に加わるストレスに対しての耐性が強く、且つ配線の配置が容易な半導体装置を提供する。

【解決手段】半導体基板1上に形成された多層配線層2を貫通し半導体基板1に達する支柱5a,5bにより、多層配線層2上に形成される電極パッド4の4隅のうち、少なくとも隣接する2隅を下方から支え、支柱5a,5b間に複数の梁6a,6b,6cを接続し、梁6a,6b間に部材7a,7b,7c,7dを接続する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】抵抗素子の膜厚が薄くても、抵抗素子と上層配線と接続する為のコンタクトホールを形成する際に、コンタクトホールが抵抗素子を突き抜けてしまうことを防止する半導体装置及びその製造方法を提供する。

【解決手段】基板上にゲート絶縁膜4を形成し、ゲート絶縁膜4上に第1の金属膜5、および第2の金属膜6を含む積層膜を形成し、ゲート電極形成領域及び抵抗素子部形成領域に前記積層膜が残るように、パターニングを行う。その後、ゲート電極形成領域及び前記抵抗素子部形成領域に、コンタクトホール形成領域を設定し、コンタクトホール形成予定領域を保護した状態で、抵抗素子形成予定領域の前記第2の金属膜6を除去し、その後に前記積層膜を覆うように層間膜9を形成し、コンタクトホール形成予定領域に形成された前記層間膜9を除去し、前記第2の金属膜6に達するコンタクトホールを形成する工程とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】低コストでメタルキャップ膜が形成された半導体装置及びその製造方法を提供する。

【解決手段】絶縁膜1bに配線溝及び配線孔を形成し、バリアメタル2bを成膜した後、銅層3bを配線溝及び配線孔に埋め込むように形成する。次に、CMP法により表面を平坦化して銅配線層を形成する。この際、CMP用のスラリーに異種金属を有する水溶性金属化合物を添加してCMPを行う。次に、不活性ガス又は還元性ガス雰囲気中で熱処理を行うことにより、銅配線層の表面に、異種金属が添加された銅層9bを形成する。その後、異種金属が添加された銅層9bを覆うようにバリア絶縁膜5bを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜として低誘電率膜のように機械的強度が低い膜を用いた場合であっても配線の集積度が高く且つ信頼性を確保できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上にトランジスタ12等の半導体素子を被覆する第1の層間絶縁膜16を形成した後、ヤング率が低い低誘電率膜からなる下層側層間絶縁膜Aと、シリコン酸化膜等のようにヤング率が高く且つ密着性及び耐湿性が優れた膜からなる上層側層間絶縁膜Bを形成する。電極パッド70の直下域の下層側層間絶縁膜A内にはダミー配線及びダミープラグとともに、半導体素子に電気的に接続された有効配線を配置する。また、電極パッド70の直下域の上層側層間絶縁膜B内にはダミー配線及びダミープラグのみを配置し、電極パッド70に応力が印加されたときに下層側層間絶縁膜Aよりも上層側層間絶縁膜Bに大きな応力が印加されるようにする。

(もっと読む)

半導体装置

【課題】メモリを有するRFIDにおいて、プロセスもしくは回路面積を増大させることなくアンテナの配置を行うことを課題とする。

【解決手段】メモリを中央に配置し、メモリ共通電極を囲むようにアンテナの配線を行う。さらに、メモリ共通電極とアンテナの距離は500μm以上、好ましくは1000μm以上離して配置する。このような構成により、メモリ共通電極とアンテナとを共通の絶縁層上に形成することが可能となり、余剰プロセスを防ぐことができる。

(もっと読む)

集積回路デバイスとその製造方法

【課題】基板と複数のマイクロ電子デバイスを備える集積回路デバイス及びその方法を提供する。

【解決手段】少なくとも一つのマイクロ電子デバイス150に電気的に接触する導電性相互接続部を備える第1の層と、第1の層のラインに対して直角に整列された導電性のラインを備える第2の層であってかつ第2の層のラインが第1の層のラインと電気的に接触している第2の層と、第2の層のラインに対して直角に整列された導電性のラインを備える第3の層であってかつ第3の層のラインが第2の層のラインと電気的に接触している第3の層とを備え、第1の層を第2の層に相互接続し、かつ第3の層を第2の層に相互接続する複数のバイア224等を備える。

(もっと読む)

半導体装置の作製方法およびレーザ加工装置

【課題】半導体装置の製造工程において、フォトレジストを用いたリソグラフィー工程を簡略化する半導体装置の製造技術を提供して、製造コストを低減し、スループットを向上させる。

【解決手段】基板上に第1材料層、第2材料層を順次積層して被照射体を形成する。当該被照射体に、第1材料層に吸収される第1のレーザビームと、第2材料層に吸収される第2のレーザビームを重畳するように照射し、該重畳するようにレーザビームが照射された領域の一部或いは全部をアブレーションさせ、開口を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極を好適な仕事関数を有する導電材料から構成することができ、ゲート電極の構成材料と層間絶縁層のエッチング条件との関係を考慮する必要のない半導体装置を提供する。

【解決手段】NMISFET及びPMISFETを含む半導体装置であって、各ゲート電極32A,32Bは、層間絶縁層の下層部28Aに設けられたゲート電極形成用開口部に埋め込まれており、NMISFETのゲート電極32Aの少なくとも底面部と側面部は第1の導電材料33Aから構成されており、PMISFETのゲート電極32Bの少なくとも底面部と側面部は第1の導電材料とは異なる第2の導電材料33Bから構成されており、各ゲート電極32A,32Bの頂面上には、導電性を有する保護層35A,35Bが形成されており、各ゲート電極用コンタクトプラグ44A,44Bは、保護層35A,35Bを介して、各ゲート電極32A,32Bの頂面に接続されている。

(もっと読む)

電子デバイス及びその製造方法

【課題】 電子デバイス及びその製造方法に関し、カーボンナノチューブの特性を生かすとともに、よりに良好な電気伝導特性をもつ配線構造を提供する。

【解決手段】 カーボンナノチューブ束3の間隙を重合フラーレン6で埋め込んだカーボンベース配線を設ける。

(もっと読む)

炭素ナノチューブ配線の形成方法及びこれを用いる半導体素子配線の形成方法

【課題】界面破壊現象が発生しない炭素ナノチューブ配線の形成方法及びこれを利用した半導体素子配線の形成方法が開示されている。

【解決手段】基板上に酸化金属膜を形成した後、前記酸化金属膜上に前記酸化金属膜の表面を露出させる開口を含む絶縁膜パターンを形成する。前記開口に露出された前記酸化金属膜を炭素ナノチューブの成長が可能な触媒金属膜パターンに形成する。前記触媒金属膜パターンから炭素ナノチューブを成長させて炭素ナノチューブ配線を形成する。前述した炭素ナノチューブ配線の形成方法は、前記絶縁膜パターンと触媒金属膜パターンとの間で炭素ナノチューブが成長する現象を防止することができる。

(もっと読む)

1 - 20 / 42

[ Back to top ]